кода по известной заранее величине ошибки синусно-косинусные сигналы преобразуются в блоКе 1 в систему многофазных сигналов, В зависимости от соотношения амплитуды входных сигналов преобразователя на одном из вькодов дешифратора 2 формируется еди-j ничный сигнал. Значение предыдущего сигнала хранится в регистре 3. В блоках 4 и 5 элементов И сравниваются значения кода текущего сигнала с предыдущим. При изменении на 1 в одну сторону текущего кода по сравнению с предыдущим формируются импульсы на выходе элемента ИЛИ 6, код реверсив- кого счетчика 8 изменяется на 1 в

Изобретение относится к автом ати- ке и вычислительной технике, может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством и является усовершенствованием изобретения по авт.св. № 1094043.

Цель изобретения - повьппение точности преобразователя- путем коррекции величины выходного кода по из- бестной заранее величине ошибки.

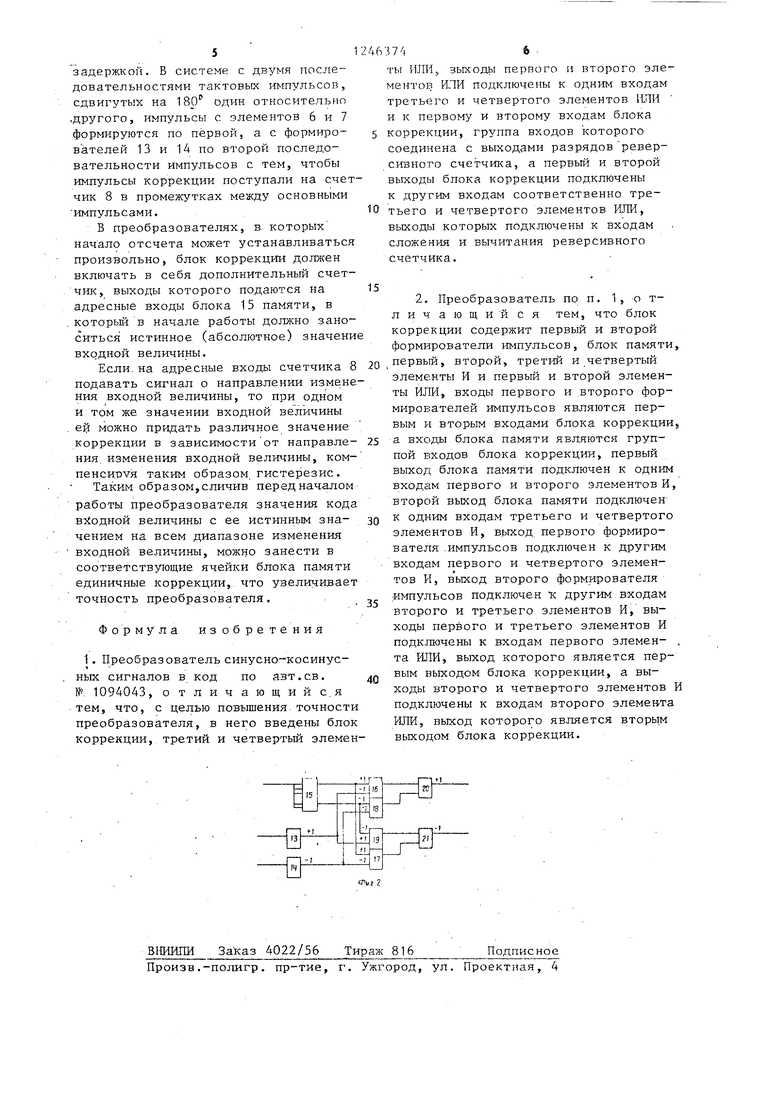

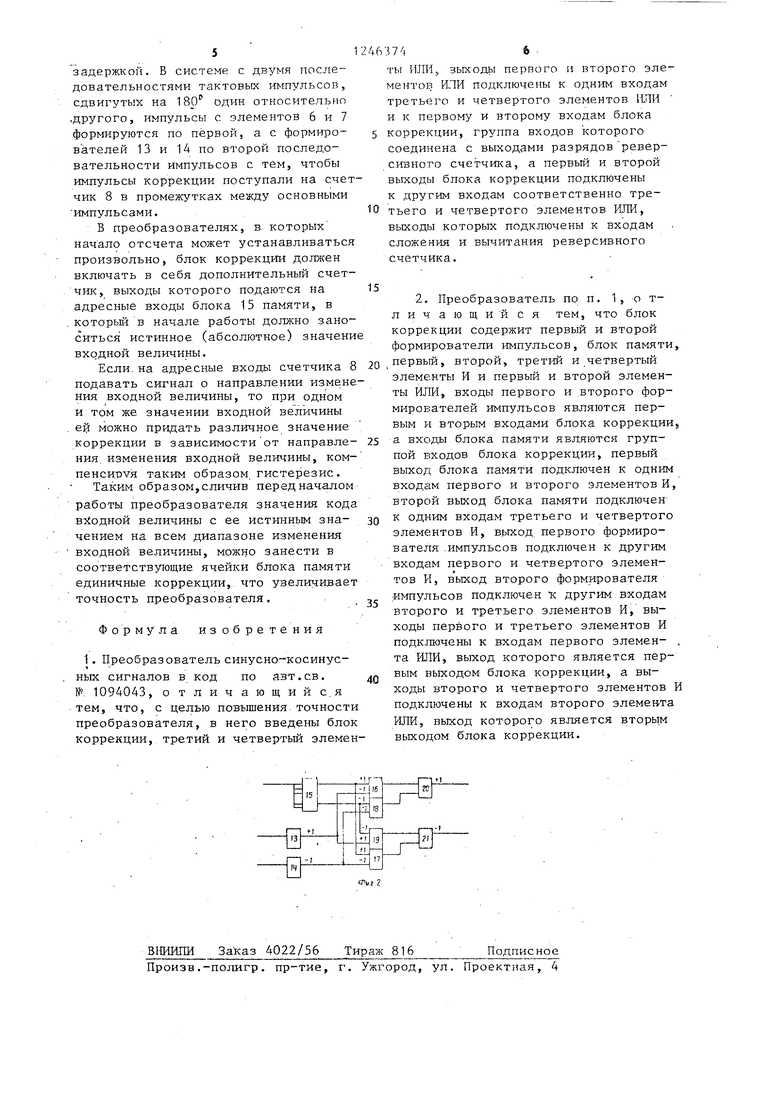

На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 - структурная схема блока коррекции.

Преобразователь содержит блок 1 преобразования синусно-косинусных - ; сигналов в многофазные сигна.пы, выходы которого через дешифратор 2 подключены к информационным входам регистра 3 и к одним группам входов первого 4 и второго 5 блоков элементов И, Д1эугие группы входов которых соединены с выходами разрядов регистра 3, а выходы первого 4 и второго 5 блоков элементов И подключены соответственно к входам первого 6 и второго 7 элементов ИЛИ, реверсивный счетчик В, формирователь 9 импульсбв, входы которого соединены с выходами элементов ИЛИ- 6 и 7, а выход подключен к синхронизирующему входу регистра 3. Выходы элементов ИЛИ 6 и 7 подкЛ1С|чены к первому и второ иу вхо46374

одну сторону, а содержимое дешифратора 2 переписывается в регистр 3 по выходному импульсу формирователя 9. При изменении на 1 в другую сторону текущего кода формируются импульсы . на выходе,элемента ИЛИ 7, .а код реверсивного счетчика 8 изменяется на 1 в другую сторону, и содержимое дешифратора 2 переписывается в.регистр 3. В блоке 10 коррекции хранится код поправки, который в зависимости отвыходного кода реверсивного счетчика 8 инаправления его изменения вводится через элементы ИЛИ 1 1 , 1ШИ 12 на входы сложения или вычитания реверсивного счетчика 8. 1.з .п.ф-лы, 2 ил.

дам блока 10 коррекции, группа вхо-. :дов которого соединена с выходами разрядов реверсивного счетчика 8.- Выход элемента ИЛИ 6 и первый выход 5 блока 10 через элемент ИЛИ 11 подключены к входу сложения реверсивного счетчика 8, а выход элемента РШИ 7 .и второй выход блока 10 через элемент ИЛИ 12 - к входу вычитания ре0 версивного счетчика 8.

Блок 10 коррекции содержит форми- .рователи 13 и 14 импульсов, блок 15 памятиj первый 16, второй 17, третий 18 и четвертый 19 элементы И, первый

5 20 и второй 21 элементы ИЛИ. Входы формирователей 13 и 14 импульсов являются первым и вторым входами блока 10 кйррекции, .а входы блока 15 памяти - группой входов блока 10

0 коррекции. Первый выход блока 15 памяти подключен к одним входам элементов И i6 и 17, второй выход блока 15 - к одним входам элементов-И 18 и 19. Выход формирователя 13 под5 ключен к другим входам элементов

И 16 и 19, а выход формирователя 14- к другим входам элементов И 17 и 18. Выходы элементов И 16 и t8 подключены к входам элемента ИЛИ 20, выход .

0 которого является первым выходом блока 10 коррекции, а выходы элементов И 17 и 19 подключены к входам элемента ИЛИ 21, который является вторым выходом блока 10 коррекции.

Преобразователь работает следуюим образом.

В блоке 1 входные синусно-косинус- ные сигналы преобразуются в прямоугольные многофазные сигналы, число s которых определяется принятой дискретностью преобразователя. В дешифраторе 2 многофазные сигналы преобразуются в последовательности неперекрывающихся импульсов, которые Q

поступают на входы блоков 4 и 5 элементов И и на информационные входы регистра 3.

В любой момент времени сигнал на выходе дешифратора 2 представляет 15 собой 1 на одном из выходов и О на всех остальных выходах. По сигналу с формирователя 9 состояние де- шифратора 2 запоминается в регистре 3. Коды дешифратора 2 и регистра 20

3сравниваются в блоках 4 и 5. При равенстве выходных кодов дешифратора 2 и регистра 3 все выходы блоков

4и 5 находятся в нулевом состоянии. При изменении входной величины в 25 одну сторону выходной код дешифратора 2 последовательно принимает значения, например, 1000, 0100, 0010

и т. д,

При -каждом изменении выходного зо кода дешифратора 2 происходит совпадение на одном из элементов И блока 4 единицы кода предьщущего значения с регистра 3 с единицей кода текущего значения с дешифратора. 2. Единичный . сигнал с выхода блока 4 через элемен- ты РШИ 6 и 11 проходит ра вход сложения реверсивного счетчика 8 и через формирователь 9, представляющий собой элемент ИЛИ и элемент задержки, пос- тупает на управляющий вход регистра 3. По сигналу с формирователя 9 в регистре 3 происходит перезапись выходного кода дешифратора 2, после чего выходные коды дешифратора 2 и регистра 3 ,с становятся равными. Выходы блока 4 возвращаются в нулевое состояние до следующего изменения входной величины в ту же сторону.

При изменении входной величины в 50 другую сторону выходной код дешифратора 2 принимает значения, наприер, 1000, 0001, 0010,0100 и т.д. При каждом изменении выходного кода дешифратора 2-происходит совпадение 55 на одном из элементов И блока 5 еди- ницы кода предыдущего значения с регистра 3 с единицей кода текущего

35

s Q

15 20

25

зо ,с

0 5

5

значения с дешифратора 2. Единичный сигнал с выхода блока 5 через элементы ИЛИ 7 и 12 проходит на вход вычитания реверсивного счетчика 8 и через формирователь 9 на управляющий вход регистра 3 для перезаписи выходного кода дешифратора 2. Выходы 5 возвращаются в нулевое состояние до следующего изменения входной величины. Выходной код преобразователя формируется в реверсивном счетчике 8.

Выходной код счетчика 8 для форми- рования в. заданных точках едишсчных сигналов коррекции поступает на пер-, вые входы блока 10 коррекции. Еди- . ничные сигналы с блоков 4 и 5 через элементы ИЛИ 6 и 7 соответственно поступают на первый и второй входы блока 10 коррекции, с которого в промежутках между единичными сигналами с блоков 4 и 5 поступают единичные сигналы коррекции через элементы ИЛИ 11 и 12 на соответствующие входы реверсивного счетчика 8.

В каждой ячейке блока 15 записан код коррекции 10 либо 01, либо 00. Это значит, что, когда код реверсивного счетчика примет значение, соответствующее адресу ячейки, в которой записан, например код 10, то при этом значении входной величины и росте ее в счетчик 8 необходимо внести коррекцию +1, при убывании входной величи- . ны необходимо внести коррекцию -1. Если код в ячейке равен 01, то при возрастании входной-величины в счетчик необходимо внести коррекцию -1, а при убывании +1, Код 00 означает отсутствие коррекции в данной точке.

На адресные шины блока 15 младшие разряды реверсивного счетчика 8 могут не подаваться. Число этих разрядов определяется минимальной длиной участка, на котором требуется единичное значение коррекции.

С помощью элементов И 16-19 код коррекции, записанньй в ячейке блока 15, передается на суммирующий или вычитающий вход реверсивного счетчика 8 в зависимости от направления ; изменения входной величины.

Формирователи 13 и 14 импульсов вырабатывают после каждого из импуль- сов, поступающих с элементов ИЛИ 6 и 7, импульсы коррекции.

В нетактированной системе эти импульсы формируются по срезу импульсов с элементов 6 и 7 с некоторой

задержкой. В системе с двумя последовательностями тактовых импульсов, сдвигутых на 180 один относительно .другого, импульсы с элементов 6 и 7 формируются по первой, а с формирователей 13 и 14 по второй последовательности импульсов с тем, чтобы импульсы коррекции поступали на счетчик 8 в промежутках между основными импульсами.

В преобразователях, в которых начало отсчета может устанавливаться произвольно, блок коррекции должен включать в себя дополнительный счетчик, выходы которого подаются на

адресные входы блока 15 памяти, в который в начале работы должно заноситься истинное (абсолютное) значени входной величины.

Если.на адресные входы счетчика 8 подавать сигнал о направлении изменения входной величины, то при одном и том же значении входной величины ей можно придать различное значение коррекции в зависимости от направле- ния. изменения входной величины, ком- пенси.руя таким образом гистерезис. Таким образом,сличив передначалом

работы преобразователя значения кода в; одной величины с ее истинным зна- чением на всем диапазоне изменения входной величины, можно занести в соответствующие ячейки блока памяти единичные коррекции, что увеличивает точность преобразователя.

Формула изобретения

1. Преобразователь синусно-косинус- ных сигналов в код по азт.св.

№. 1094043, отличающий с.я тем, что, с целью повышения точности преобразователя, в него введены блок коррекции, третий и четвертый элемен

10

37 А6

ты ИЛИ, зькодь первого и второго элементов ИЛИ подключень к одним входам третьего и четвертого элементов ШИ и к первому и второму входам блока коррекции, группа входов которого соединена с выходами разрядов реверсивного счетчика, а первый и второй выходы блока коррекции подключены к другим входам соответственно третьего и четвертого элементов ИЛИ, выходы которых подключены к входам сложения и вычитания реверсивного счетчика.

2, Преобразователь по п. 1, о т- ли чающийся тем, что блок коррекции содержит первый и второй формирователи импульсов, блок памяти, первый, второй, третий и четвертый элементы И и первый и второй элементы ИЛИ, входы первого и второго формирователей импульсов являются первым и вторым входами блока коррекции, а входы блока памяти являются группой входов блока коррекции, первый выход блока памяти подключен к одним входам первого и второго элементов И, второй выход блока памяти подключен к одним входам третьего и четвертого элементов И, вьгход. первого формирователя .импульсов подключен к другим входам первого и четвертого элементов И, выход второго формирователя импульсов подключен тс другим входам второго и третьего элементов И, выходы первого и третьего элементов И подключены к входам первого элемен- . та ИЛИ, выход которого является первым выходом блока коррекции, а выходы второго и четвертого элементов И подключены к входам второго элемента ИЛИ, вькод которого является вторым выходом блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синусно-косинусных сигналов в код | 1982 |

|

SU1094043A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1262730A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для управления меткой на экране индикатора | 1983 |

|

SU1160451A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для кодирования сигналов частотных датчиков | 1987 |

|

SU1564728A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повьшения точности преобразователя путем коррекции величины выходного ,1пФ Cosf (Л

В1МИПИ 4022/56 Тираж 816

Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул, Проектная, 4

Подписное

| Преобразователь синусно-косинусных сигналов в код | 1982 |

|

SU1094043A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-07-23—Публикация

1985-01-10—Подача