Изобретение относится к контрольно- измерительной технике и может быть использовано для автоматического контроля гальванических соединений.

Цель изобретения - упрощение за счет сокращения числа разрядов блока постоянной памяти и блока сравнения, расширение функциональных возможностей и повышение достоверности контроля за счет обеспечения возможности контроля сопротивлений цепей и их участков.;

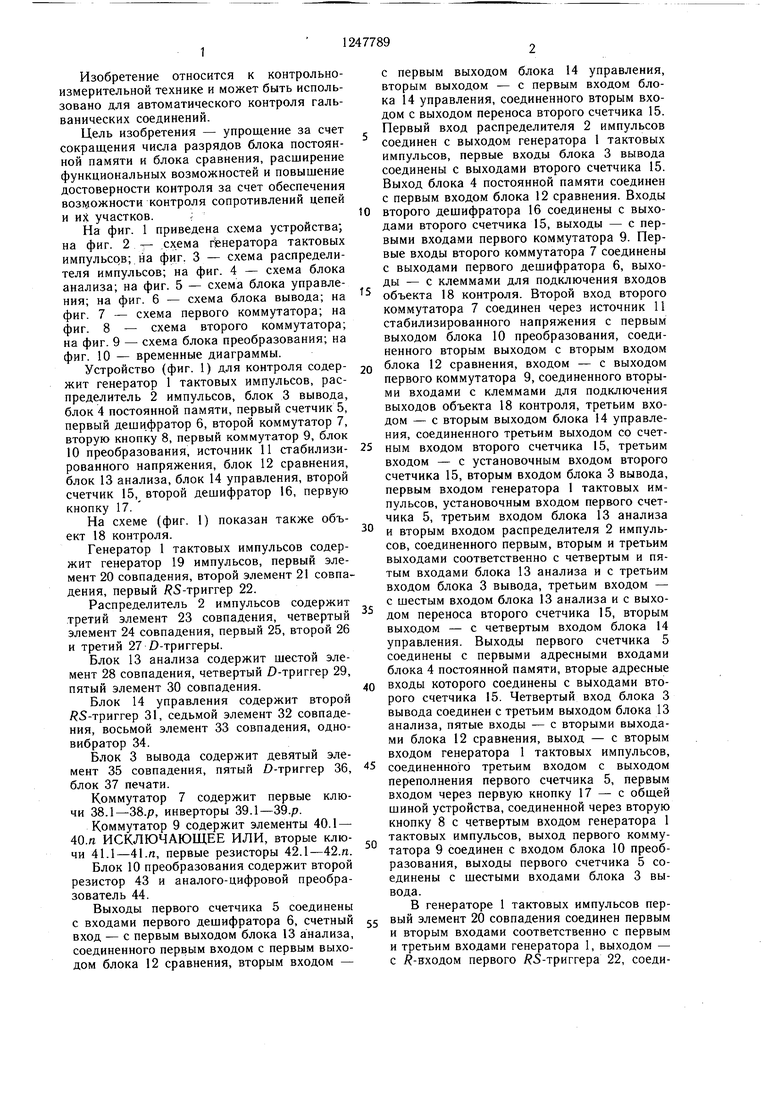

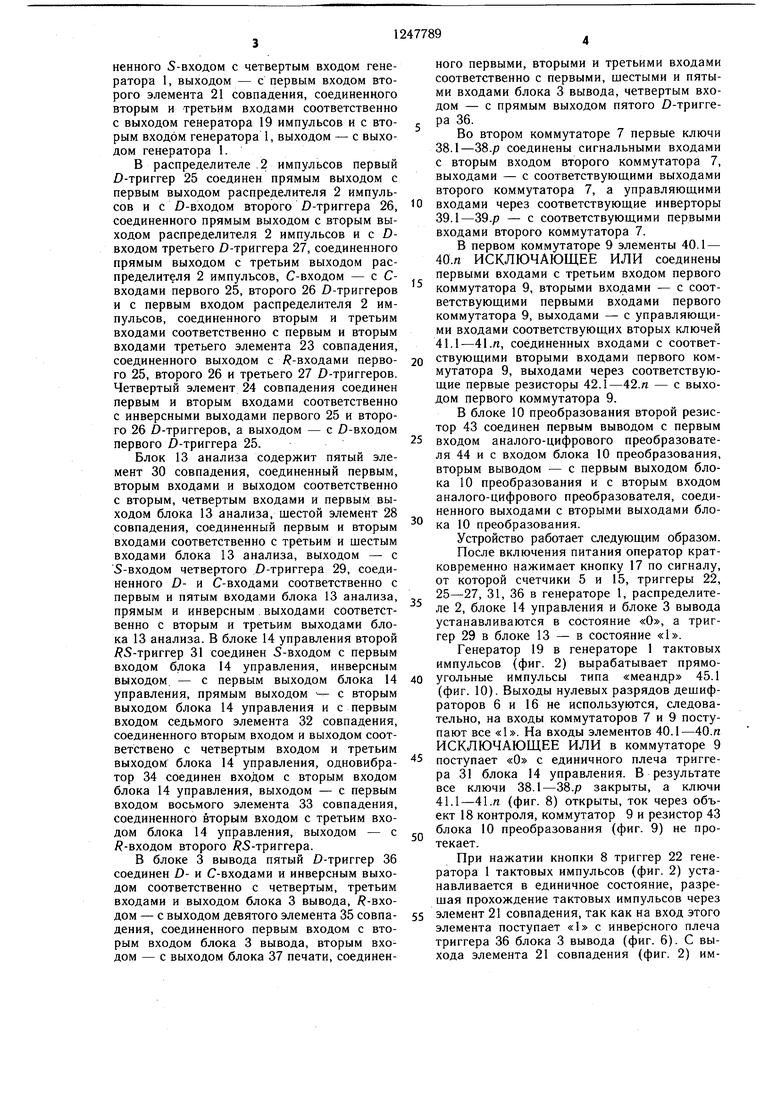

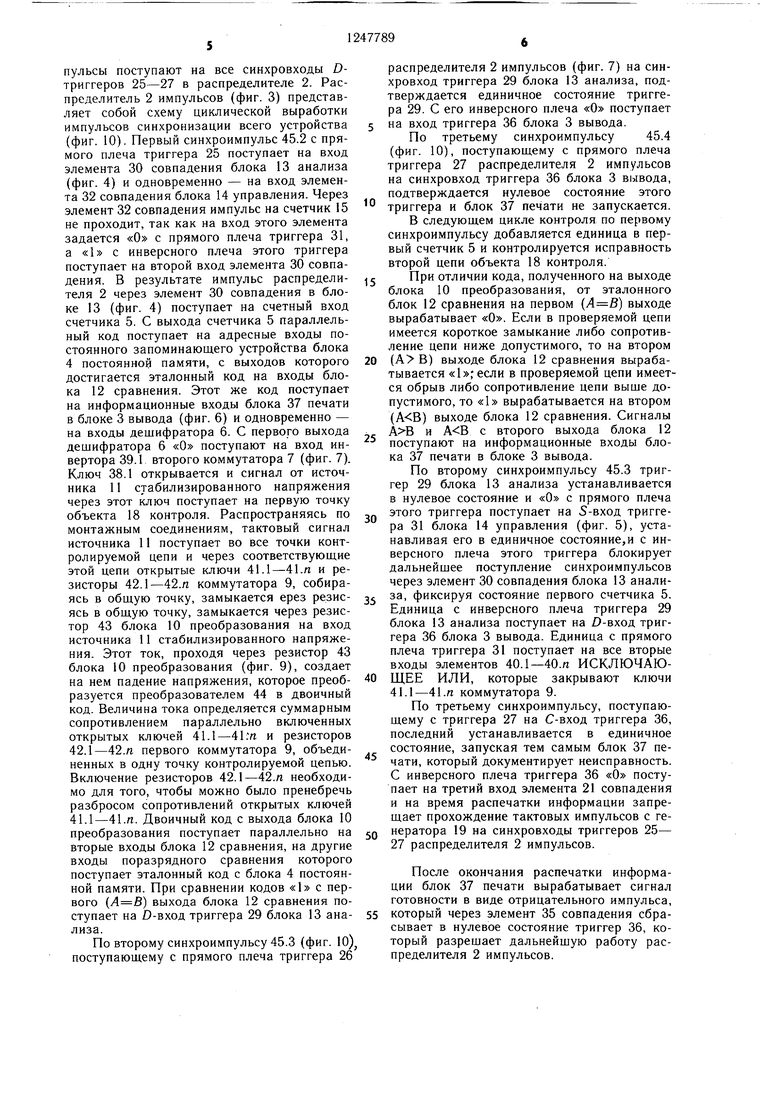

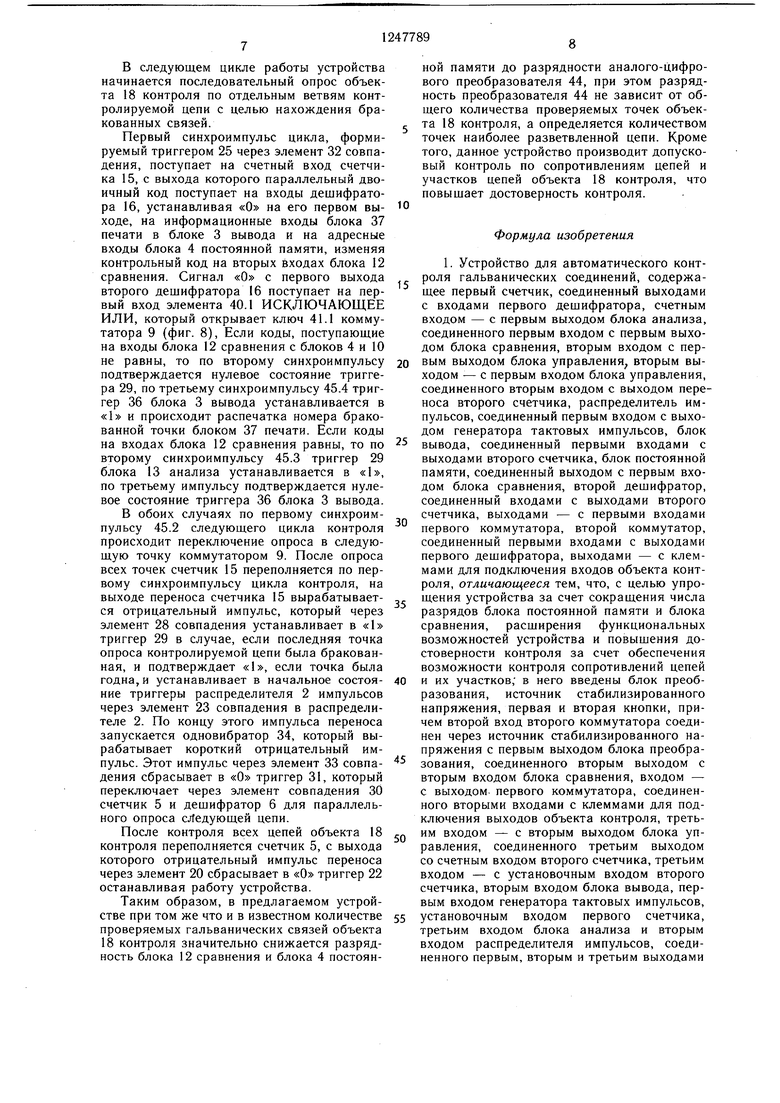

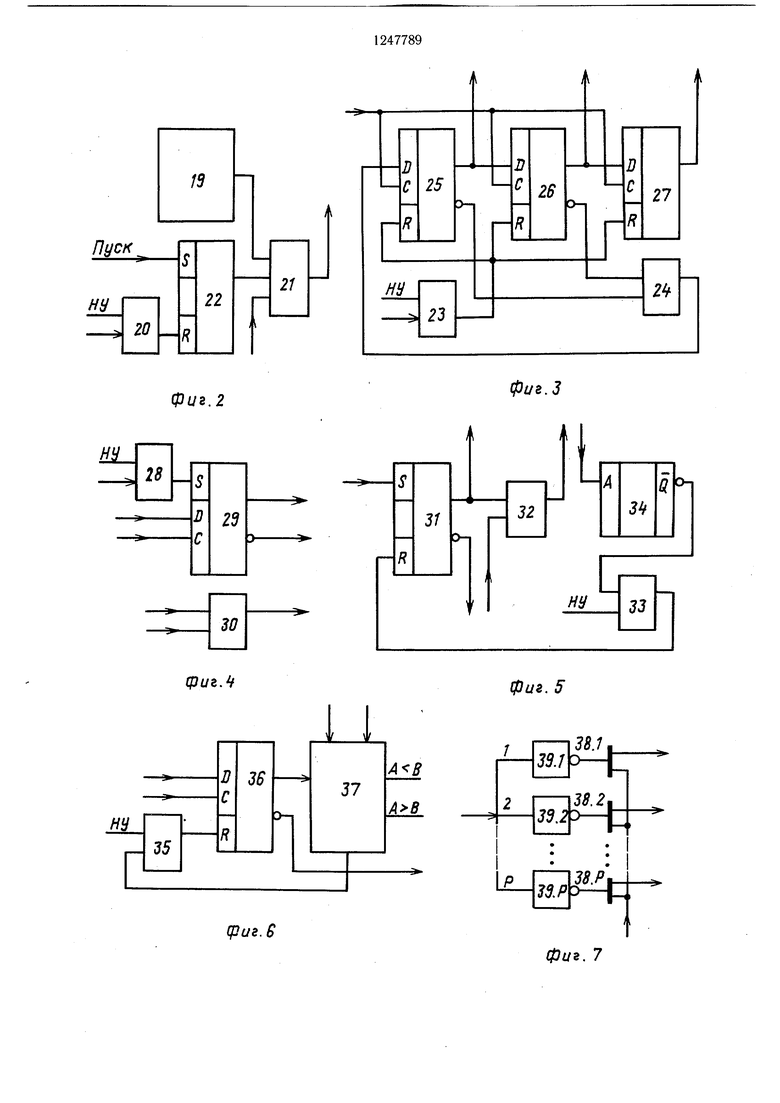

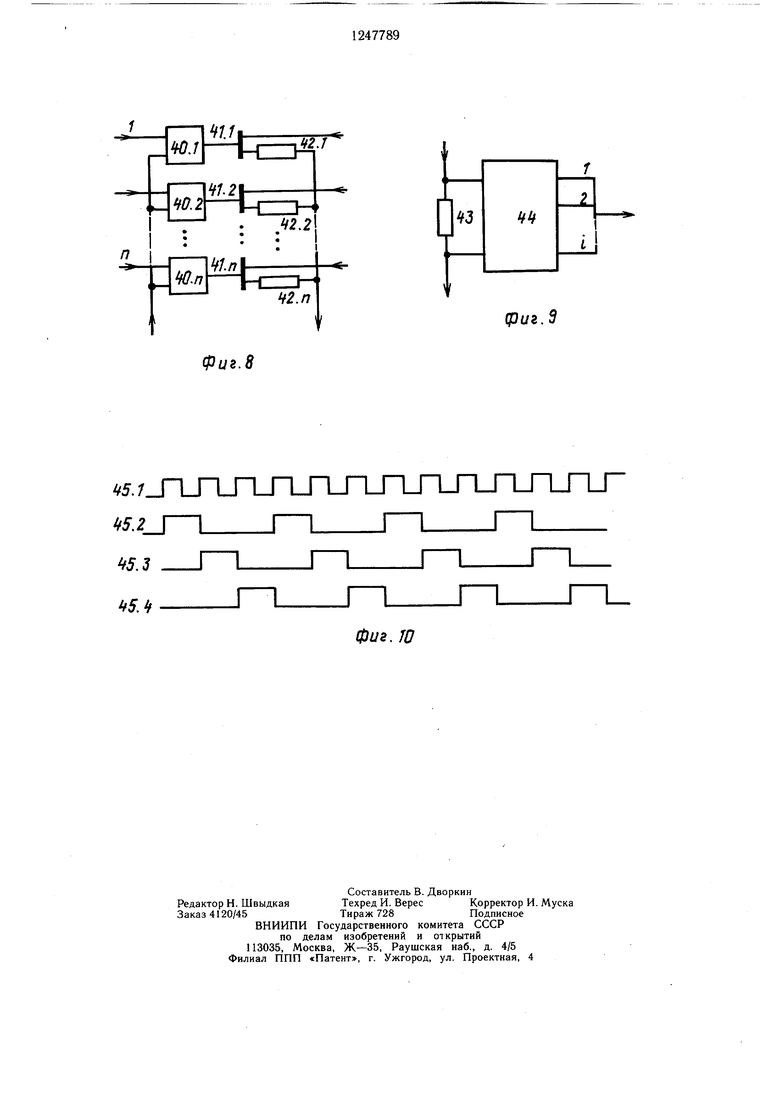

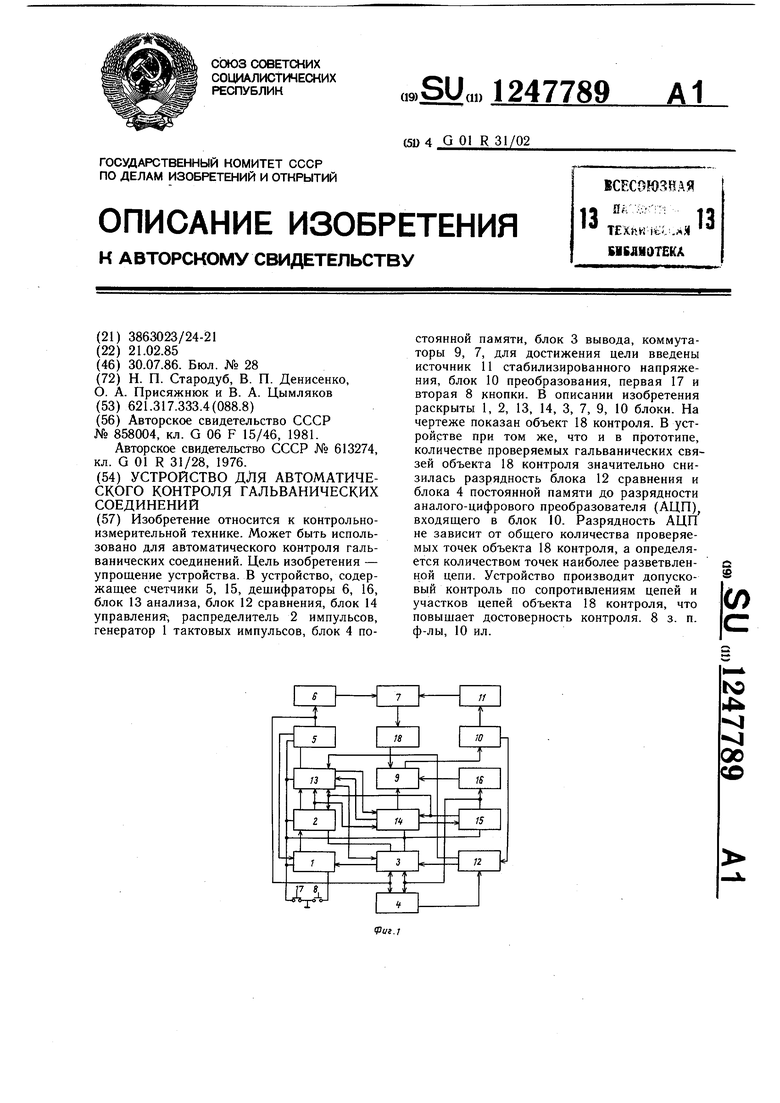

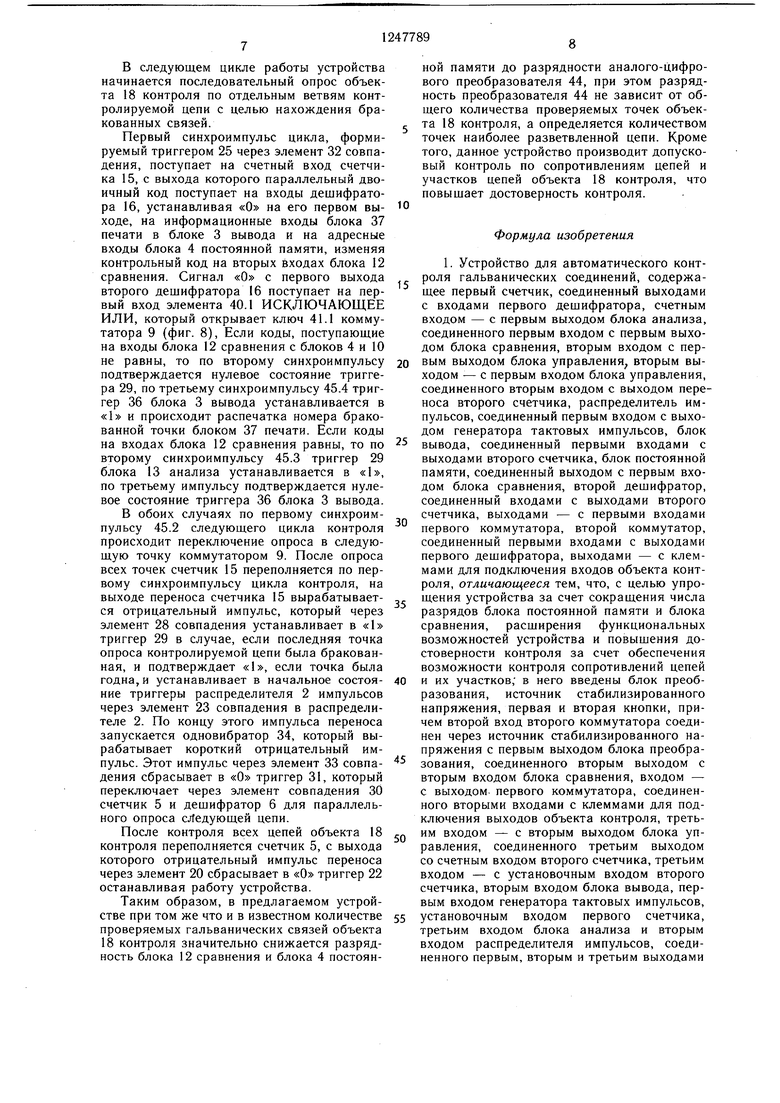

На фиг. 1 приведена схема устройства; на фиг. 2 т- схема генератора тактовых импульсов; на фиг. 3 - схема распределителя импульсов; на фиг. 4 - схема блока анализа; на фиг. 5 - схема блока управления; на фиг. 6 - схема блока вывода; на фиг. 7 - схема первого коммутатора; на фиг. 8 - схема второго коммутатора; на фиг. 9 - схема блока преобразования; на фиг. 10 - временные диаграммы.

Устройство (фиг. 1) для контроля содержит генератор 1 тактовых импульсов, распределитель 2 импульсов, блок 3 вывода, блок 4 постоянной памяти, первый счетчик 5, первый дешифратор 6, второй коммутатор 7, вторую кнопку 8, первый коммутатор 9, блок 10 преобразования, источник 11 стабилизированного напряжения, блок 12 сравнения, блок 13 анализа,блок 14 управления, второй счетчик 15, второй дешифратор 16, первую кнопку 17.

На схеме (фиг. 1) показан также объект 18 контроля.

Генератор 1 тактовых импульсов содержит генератор 19 импульсов, первый элемент 20 совпадения, второй элемент 21 совпадения, первый / 5-триггер 22.

Распределитель 2 импульсов содержит третий элемент 23 совпадения, четвертый элемент 24 совпадения, первый 25, второй 26 и третий 27 D-триггеры.

Блок 13 анализа содержит шестой элемент 28 совпадения, четвертый D-триггер 29, пятый элемент 30 совпадения.

Блок 14 управления содержит второй / 5-триггер 31, седьмой элемент 32 совпадения, восьмой элемент 33 совпадения, одно- вибратор 34.

Блок 3 вывода содержит девятый элемент 35 совпадения, пятый D-триггер 36, блок 37 печати.

Коммутатор 7 содержит первые ключи 38.1-З8.р, инверторы 39.1-З9.р.

Коммутатор 9 содержит элементы 40.1 - 40./г ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые ключи 41.1-41./г, первые резисторы 42.1-42.п.

Блок 10 преобразования содержит второй резистор 43 и аналого-цифровой преобразователь 44.

Выходы первого счетчика 5 соединены с входами первого дешифратора 6, счетный вход - с первым выходом блока 13 анализа, соединенного первым входом с первым выходом блока 12 сравнения, вторым входом -

с первым выходом блока 14 управления, вторым выходом - с первым входом блока 14 управления, соединенного вторым входом с выходом переноса второго счетчика 15. Первый вход распределителя 2 импульсов соединен с выходом генератора 1 тактовых импульсов, первые входы блока 3 вывода соединены с выходами второго счетчика 15. Выход блока 4 постоянной памяти соединен с первым входом блока 12 сравнения. Входы

0 второго дешифратора 16 соединены с выходами второго счетчика 15, выходы - с первыми входами первого коммутатора 9. Первые входы второго коммутатора 7 соединены с выходами первого дешифратора 6, выходы - с клеммами для подключения входов

объекта 18 контроля. Второй вход второго коммутатора 7 соединен через источник 11 стабилизированного напряжения с первым выходом блока 10 преобразования, соединенного вторым выходом с вторым входом

0 блока 12 сравнения, входом - с выходом первого коммутатора 9, соединенного вторыми входами с клеммами для подключения выходов объекта 18 контроля, третьим входом - с вторым выходом блока 14 управления, соединенного третьим выходом со счет5 ным входом второго счетчика 15, третьим входом - с установочным входом второго счетчика 15, вторым входом блока 3 вывода, первым входом генератора 1 тактовых импульсов, установочным входом первого счетчика 5, третьим входом блока 13 анализа

и вторым входом распределителя 2 импульсов, соединенного первым, вторым и третьим выходами соответственно с четвертым и пятым входами блока 13 анализа и с третьим входом блока 3 вывода, третьим входом - с шестым входом блока 13 анализа и с выхо- дом переноса второго счетчика 15, вторым выходом - с четвертым входом блока 14 управления. Выходы первого счетчика 5 соединены с первыми адресными входами блока 4 постоянной памяти, вторые адресные

входы которого соединены с выходами второго счетчика 15. Четвертый вход блока 3 вывода соединен с третьим выходом блока 13 анализа, пятые входы - с вторыми выходами блока 12 сравнения, выход - с вторым входом генератора 1 тактовых импульсов, соединенного третьим входом с выходом переполнения первого счетчика 5, первым входом через первую кнопку 17 - с общей шиной устройства, соединенной через вторую кнопку 8 с четвертым входом генератора 1 тактовых импульсов, выход первого коммутатора 9 соединен с входом блока 10 преобразования, выходы первого счетчика 5 соединены с шестыми входами блока 3 вывода.

В генераторе 1 тактовых импульсов пер5 вый элемент 20 совпадения соединен первым и вторым входами соответственно с первым и третьим входами генератора 1, выходом - с / -нходом первого 5-триггера 22, соеди5

ненного S-входом с четвертым входом генератора 1, выходом - с первым входом второго элемента 21 совпадения, соединенного вторым и третьим входами соответственно с выходом генератора 19 импульсов и с вторым входом генератора 1, выходом - с выходом генератора 1.

В распределителе .2 импульсов первый /)-триггер 25 соединен прямым выходом с первым выходом распределителя 2 импульсов и с D-входом второго D-триггера 26, соединенного прямым выходом с вторым выходом распределителя 2 импульсов к с D- входом третьего D-триггера 27, соединенного прямым выходом с третьим выходом распределителя 2 импульсов, С-входом - с С- входами первого 25, второго 26 )-триггеров и с первым входом распределителя 2 импульсов, соединенного вторым и третьим входами соответственно с первым и вторым входами третьего элемента 23 совпадения, соединенного выходом с / -входами первого 25, второго 26 и третьего 27 О-триггеров. Четвертый элемент 24 совпадения соединен первым и вторым входами соответственно с инверсными выходами первого 25 и второго 26 D-триггеров, а выходом - с )-входом первого )-триггера 25.

Блок 13 анализа содержит пятый элемент 30 совпадения, соединенный первым, вторым входами и выходом соответственно с вторым, четвертым входами и первым выходом блока 13 анализа, шестой элемент 28 совпадения, соединенный первым и вторым входами соответственно с третьим и шестым входами блока 13 анализа, выходом - с S-входом четвертого D-триггера 29, соединенного D- и С-входами соответственно с первым и пятым входами блока 13 анализа, прямым и инверсным . выходами соответственно с вторым и третьим выходами блока 13 анализа. В блоке 14 управления второй / 5-триггер 31 соединен S-входом с первым входом блока 14 управления, инверсным выходом. - с первым выходом блока 14 управления, прямым выходом -- с вторым выходом блока 14 управления и с первым входом седьмого элемента 32 совпадения, соединенного вторым входом и выходом соот- ветствено с четвертым входом и третьим выходом блока 14 управления, одновибра- тор 34 соединен входом с вторым входом блока 14 управления, выходом - с первым входом восьмого элемента 33 совпадения, соединенного вторым входом с третьим входом блока 14 управления, выходом - с / -входом второго S-триггера.

В блоке 3 вывода пятый О-триггер 36 соединен D- и С-входами и инверсным выходом соответственно с четвертым, третьим входами и выходом блока 3 вывода, / -вхо- дом - с выходом девятого элемента 35 совпадения, соединенного первым входом с вторым входом блока 3 вывода, вторым входом - с выходом блока 37 печати, соединенного первыми, вторыми и третьими входами соответственно с первыми, шестыми и пятыми входами блока 3 вывода, четвертым входом - с прямым выходом пятого /)-тригге- ра 36.

Во втором коммутаторе 7 первые ключи 38.1-З8.р соединены сигнальными входами с вторым входом второго коммутатора 7, выходами - с соответствуюш,ими выходами второго коммутатора 7, а управляюшими

0 входами через соответствуюшие инверторы 39.1-39.р - с соответствуюш.ими первыми входами второго коммутатора 7.

В первом коммутаторе 9 элементы 40.1 - 4а.п ИСКЛЮЧАЮЩЕЕ ИЛИ соединены первыми входами с третьим входом первого

коммутатора 9, вторыми входами - с соответствуюш.ими первыми входами первого коммутатора 9, выходами - с управляюш,и- ми входами соответствуюш,их вторых ключей 41.1-41.и, соединенных входами с соответQ ствуюш.ими вторыми входами первого коммутатора 9, выходами через соответствую- ш,ие первые резисторы 42.1-42.л - с выходом первого коммутатора 9.

В блоке 10 преобразования второй резистор 43 соединен первым выводом с первым

5 входом аналого-цифрового преобразователя 44 и с входом блока 10 преобразования, вторым выводом - с первым выходом блока 10 преобразования и с вторым входом аналого-цифрового преобразователя, соединенного выходами с вторыми выходами бло ка 10 преобразования.

Устройство работает следующим образом. После включения питания оператор кратковременно нажимает кнопку 17 по сигналу, от которой счетчики 5 и 15, триггеры 22, 25-27, 31, 36 в генераторе 1, распределителе 2, блоке 14 управления и блоке 3 вывода устанавливаются в состояние «О, а триггер 29 в блоке 13 - в состояние «1.

Генератор 19 в генераторе 1 тактовых импульсов (фиг. 2) вырабатывает прямо0 угольные импульсы типа «меандр 45.1 (фиг. 10). Выходы нулевых разрядов дешифраторов 6 и 16 не используются, следовательно, на входы коммутаторов 7 и 9 поступают все «1. На входы элементов 40.1-40.п ИСКЛЮЧАЮЩЕЕ ИЛИ в коммутаторе 9

5 поступает «О с единичного плеча триггера 31 блока 14 управления. В результате все ключи 38.1-З8.р закрыты, а ключи 41.1-41.П (фиг. 8) открыты, ток через объект 18 контроля, коммутатор 9 и резистор 43 блока 10 преобразования (фиг. 9) не протекает.

При нажатии кнопки 8 триггер 22 генератора 1 тактовых импульсов (фиг. 2) устанавливается в единичное состояние, разрешая прохождение тактовых импульсов через

5 элемент 21 совпадения, так как на вход этого элемента поступает «1 с инверсного плеча триггера 36 блока 3 вывода (фиг. 6). С выхода элемента 21 совпадения (фиг. 2) им0

пульсы поступают на все синхровходы D- триггеров 25-27 в распределителе 2. Распределитель 2 импульсов (фиг. 3) представляет собой схему циклической выработки импульсов синхронизации всего устройства (фиг. 10). Первый синхроимпульс 45.2 с прямого плеча триггера 25 поступает на вход элемента 30 совпадения блока 13 анализа (фиг. 4) и одновременно - на вход элемента 32 совпадения блока 14 управления. Через элемент 32 совпадения импульс на счетчик 15 не проходит, так как на вход этого элемента задается «О с прямого плеча триггера 31, а «1 с инверсного плеча этого триггера поступает на второй вход элемента 30 совпадения. В результате импульс распредели- теля 2 через элемент 30 совпадения в блоке 13 (фиг. 4) поступает на счетный вход счетчика 5. С выхода счетчика 5 параллельный код поступает на адресные входы постоянного запоминающего устройства блока 4 постоянной памяти, с выходов которого достигается эталонный код на входы блока 12 сравнения. Этот же код поступает на информационные входы блока 37 печати в блоке 3 вывода (фиг. 6) и одновременно - на входы дешифратора 6. С первого выхода дешифратора 6 «О поступают на вход инвертора 39.1 второго коммутатора 7 (фиг. 7). Ключ 38.1 открывается и сигнал от источника 11 С7абилизированного напряжения через этот ключ поступает на первую точку объекта 18 контроля. Распространяясь по монтажным соединениям, тактовый сигнал источника 11 поступает во все точки контролируемой цепи и через соответствуюшие этой цепи открытые ключи 41.1-41.п и резисторы 42.1-42.л коммутатора 9, собираясь в общую точку, замыкается ерез резис- ясь в общую точку, замыкается через резистор 43 блока 10 преобразования на вход источника 11 стабилизированного напряжения. Этот ток, проходя через резистор 43 блока 10 преобразования (фиг. 9), создает на нем падение напряжения, которое преоб- разуется преобразователем 44 в двоичный код. Величина тока определяется суммарным сопротивлением параллельно включенных открытых ключей 41.1-41. п и резисторов 42.1-42.л первого коммутатора 9, объединенных в одну точку контролируемой цепью. Включение резисторов 42.1-42.п необходимо для того, чтобы можно было пренебречь разбросом сопротивлений открытых ключей 41.1-41.п. Двоичный код с выхода блока 10 преобразования поступает параллельно на вторые входы блока 12 сравнения, на другие входы поразрядного сравнения которого поступает эталонный код с блока 4 постоянной памяти. При сравнении кодов «1 с первого () выхода блока 12 сравнения поступает на D-вход триггера 29 блока 13 ана- лиза.

По второму синхроимпульсу 45.3 (фиг. 10) :тупающему с прямого плеча триггера 26

поступающему с прямого

распределителя 2 импульсов (фиг. 7) на син- хровход триггера 29 блока 13 анализа, подтверждается единичное состояние триггера 29. С его инверсного плеча «О поступает на вход триггера 36 блока 3 вывода.

По третьему синхроимпульсу 45.4 (фиг. 10), поступающему с прямого плеча триггера 27 распределителя 2 импульсов на синхровход триггера 36 блока 3 вывода, подтверждается нулевое состояние этого триггера и блок 37 печати не запускается.

В следующем цикле контроля по первому синхроимпульсу добавляется единица в первый счетчик 5 и контролируется исправность второй цепи объекта 18 контроля.

При отличии кода, полученного на выходе блока 10 преобразования, от эталонного блок 12 сравнения на первом () выходе вырабатывает «О. Если в проверяемой цепи имеется короткое замыкание либо сопротивление цепи ниже допустимого, то на втором (А В) выходе блока 12 сравнения вырабатывается «1 гесли в проверяемой цепи имеется обрыв либо сопротивление цепи выще допустимого, то «1 вырабатывается на втором () выходе блока 12 сравнения. Сигналы и с второго выхода блока 12 поступают на информационные входы блока 37 печати в блоке 3 вывода.

По второму синхроимпульсу 45.3 триггер 29 блока 13 анализа устанавливается в нулевое состояние и «О с прямого плеча этого триггера поступает на S-вход триггера 31 блока 14 управления (фиг. 5), устанавливая его в единичное состояние,и с инверсного плеча этого триггера блокирует дальнейшее поступление синхроимпульсов через элемент 30 совпадения блока 13 анализа, фиксируя состояние первого счетчика 5. Единица с инверсного плеча триггера 29 блока 13 анализа поступает на )-вход триггера 36 блока 3 вывода. Единица с прямого плеча триггера 31 поступает на все вторые входы элементов 40.1-40.п ИСКЛЮЧАЮЩЕЕ ИЛИ, которые закрывают ключи 41.1-41.П коммутатора 9.

По третьему синхроимпульсу, поступающему с триггера 27 на С-вход триггера 36, последний устанавливается в единичное состояние, запуская тем самым блок 37 печати, который документирует неисправность. С инверсного плеча триггера 36 «О поступает на третий вход элемента 21 совпадения и на время распечатки информации запрещает прохождение тактовых импульсов с генератора 19 на синхровходы триггеров 25- 27 распределителя 2 импульсов.

После окончания распечатки информации блок 37 печати вырабатывает сигнал готовности в виде отрицательного импульса, который через элемент 35 совпадения сбрасывает в нулевое состояние триггер 36, который разрешает дальнейшую работу распределителя 2 импульсов.

В следующем цикле работы устройства начинается последовательный опрос объекта 18 контроля по отдельным ветвям контролируемой цепи с целью нахождения бракованных связей.

Первый синхроимпульс цикла, формируемый триггером 25 через элемент 32 совпадения, поступает на счетный вход счетчика 15, с выхода которого параллельный двоичный код поступает на входы дешифратора 16, устанавливая «О на его первом вы- ходе, на информационные входы блока 37 печати в блоке 3 вывода и на адресные входы блока 4 постоянной памяти, изменяя контрольный код на вторых входах блока 12 сравнения. Сигнал «О с первого выхода второго дешифратора 16 поступает на первый вход элемента 40.1 ИСКЛЮЧАЮЩЕЕ ИЛИ, который открывает ключ 41.1 коммутатора 9 (фиг. 8), Если коды, поступающие на входы блока 12 сравнения с блоков 4 и 10 не равны, то по второму синхроимпульсу подтверждается нулевое состояние триггера 29, по третьему синхроимпульсу 45.4 триггер 36 блока 3 вывода устанавливается в «1 и происходит распечатка номера бракованной точки блоком 37 печати. Если коды на входах блока 12 сравнения равны, то по второму синхроимпульсу 45.3 триггер 29 блока 13 анализа устанавливается в «1, по третьему импульсу подтверждается нулевое состояние триггера 36 блока 3 вывода.

В обоих случаях по первому синхроимпульсу 45.2 следующего цикла контроля происходит переключение опроса в следующую точку коммутатором 9. После опроса всех точек счетчик 15 переполняется по первому синхроимпульсу цикла контроля, на выходе переноса счетчика 15 вырабатывается отрицательный импульс, который через элемент 28 совпадения устанавливает в «1 триггер 29 в случае, если последняя точка опроса контролируемой цепи была бракованная, и подтверждает «1, если точка была годна,и устанавливает в начальное состоя- ние триггеры распределителя 2 импульсов через элемент 23 совпадения в распределителе 2. По концу этого импульса переноса запускается одновибратор 34, который вырабатывает короткий отрицательный импульс. Этот импульс через элемент 33 совпадения сбрасывает в «О триггер 31, который переключает через элемент совпадения ЗО счетчик 5 и дешифратор 6 для параллельного опроса следующей цепи.

После контроля всех цепей объекта 18 контроля переполняется счетчик 5, с выхода которого отрицательный импульс переноса через элемент 20 сбрасывает в «О триггер 22 останавливая работу устройства.

Таким образом, в предлагаемом устройстве при том же что и в известном количестве проверяемых гальванических связей объекта 18 контроля значительно снижается разрядность блока 12 сравнения и блока 4 постоян

ной памяти до разрядности аналого-цифрового преобразователя 44, при этом разрядность преобразователя 44 не зависит от общего количества проверяемых точек объекта 18 контроля, а определяется количеством точек наиболее разветвленной цепи. Кроме того, данное устройство производит допуско- вый контроль по сопротивлениям цепей и участков цепей объекта 18 контроля, что повышает достоверность контроля.

Формула изобретения

1. Устройство для автоматического контроля гальванических соединений, содержащее первый счетчик, соединенный выходами с входами первого дешифратора, счетным входом - с первым выходом блока анализа, соединенного первым входом с первым выходом блока сравнения, вторым входом с первым выходом блока управления, вторым выходом - с первым входом блока управления, соединенного вторым входом с выходом переноса второго счетчика, распределитель импульсов, соединенный первым входом с выходом генератора тактовых импульсов, блок вывода, соединенный первыми входами с выходами второго счетчика, блок постоянной памяти, соединенный выходом с первым входом блока сравнения, второй дешифратор, соединенный входами с выходами второго счетчика, выходами - с первыми входами первого коммутатора, второй коммутатор, соединенный первыми входами с выходами первого дешифратора, выходами - с клеммами для подключения входов объекта контроля, отличающееся тем, что, с целью упрощения устройства за счет сокращения числа разрядов блока постоянной памяти и блока сравнения, расширения функциональных возможностей устройства и повышения достоверности контроля за счет обеспечения возможности контроля сопротивлений цепей и их участков; в него введены блок преобразования, источник стабилизированного напряжения, первая и вторая кнопки, причем второй вход второго коммутатора соединен через источник стабилизированного напряжения с первым выходом блока преобразования, соедииенного вторым выходом с вторым входом блока сравнения, входом - с выходом, первого коммутатора, соединенного вторыми входами с клеммами для подключения выходов объекта контроля, третьим входом - с вторым выходом блока управления, соединенного третьим выходом со счетным входом второго счетчика, третьим входом - с установочным входом второго счетчика, вторым входом блока вывода, первым входом генератора тактовых импульсов, установочным входом первого счетчика, третьим входом блока анализа и вторым входом распределителя импульсов, соединенного первым, вторым и третьим выходами

соответственно с четвертым и пятым входами блока анализа и с третьим входом блока вывода, третьим входом - с шестым входом блока анализа и с выходом переноса второго счетчика, вторым выходом - с четвертым входом блока управления, выходы первого счетчика соединены с первыми адресными входами блока постоянной памяти, вторые адресные входы которого соединены с выходами второго, счетчика, четвертый вход блока вывода соединен с третьим выходом блока анализа, пятые входы - с вторыми выходами блока сравнения, выход - с вторым входом генератора тактовых импульсов, соединенного третьим входом с выходом переполнения первого счетчика, первым входом через первую кнопку - с общей шиной устройства, соединенной через вторую кнопку с четвертым входом генератора тактовых импульсов, выходы первого счетчика соединены с шестыми входами блока вывода.

2.Устройство по п. 1, отличающееся тем, что генератор тактовых импульсов содержит первый элемент совпадения, соединенный первым и вторым входами соответственно

с первым и третьим входами генератора, выходом - с -входом первого / 5-триггера, соединенного S-входом с четвертым входом генератора, выходом - с первым входом второго элемента совпадения, соединенного вторым и третьим входами соответственно с выходом генератора импульсов и с вторым входом генератора, выходом - с выходом генератора.

3.Устройство по п. 1, отличающееся тем, что распределитель импульсов содержит первый -триггер, соединенный прямым выходом с первым выходом распределителя импульсов и с D-входом второго D-триггера, соединенного прямым выходом с вторым выходом распределителя импульсов и с D-входом третьего D-триггера, соединенного прямым выходом с третьим выходом распределителя импульсов, С-входом - с С-входами первого, второго D-триггеров и с первым входом распределителя импульсов, соединенного вторым и третьим входами соответственно с первым и вторым входами третьего элемента совпадения, соединенного выходом

с / -входами первого, второго и третьего D-триггеров, четвертый элемент совпадения, соединенный первым и вторым входами соотт ветственно с инверсными выходами первого и второго D-триггеров, а выходом - с D-входом первого D-триггера.

4.Устройство по п. 1, отличающееся тем, что блок анализа содержит пятый элемент совпадения, соединенный первым, вторым входами и выходом соответственно с вторым, четвертым входами и первым выходом блока анализа, шестой элемент совпадения, соединенный первым и вторым входами соответст- венно с третьим и шестым входами блока анализа, выходом - с S-входом четвертого D-триггера, соединенного с D- и С

0

0

Q 5

5

входами соответственно с первым и пятым входами блока анализа, прямым и инверсным выходами соответственно с вторым и третьим выходами блока анализа.

5.Устройство по п. 1, отличающееся тем, что блок управления содержит второй RS- триггер, соединенный 5-входом с первым входом блока управления, инверсным выходом - с первым выходом блока управления, прямым выходом - с вторым выходом блока управления и с первым входом седьмого элемента совпадения, соединенного вторым входом и выходом соответственно с четвертым входом и третьим выходом блока управления, одновибратор, соединенный входом с вторым входом блока управления, выходом - с первым входом восьмого элемента совпадения, соединенного вторым входом с третьим входом блока управления, выходом - с / -входом второго / 5-триггера.

6.Устройство по п. 1, отличающееся тем, что блок вывода содержит пятый D-триггер, соединенный D- и С-входами и инверсным выходом соответственно с четвертым, третьим входами и выходом блока вывода, / -вхо- дом - с выходом девятого элемента совпадения, соединенного первым входом с вторым входом блока вывода, вторым входом с выходом блока печати, соединенного первыми, вторыми и третьими входами соответственно с первыми, шестыми и пятыми входами блока вывода, четвертым входом - с прямым выходом пятого D-триггера.

7.Устройство по п. 1, отличающееся тем, что второй коммутатор содержит первые ключи, соединенные сигнальными входами с вторым входом второго коммутатора, выходами с соответствуюш,ими выходами второго коммутатора, а управляющими входами через соответствующие инверторы - с соответствующими первыми входами второго коммутатора.

8.Устройство по п. 1, отличающееся тем, что первый коммутатор содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, соединенные первыми входами с третьим входом первого коммутатора, вторыми входами - с соответствующими первыми входами первого коммутатора, выходами с управляющими входами соответствующих вторых ключей, соединенных входами с соответствующими вторыми входами первого коммутатора, выходами через соответствующие первые резисторы - с выходом первого коммутатора.

9.Устройство по п. 1, отличающееся тем, что блок преобразования содержит второй резистор, соединенный первым выводом с первым входом аналого-цифрового преобразователя и с входом блока преобразования, вторым выводом - с первым выходом блока преобразования и с вторым входом аналого- цифрового преобразователя, соединенного выходами с вторыми выходами блока преобразования.

13

nycf

ну

22

21

20

-/

Фиг.2

фиг.

п

25

26

21

фцв.З

фиг. 5

фиг. 7

D

3

(Риг.5

Фиг.8

5.1. «5. L

5.J

фиг. W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для управления многоканальным импульсным регулятором мощности переменного тока с @ -нагрузками | 1987 |

|

SU1545306A1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Преобразователь параллельного кода в последовательный | 1985 |

|

SU1339896A1 |

| Система управления технологическим процессом дискретного производства | 1984 |

|

SU1251110A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

Изобретение относится к контрольно- измерительной технике. Может быть использовано для автоматического контроля гальванических соединений. Цель изобретения - упрощение устройства. В устройство, содержащее счетчики 5, 15, дещифраторы 6, 16, блок 13 анализа, блок 12 сравнения, блок 14 управления-, распределитель 2 импульсов, генератор 1 тактовых импульсов, блок 4 постоянной памяти, блок 3 вывода, коммутаторы 9, 7, для достижения цели введены источник 11 стабилизироЬанного напряжения, блок 10 преобразования, первая 17 и вторая 8 кнопки. В описании изобретения раскрыты 1, 2, 13, 14, 3, 7, 9, 10 блоки. На чертеже показан объект 18 контроля. В устройстве при том же, что и в прототипе, количестве проверяемых гальванических связей объекта 18 контроля значительно снизилась разрядность блока 12 сравнения и блока 4 постоянной памяти до разрядности аналого-цифрового преобразователя (АЦП), входящего в блок 10. Разрядность АЦП не зависит от общего количества проверяемых точек объекта 18 контроля, а определяется количеством точек наиболее разветвленной цепи. Устройство производит допуско- вый контроль по сопротивлениям цепей и участков цепей объекта 18 контроля, что повыщает достоверность контроля. 8 з. п. ф-лы, 10 ил. i (Л ю 4 СХ5 ;о

| Матричный регистратор | 1979 |

|

SU858004A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля монтажа | 1976 |

|

SU613274A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-21—Подача