Изобретение относится к вычислиельной технике и автоматике и может ыть использовано в цифровых: системах ередачи данных.

Цель изобретения - расширение ункциональных возможностей преобразователя за счет преобразования последовательного кода в параллельньй упрощение перестройки преобразователя,

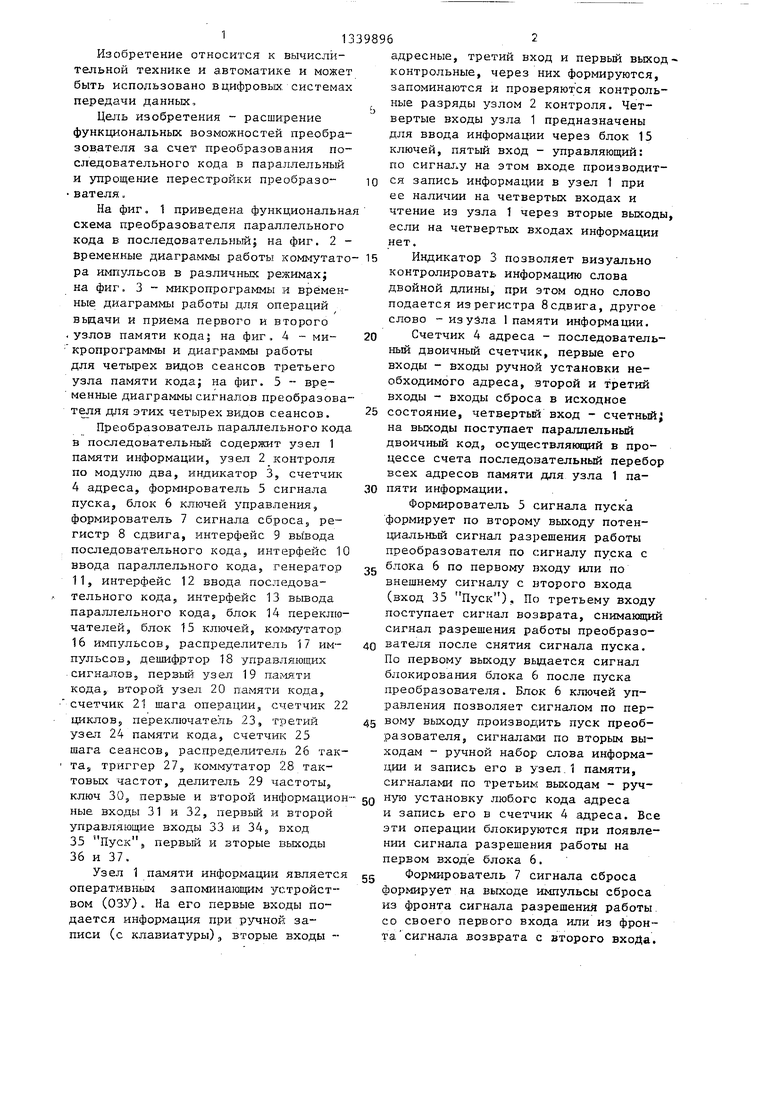

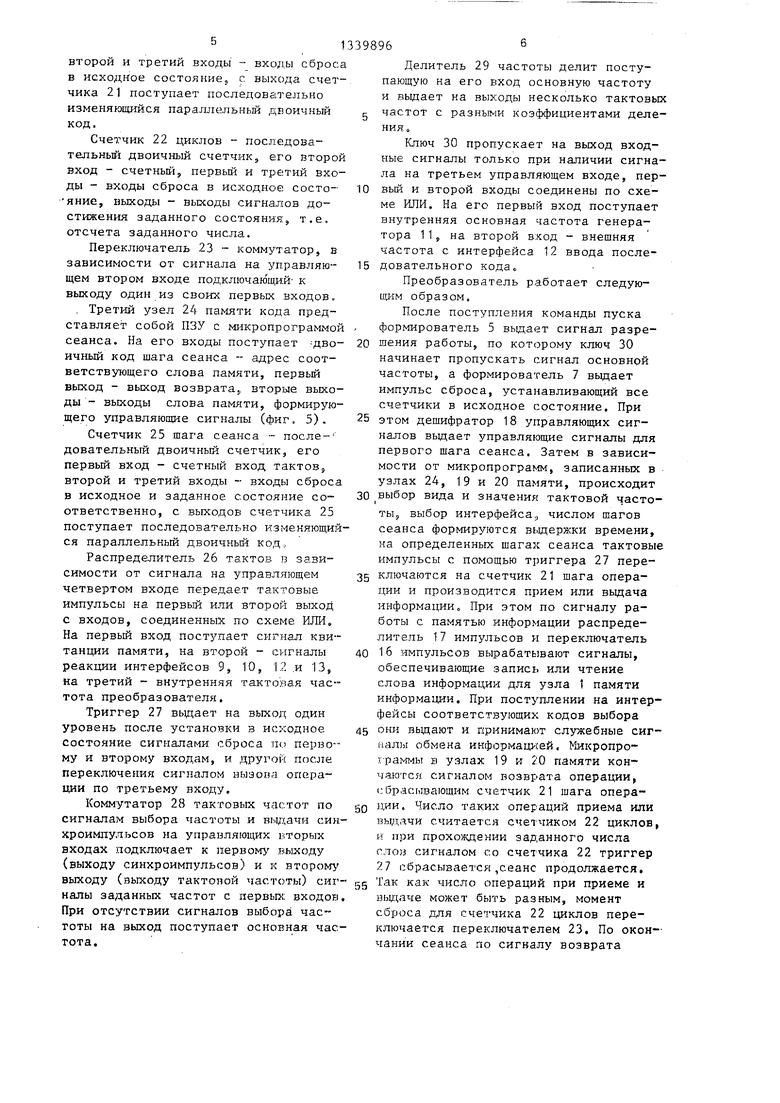

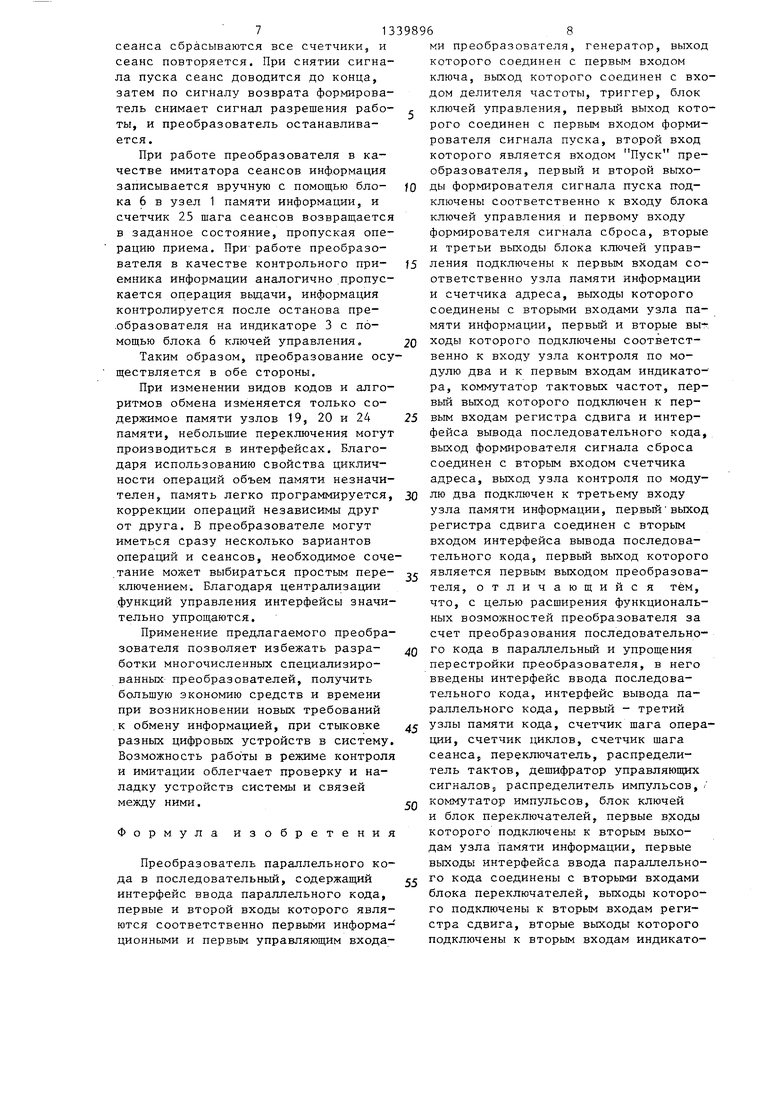

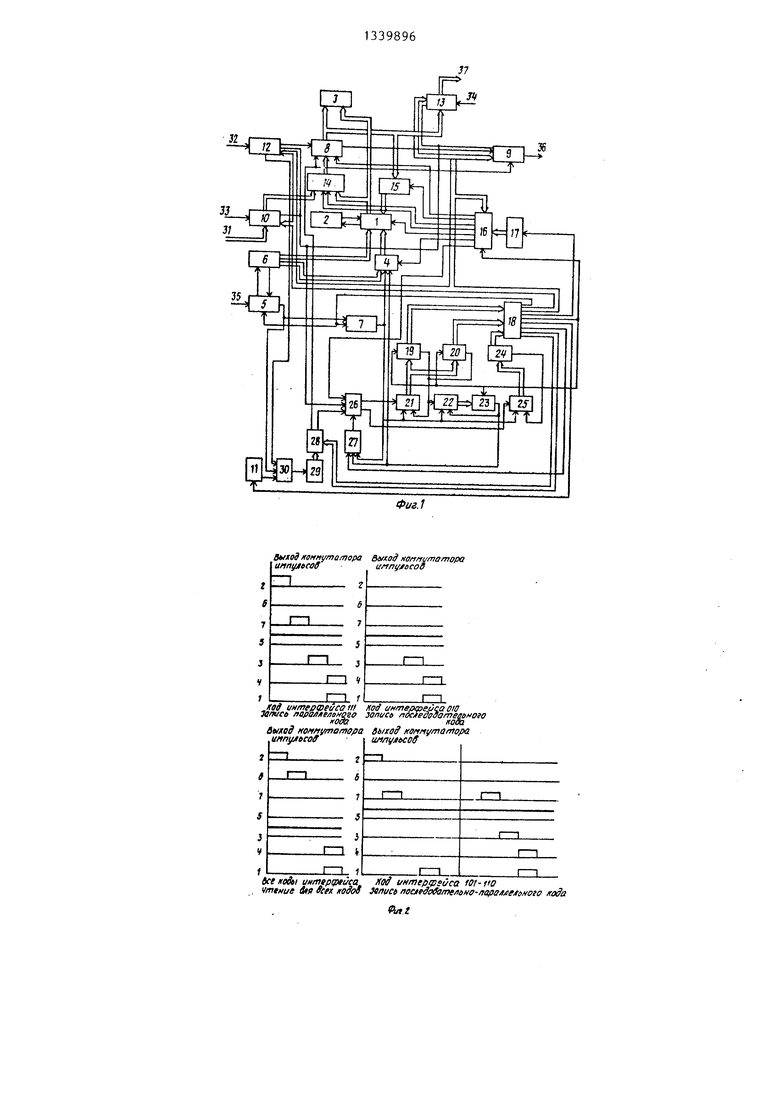

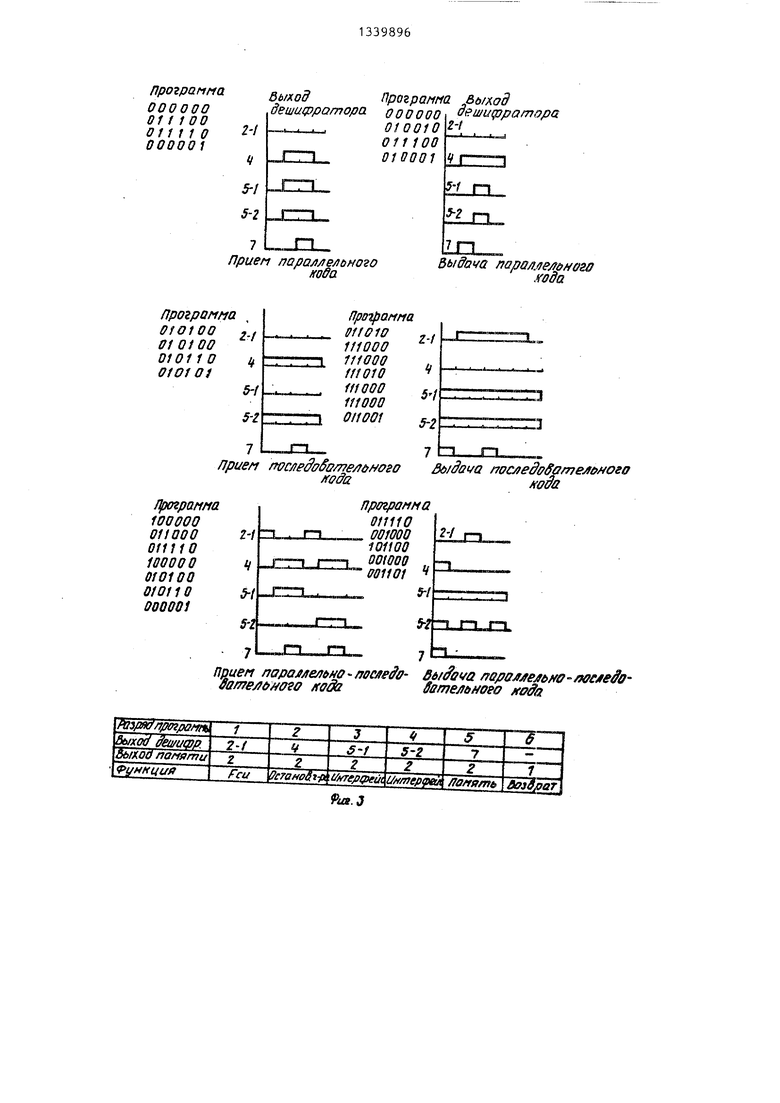

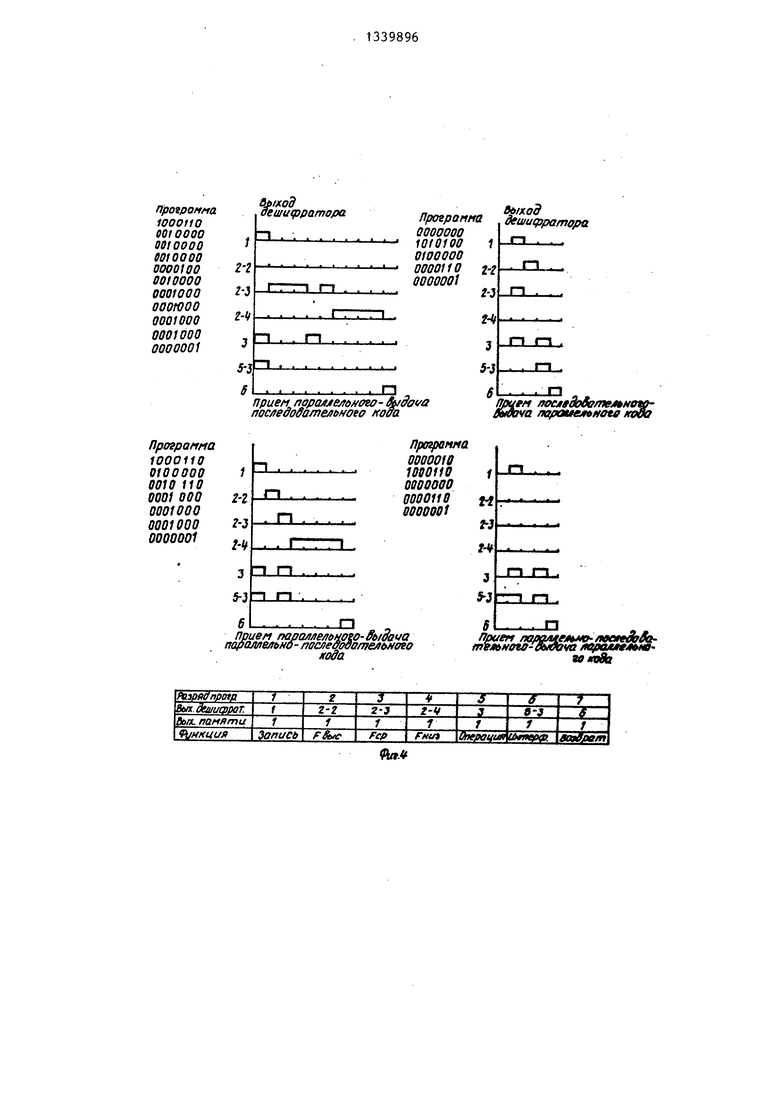

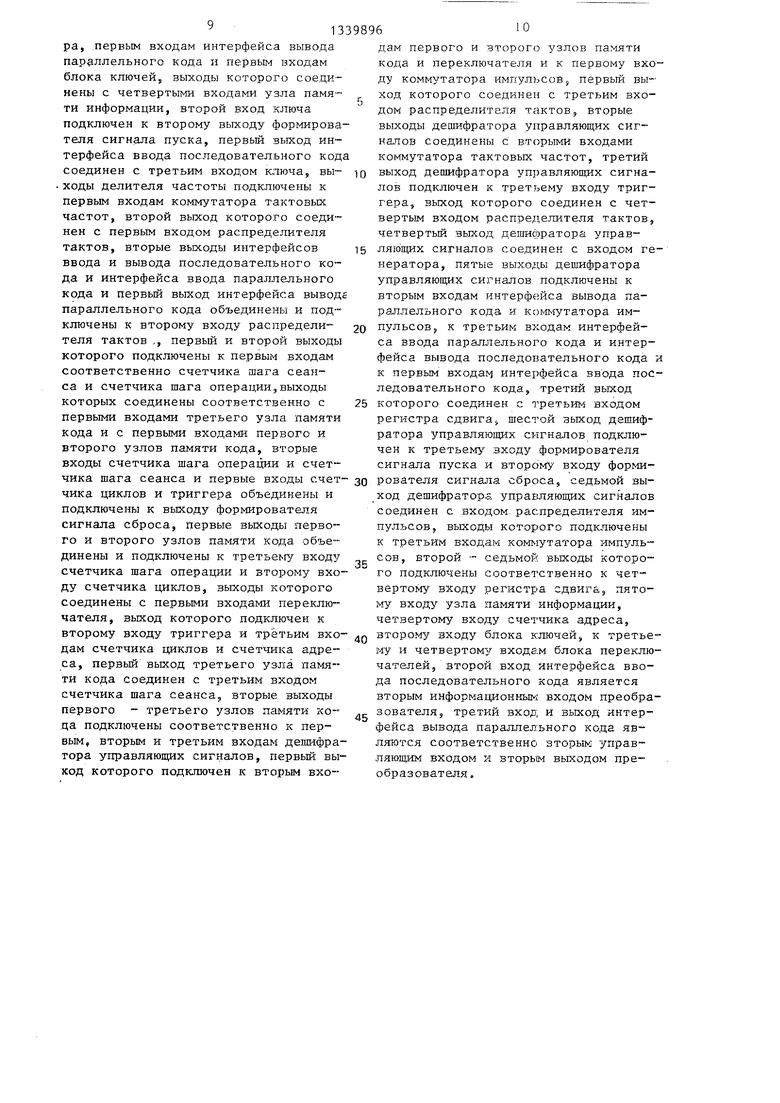

На фиг, 1 приведе 1а функциональная схема преобразователя параллельного кода в последовательньй; на фиг. 2 - временные диаграммы работы коммутатора импульсов в различных режимах; на фиг. 3 микропрограммы и временные диаграммы работы для операций вьдачи и приема первого и второго

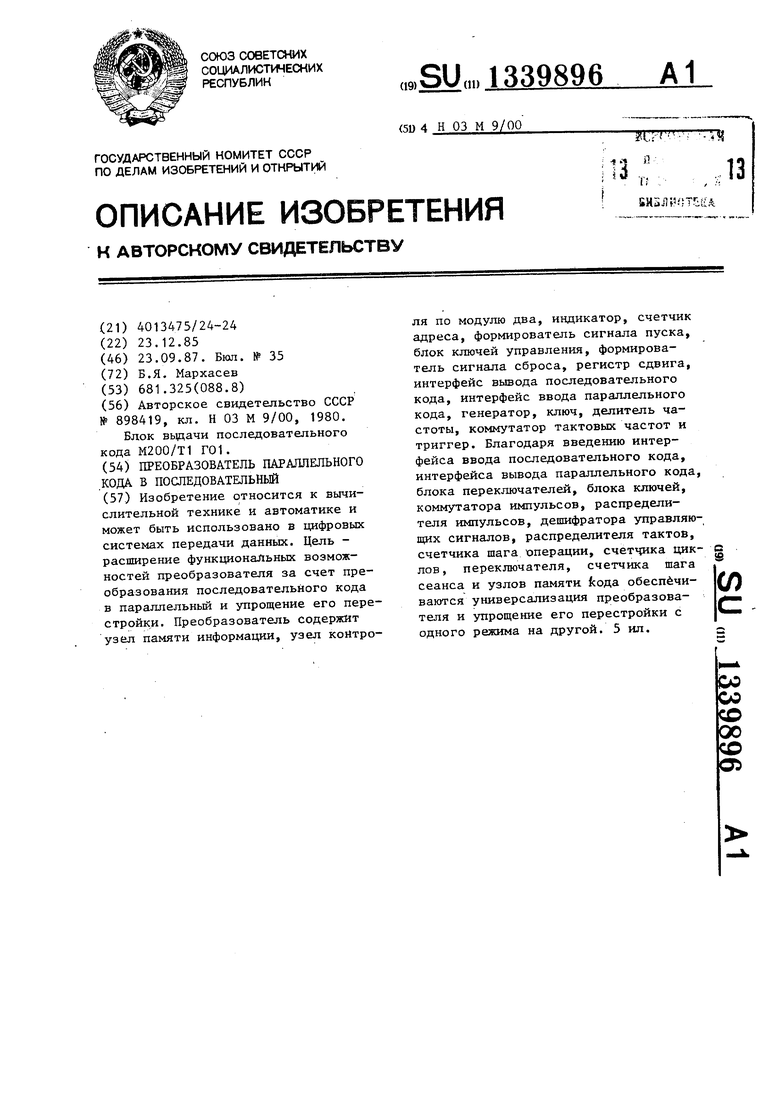

узлов памяти кода; на фиг. 4 - микропрограммы и диаграммы работы ля четырех видов сеансов третьего узла памяти кода; на фиг. 5 - вреенные диаграммы сигналов преобразоваеля для этих четырех видов сеансов.

Преобразователь параллельного кода в последовательный содержит узел 1 памяти информации, узел 2 контроля по модулю два, индикатор 3, счетчик 4 адреса, формирователь 5 сигнала пуска, блок 6 ключей управления, формирователь 7 сигнала сброса, регистр 8 сдвига, интерфейс 9 вы вода последовательного кода, интерфейс 10 ввода параллельного кода, генератор 11, интерфейс 12 ввода последовательного кода, интерфейс 13 вьтода параллельного кода, блок 14 переключателей, блок 15 ключей, коммутатор 16 импульсов, распределитель 17 импульсов, дешифртор 18 управляющих сигналов, первый узел 19 памяти кода, второй узел 20 памяти кода,

счетчик 21 шага операции, счетчик 22 циклов, переключатель 23, третий узел 24 памяти кода, счетчик 25 шага сеансов, распределитель 26 такта, триггер 27, коммутатор 28 тактовых частот, делитель 29 частоты, ключ 30, первые и второй информационные входы 31 и 32, первьй и второй управляющие входы 33 и 34, вход

первьй и вторые выходы

36и 37.

Узел 1 памяти информации является оперативным запоминающим устройством (ОЗУ). На его первые входы подается информация при ручной записи (с клавиатуры),, вторые входы адресные, третий вход и первьй выход- контрольные, через них формируются, запоминаются и проверяются контрольные разряды узлом 2 контроля. Чет-

вертые входы узла 1 предназначены

для ввода информации через блок 15 ключей, пятьй вход - управляющий: по сигнаг у на этом входе производит- ся запись информации в узел 1 при ее наличии на четвертых входах и чтение из узла 1 через вторые выходы,

если на четвертых входах информации нет.

Индикатор 3 позволяет визуально контролировать информацию слова двойной длины, при этом одно слово подается из регистра 8 сдвига, другое слово - изуЗла 1 памяти информации.

Счетчик 4 адреса - последовательный двоичньй счетчик, первые его входы - входы ручной установки необходимого адреса, второй и третий входы - входы сброса в исходное

состояние, четвертый вход - счетный; на выходы поступает параллельный двоичный код, осуществляющий в процессе счета последоззательный перебор всех адресов памяти для узла 1 папяти информации.

Формирователь 5 сигнала пуска формирует по второму выходу потен- циальньй сигнап разрешения работы преобразователя по сигналу пуска с

блока 6 по первому входу или по внешнему сигналу с второго входа (вход 35 Пуск), По третьему входу поступает сигнал возврата, снимаклций сигнал разрешения работы преобразователя после снятия сигнала пуска. По первому вькоду вьщается сигнал блокирования блока 6 после пуска преобразователя. Блок 6 ключей управления позволяет сигналом по первому выходу производить пуск преобразователя, сигналами по вторым выходам - ручной набор слова информации и запись его в узел,1 памяти, сигналами по третьим выходам - ручную установку любого кода адреса

и запись его в счетчик 4 адреса. Все эти операции блокируются при появлении сигнала разрешения работы на первом входе блока 6.

Формирователь 7 сигнала сброса формирует на выходе импульсы сброса из фронта сигнгша разрешений работы со своего первого входа или из фронта сигнала возврата с второго вхоДа.

31339896

Регистр 8 сдвига служит буферным регистром памяти и преобразователем .последовательного кода в параллельный, а параллельного кода в последо- вательньй, С его помощью производится з упаковка и распаковка слов параллельного кода с разрядностью, меньшей длины регистра. Первьш вход - вход тактовых импульсов сдвига, первый выход - выход последовательного кода вторые входы и выходы служат для параллельного ввода и вывода информации, третий вход - вход записи последовательного кода, четвертый вход вход параллельного сброса регистра 8

Интерфейс 9 вывода последовательного кода по синхроимпульсам, поступающим на первьй вход, преобразует

уровни и форму сигнала последователь20

10

15

25

30

него кода с второго входа к виду, необходимому для вьщачи на первый выход (выход 36), третий вход - вход управления интерфейсом 9, второй выход - выход реакдии интерфейса 9.

Интерфейс 10 ввода параллельного кода преобразует уровни входного параллельного кода со своих первых входов (входы 31) к уровням, принятым в преобразователе по первым выходам второй вход служит для внешнего управления, второй выход - выход реакции интерфейса 10, третьи входы - входы управления интерфейсом 10.

Генератор 11 вырабатывает на выходе основную, самую высокую, тактовую частоту для работы устройства, сигнал на входе запирает или отпирает генератор 11.

Интерфейс 12 ввода последовательного кода преобразует уровни и вид входного последовательного кода со своего второго входа (вход 32) к уровням и виду, принятым в преобразователе по третьему выходу, первый выход - выход синхроимпульсов, второй выход - выход реакции интерфейса 12, первые входы - входы управления интерфейсом 12.

Интерфейс 13 вывода параллельного кода преобразует уровни параллельного кода с первых входов к уровням и виду, необходимым для выдачи на вторые выходы (выходы 37), второй вход - вход управления интерфейсом 13, первый вьпход - выход реакции интерфейса 13.

Блок 14 переключателей подключает к своим выходам первые или втоп

и и п п с ч

с р в в

л в с с п в х п и н в и

м в м

40

45

50

з

20

10

15

25

30

рые входы по сигналам на третьем и четвертом (управляющих) входах соответственно.

В блоке 15 ключей первые входы подключаются к выходам по сигналу на втором входе.

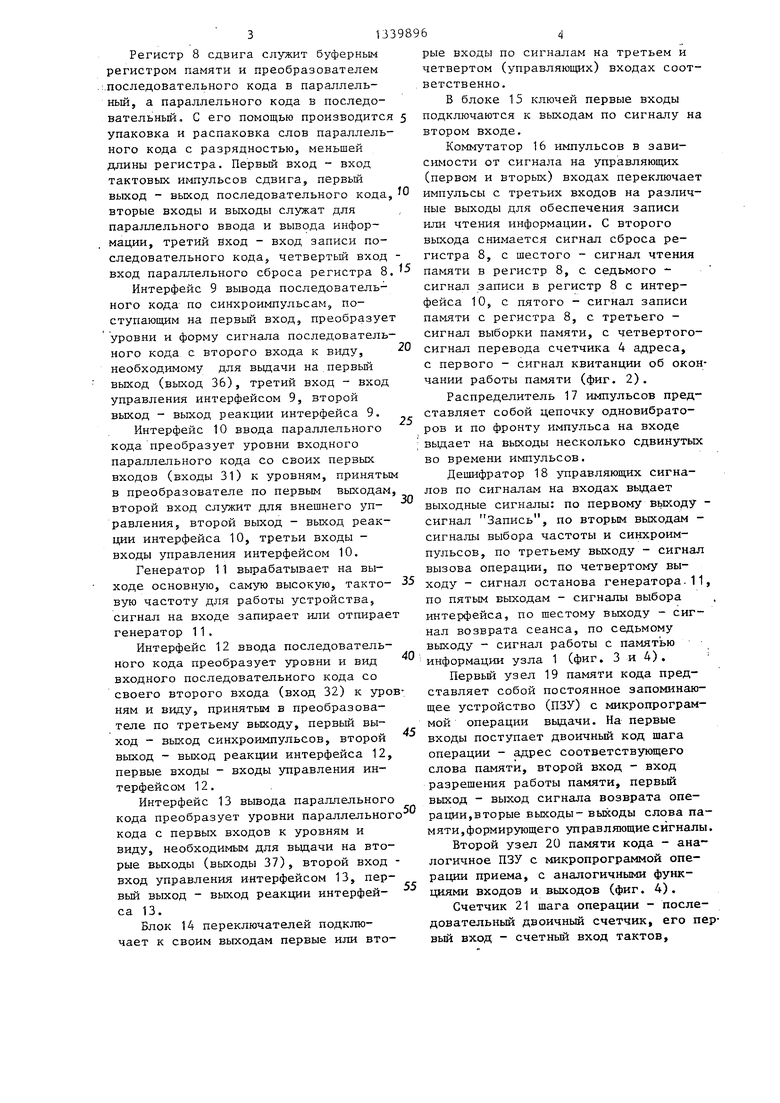

Коммутатор 16 импульсов в зависимости от сигнала на управляющих (первом и вторых) входах переключает импульсы с третьих входов на различные выходы для обеспечения записи или чтения информации. С второго выхода снимается сигнал сброса регистра 8, с шестого - сигнал чтения памяти в регистр 8, с седьмого сигнал записи в регистр 8 с интерфейса 10, с пятого - сигнал записи памяти с регистра 8, с третьего - сигнал выборки памяти, с четвертого- сигнал перевода счетчика 4 адреса, с первого - сигнал квитанции об окончании работы памяти (фиг. 2).

Распределитель 17 импульсов представляет собой цепочку одновибрато- ров и по фронту импульса на входе вьщает на выходы несколько сдвинутых во времени импульсов.

Дешифратор 18 управляющих сигналов по сигналам на входах вьщает выходные сигналы: по первому вькоду - сигнал Запись, по вторым выходам - сигналы выбора частоты и синхроимпульсов, по третьему выходу - сигнал вызова операции, по четвертому вы- ходу - сигнал останова генератора. 11, по пятым выходам - сигналы выбора интерфейса, по шестому выходу - сигнал возврата сеанса, по седьмому выходу - сигнал работы с памятью информации узла 1 (фиг. 3 и 4).

Первый узел 19 памяти кода представляет собой постоянное запоминающее устройство (ПЗУ) с микропрограммой операции выдачи. На первые входы поступает двоичный код шага операции - адрес соответствующего слова памяти, второй вход - вход разрешения работы памяти, первый выход - выход сигнала возврата операции, вторые выходы- выходы слова памяти, формирующего управляющиесигналы.

Второй узел 20 памяти кода - аналогичное ПЗУ с микропрограммой операции приема, с аналогичными функ- циями входов и выходов (фиг. 4).

Счетчик 21 шага операции - последовательный двоичный счетчик, его первьй вход - счетньш вход тактов.

40

45

50

51

второй и третий входы - входы сброса в исходное состояние, с выхода счетчика 21 поступает последовательно изменяющийся паралл шьньй двоичный код.

Счетчик 22 циклов - последовательный двоичный счетчик, его второй вход - счетный первый и третий входы - входы сброса в исходное состо

яние, выходы - выходы сигналов достижения заданного состояния, т.е. отсчета заданного числа.

Переключатель 23 - коммутатор, в зависимости от сигнала на управляющем втором входе подключающий- к выходу один из своих первых входов. . Третий узел 24 памяти кода представляет собой ПЗУ с микропрограммой сеанса. На его входы поступает ;дво- ичный код шага сеанса - адрес соответствующего слова памяти, первьй выход - выход возврата;, вторые выходы - выходы слова памяти, формирующего управляющие сигналы (фиг. 5).

Счетчик 25 шага сеанса - после- довательный двоичный счетчик, его первый вход - счетный вход тактов, второй и третий входы - входы сброса в исходное и заданное состояние соответственно, с вькодов счетчика 25 поступает последовательно изменяющийся параллельный двоич 1ый код.

Распределитель 26 тактов в зависимости от сигнала на управляющем четвертом входе передает тактовые импульсы на первьй или второй выход с входов, соединенных по схеме ИЛИ, На первый вход поступает сигнал квитанции памяти, на второй - сигналы реакции интерфейсов 9, 10, 12 ,и 13, на третий - внутренняя тактовая частота преобразователя.

Триггер 27 вьщает на выход один уровень после установки в исходное состояние сигналами сброса по первому и второму входам, и другой после переключения сигналом вызова операции по третьему входу.

Коммутатор 28 тактовых частот по сигналам выбора частоты и вьщачи синхроимпульсов на управляющих вторых входах подключает к перлом выходу (выходу синхроимпульсов) и к второму

выходу (выходу тактовой частоты) сиг- ggТак как число операций при приеме и

налы заданных частот с иервык; входов,вьщаче может быть разным, момент

При отсутствии сигналов выб.ора час-сброса рдя счетчика 22 циклов перетоты на выход поступает основная час-ключается переключателем 23, По окон-

тота,чании сеанса по сигналу возврата

5

0

Делитель 29 частоты делит поступающую на его вход основную частоту и выдает на выходы несколько тактовых частот с разными коэффициентами деления.

Ключ 30 пропускает на выход входные сигналы только при наличии сигнала на третьем управляющем входе, первый и второй входы соединены по схеме ИЛИ, На его первый вход поступает внутренняя основная частота генератора 11, на второй вход - внешняя частота с интерфейса 12 ввода последовательного кода,

Преобразователь работает следующим образом.

После поступления команды пуска формирователь 5 выдает сигнал разрешения работы, по которому ключ 30 начинает пропускать сигнал основной частоты, а формирователь 7 вьщает импульс сброса, устанавливающий все счетчики в исходное состояние. При

5 этом дешифратор 18 управляющих сигналов вьщает управляющие сигналы .для первого шага сеанса. Затем в зависимости от микропрограмм, записанных в узлах 24, 19 и 20 памяти, происходит

0 выбор вида и значения тактовой частоты,, выбор интерфейса,, числом шагов сеанса формируются вьщержки времени, на определенных шагах сеанса тактовые импульсы с помощью триггера 27 пере5 ключаются на счетчик 21 шага операции и производится прием или выдача информации. При этом по сигналу работы с памятью информации распределитель 17 импульсов и переключатель

0 16 импульсов вырабатывают сигналы, обеспечивающие запись или чтение слова информации для узла 1 памяти информации. При поступлении на интерфейсы соответствующих кодов выбора

5 они вьщают и принимают служебные сигналы обмена информац : ей, Микропро- j paNMb в узлах 19 и 20 памяти кончаются сигналом возврата операции, сбрасывающим счетчик 21 шага опера0 ции. Число таких операций приема или считается счетчиком 22 циклов, и при прохождении заданного числа слов сигналом со счетчика 22 триггер 27 сбрасывается ,сеанс продолжается.

сеанса сбрасываются все счетчики, и сеанс повторяется. При снятии сигнала пуска сеанс доводится до конца, затем по сигналу возврата формирователь снимает сигнал разрешения рабо- ты, и преобразователь останавливается.

При работе преобразователя в качестве имитатора сеансов информация записывается вручную с помощью бло- ка 6 в узел 1 памяти информации, и счетчик 25 шага сеансов возвращается в заданное состояние, пропуская операцию приема. При работе преобразователя в качестве контрольного при- емника информации аналогично пропускается операция вьщачи, информация контролируется после останова пре- .образователя на индикаторе 3 с помощью блока 6 ключей управления.

Таким образом, преобразование осуществляется в обе стороны.

При изменении видов кодов и алгоритмов обмена изменяется только содержимое памяти узлов 19, 20 и 24 памяти, небольшие переключения могут производиться в интерфейсах. Благодаря использованию свойства цикличности операций объем памяти незначителен, память легко программируется, коррекции операций независимы друг от друга. В преобразователе могут иметься сразу несколько вариантов операций и сеансов, необходимое сочетание может выбираться простым пере- ключением. Благодаря централизации функций управления интерфейсы значительно упрощаются.

Применение предлагаемого преобразователя позволяет избежать разра- ботки многочисленньЕС специализированных преобразователей, получить большую экономию средств и времени при возникновении новых требований к обмену информацией, при стыковке разньпс цифровых устройств в систему Возможность работы в режиме контроля и имитации облегчает проверку и наладку устройств системы и связей между ними.

Формула изобретения

Преобразователь параллельного кода в последовательный, содержащий интерфейс ввода параллельного кода, первые и второй входы которого являются соответственно первыми информационными и первым управляющим входами преобразователя, генератор, выход которого соединен с первым входом ключа, выход которого соединен с входом делителя частоты, триггер, блок ключей управления, первый выход которого соединен с первым входом формирователя сигнала пуска, второй вход которого является входом Пуск преобразователя, первый и второй выходы формирователя сигнала пуска подключены соответственно к входу блока ключей управления и первому входу формирователя сигнала сброса, вторые и третьи выходы блока ключей управления подключены к первым входам соответственно узла памяти информации и счетчика адреса, выходы которого соединены с вторьпчи входами узла памяти информации, первый и вторые выг ходы которого подключены соответственно к входу узла контроля по модулю два и к первым входам индикато- ра, коммутатор тактовых частот, первый выход которого подключен к первым входам регистра сдвига и интерфейса вывода последовательного кода, выход формирователя сигнала сброса соединен с вторым входом счетчика адреса, выход узла контроля по модулю два подключен к третьему входу узла памяти информации, первый выход регистра сдвига соединен с вторым входом интерфейса вывода последовательного кода, первый выход которого является первым выходом преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя за счет преобразования последовательного кода в параллельный и упрощения перестройки преобразователя, в него введены интерфейс ввода последовательного кода, интерфейс вывода параллельного кода, первый - третий узлы памяти кода, счетчик шага операции, счетчик циклов, счетчик шага сеанса, переключатель, распределитель тактов, дешифратор управляющих сигналов, распределитель импульсов,/ коммутатор импульсов, блок ключей и блок переключателей, первые входы которого подключены к вторым выходам узла памяти информации, первые выходы интерфейса ввода параллельного кода соединены с вторыми входами блока переключателей, выходы которого подключены к вторым входам регистра сдвига, вторые выходы которого подключены к вторым входам индикатоpa, .первым входам интерфейса вывода параллельного кода н первым входам блока ключей, выходы которого соединены с четвертыми входами узла памяти информации, второй вход ключа подключен к второму вьпх:оду формирователя сигнала пуска, первый выход интерфейса ввода последовательного код соединен с третьим входом ключа, вы™ ходы делителя частоты подключены к первым входам коммутатора тактовых частот, второй выход которого соединен с первьм входом распределителя тактов, вторые вьосоды интерфейсов ввода и вывода последовательного кода и интерфейса ввода параллельного кода и первый выход интерфейса вывод параллельного кода объединены и подключены к второму входу распределителя тактов ,, первый и второй выходы которого подключены к первым входам соответственно счетчика шага сеанса и счетчика шага операции,выходы которых соединены соответственно с первыми входами третьего узла памяти кода и с первыми входами первого и второго узлов памяти кода, вторые входы счетчика шага операции и счетчика шага сеанса и первые входы счетчика циклов и триггера объединены и подключены к выходу формирователя сигнала сброса, первые выходы первого и второго узлов памяти кода объединены и подключены к третьеъгу входу счетчика шага операции и второму входу счетчика циклов, выходы которого соединены с первыми входами переключателя, выход которого подключен к второму входу триггера и третьим входам счетчика циклов и счетчика адреса, первый выход третьего узла памяти кода соединен с третьим входом счетчика шага сеанса, вторые выходы первого - третьего узлов памяти кода подключены соответственно к первым, вторым и третьим входам дешифратора управляющих сигналов, первый выход которого подключен к вторым вхо

5

5

0

5

0

5

дам первого и второго узлов памяти кода и переключателя и к первому входу коммутатора импул1зСоВ5 первый выход которого соединен с третьим входом распределителя тактов, вторые выходы дешифратора управляющих сигналов соединены с вторыми входами коммутатора тактовых частот, третий выход дешифратора управляюсцих сигналов подключен к третьему входу триггера, выход которого соединен с четвертым входом распределителя тактов, четвертый выход дешифратора управляющих сигналов соединен с входом генератора, пятые выходы дешифратора управляюш;их си1 налов подключены к вторым входам интерфейса вывода параллельного кода и коммутатора импульсов j к третьим входам интерфейса ввода параллельного кода и интерфейса вывода последовательного кода и к первым входам интерфейса ввода последовательного кода, третий выход которого соединен с третьим входом регистра сдвигаs шестой выход дешифратора управляющих сигнапов подключен к третьем входу формирователя сигнала пуска и второму входу формирователя сигнала сброса, седьмой выход дешифратора управляющих сигналов соединен с входом, распределителя импульсов, выходы которого подключены к третьим входам коммутатора импульсов, второй - седьмой вькоды которого подключены соответственно к четвертому входу регистра сдвига, пятому входу узла памяти информации, четвертому входу счетчика адреса, второму входу блока ключей, к третье- f-ry и четвертому входам блока переключателей, второй вход интерфейса ввода последовательного кода является вторым информационным входом преобразователя, третий вход и выход интерфейса вывода параллельного кода являются соответственно вторым управляющим входом к BTopbtM выходом преобразователя ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для ввода информации в калькулятор | 1990 |

|

SU1791807A1 |

| Устройство для контроля канала связи | 1987 |

|

SU1478351A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для ввода информации | 1988 |

|

SU1636840A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в цифровых системах передачи данных. Цель - расширение функциональных возможностей преобразователя за счет преобразования последовательного кода в параллельный и упрощение его перестройки. Преобразователь содержит узел памяти информации, узел контроля по модулю два, индикатор, счетчик адреса, формирователь сигнала пуска, блок ключей управления, формирователь сигнала сброса, регистр сдвига, интерфейс вывода последовательного кода, интерфейс ввода параллельного кода, генератор, ключ, делитель частоты, коммутатор тактовых частот и триггер. Благодаря введению интерфейса ввода последовательного кода, интерфейса вывода параллельного кода, блока переключателей, блока ключей, коммутатора импульсов, распределителя импульсов, дешифратора управляющих сигналов, распределителя тактов, счетчика шага операции, счетчика циклов , переключателя, счетчика шага сеанса и узлов памяти &ода обеспечиваются универсализация преобразователя и упрощение его перестройки с одного режима на другой. 5 ил. (Л &0 со со 00 UD О5

яомнутатара моппитатора -uftnt/focoo

йвв интерфейса М /loif интершейуз ff/ff JafSucef /rtvo MSHOso записи nMefpaomeiKHoio

йсе noSti uttmtpiifffufa /(off икте(шейса fOr-fO

vmtHue Лн feex кодов Xnuc noc/ifoofame/ i no-naf aji/ fjtsMoio xooa

Йл

вмод deujuippomopu

г-1 ч

5-1 5-2

Приеп лара/}/1елоно о кова

npozpai fiu ,

010100 2.. I

01 0100

0101 1 0 It

Of Of о t

H 5-1

noue/i fWC/ eMome/t6f oso SufdavQ гюследеёателмогд

l pOMMa 100000

on 000

011110 100000 010100 01011Q 000001

т iBV Miiii I-- - - I I.If

nouen napQjf efl MO-ffOC/if o- ffBflO/fjre bffO /fffe s B- лодаЗвтелоного /foffa

Программа Во/мд 000000 д ши рратора

OiOOiQ 011100 010001

z-t

S-1 п

Sb/ffavG лараме &могз jfoda

деёат

Z-2

z-3 г-ч

aeufuippamojM

5-3

прием noptu/e/fdffffeo- &fdava посаеао&алггелбноео ко&а

2-г г-3

/-V

n

X-:

3 5-3

n

Прием парсмделон,оео-8ыдв а парамеяьно- посхеводвглелмоео кода

лроеронна dewutppamopa 0000000 10(0100 1

owoooo 0000110 2-г

ODOOOOi

г-3 г-if j

5-J

ffptfefi /юел 3о8втел но90- gSattva noffoue/ntfote moo

Прогронна

OOOOOfO

WSOiiO 0000000 00001 IB

ooooooi

J

5-J

Приен /тзоллллмр-авогеЛгЛ - mSi6ffOtS i9ova /я ммемм 80 АМЬ

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

Авторы

Даты

1987-09-23—Публикация

1985-12-23—Подача