1

Изобретение относится к вычислительной технике и может использоваться в системах тестового и функционального диагностирования цифровых устройств.

Целью изобретения является повышение надежности за счет обеспечения самоконтроля.

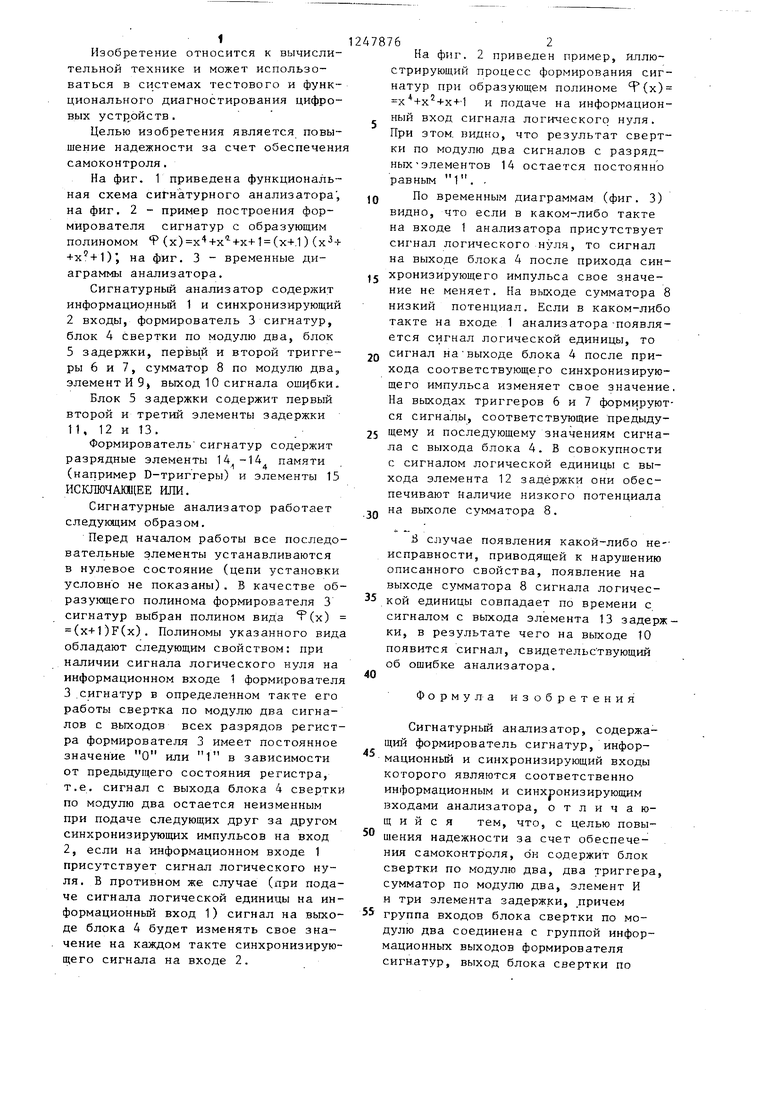

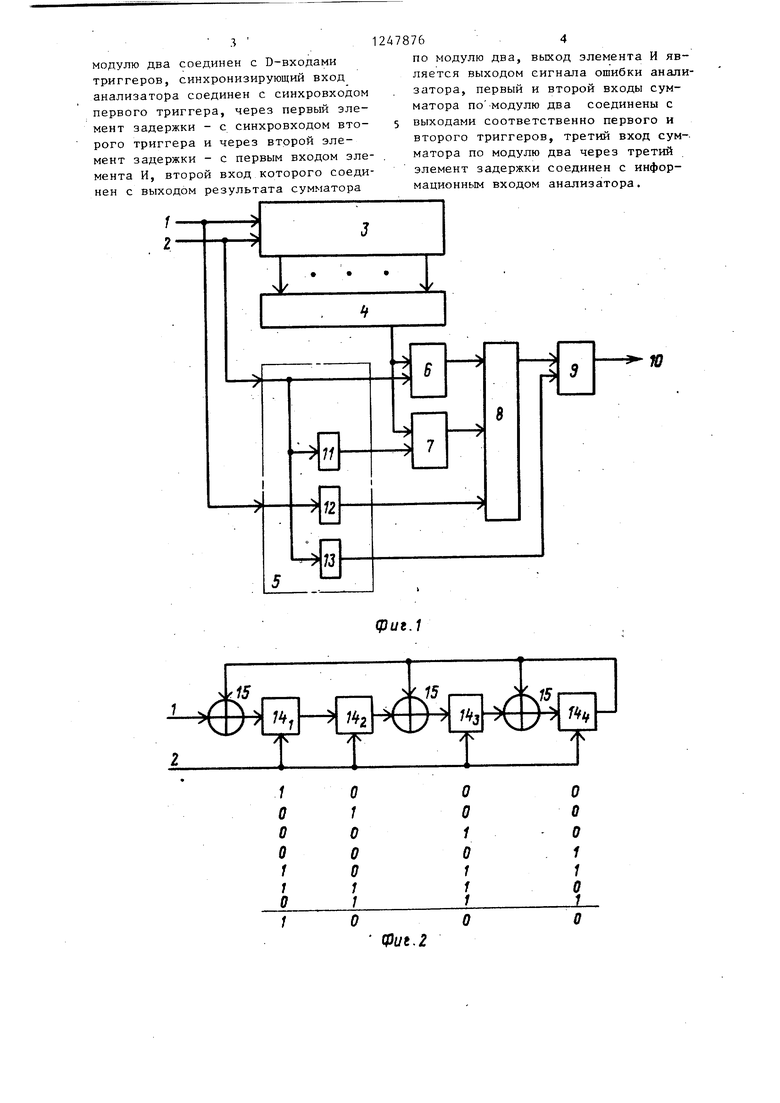

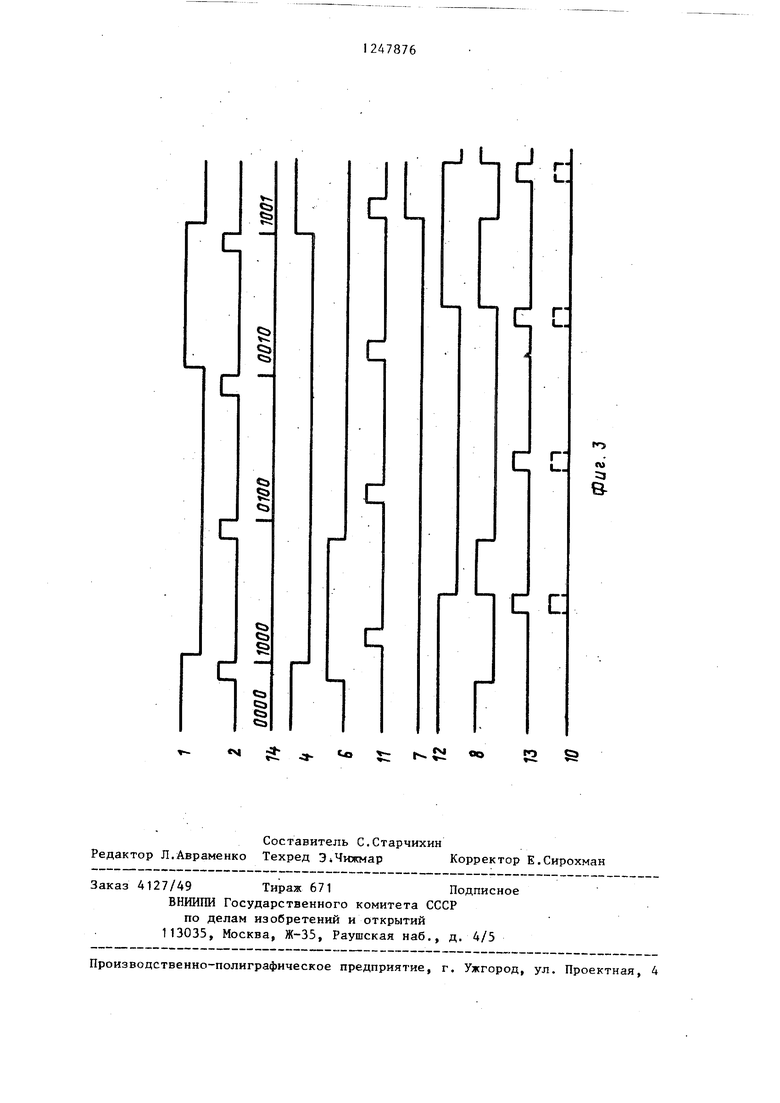

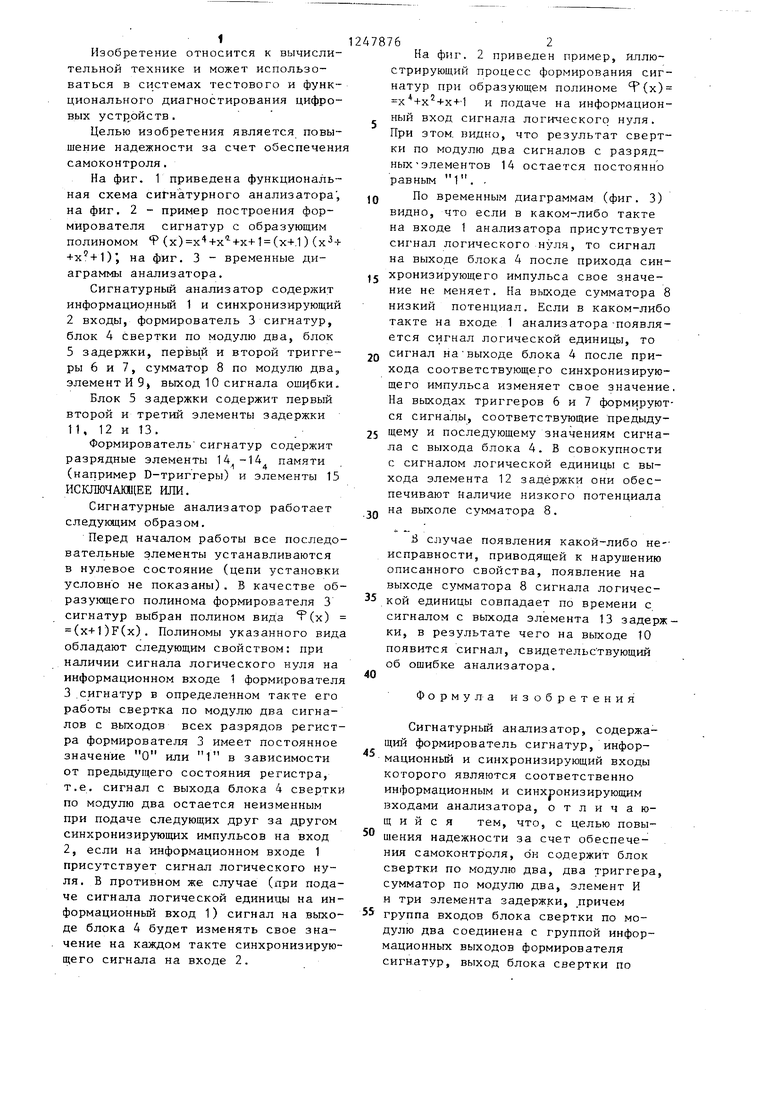

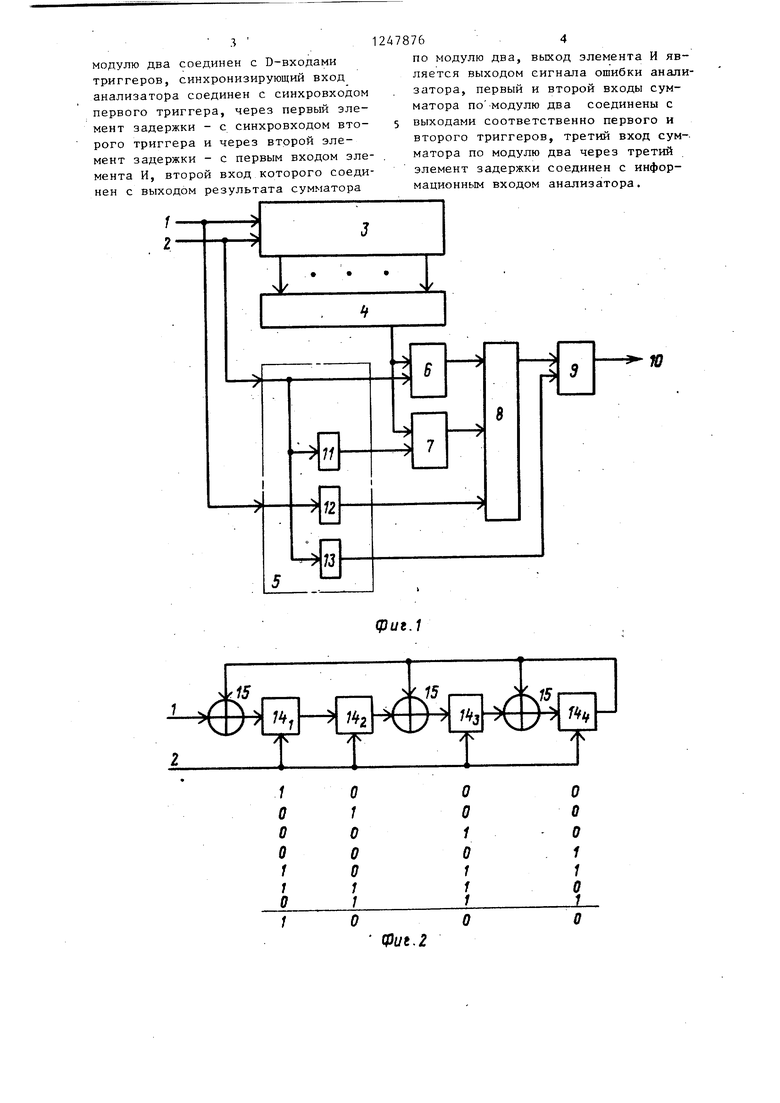

На фиг. 1 приведена функциональная схема сигнатурного анализатора; на фиг. 2 - пример построения формирователя сигнатур с образующим полиномом 9(x) (x+.1)( ); на фиг. 3 - временные диаграммы анализатора.

Сигнатурный анализатор содержит информационный 1 и синхронизирующий

2входы, формирователь 3 сигнатур, блок 4 свертки по модулю два, блок 5 задержки, первый и второй триггеры 6 и 7 , сумматор 8 по модулю два, элемент И 9 выход 10 сигнала ошибки.

Блок 5 задержки содержит первый второй и третий элементы задержки 11, 12 и 13.

Формирователь сигнатур содержит разрядные элементы 14,-1 , памяти (например D-триггеры) и элементы 15 ИСКЛЮЧАЮЩЕЕ ИЛИ.

Сигнатурные анализатор работает следугацим образом.

Перед началом работы все последовательные элементы устанавливаются в нулевое состояние (цепи установки условно не показаны). В качестве образующего полинома формирователя 3 сигнатур выбран полином вида Р(х) ( )F(x) . Полиномы указанного вида обладают следующим свойством: при наличии сигнала логического нуля на информационном входе 1 формирователя

3,сигнатур в определенном такте его работы свертка по модулю два сигналов с выходов всех разрядов регистра формирователя 3 имеет постоянное значение О или 1 в зависимости от предыдущего состояния регистра, т.е. сигнал с выхода блока 4 свертки по модулю два остается неизменным при подаче следующих друг за другом синхронизирующих импульсов на вход 2, если на информационном входе 1 присутствует сигнал логического нуля. В противном же случае (при подаче сигнала логической единицы на ин- формационньй вход 1) сигнал на выходе блока 4 будет изменять свое значение на каждом такте синхронизирующего сигнала на входе 2.

478762

На фиг. 2 приведен пример, иллюстрирующий процесс формирования сигнатур при образующем полиноме (х) х +х - -х+ 1 и подаче на информационный вход сигнала логического нуля. При зтом. видно, что результат свертки по модулю два сигналов с разрядных -элементов 14 остается постоянно равным 1. .

JQ По временным диаграммам (фиг. 3) видно, что если в каком-либо такте на входе 1 анализатора присутствует сиг нал логического , то сигнал на выходе блока 4 после прихода синJ5 хронизирующего импульса свое значение не меняет. На выходе сумматора 8 низкий потенциал. Если в каком-либо такте на входе 1 анализатора-появляется сигнал логической единицы, то

2Q сигнал на-выходе блока 4 после прихода соответствующего синхронизирующего импульса изменяет свое значение. На выходах триггеров 6 и 7 формируются сигналы, соответствующие предыду25 щему и последующему значениям сигнала с выхода блока 4. В совокупности с сигналом логической единицы с выхода элемента 12 задержки они обеспечивают Наличие низкого потенциала

,д на выходе сумматора 8.

В случае появления какой-либо не-- исправности, приводящей к нарушению описанного свойства, появление на выходе сумматора 8 сигнала логичес35

40

кой единицы совпадает по времени с сигналом с выхода элемента 13 задержки, в результате чего на выходе 10 появится сигнал, свидетельс твующий об ошибке анализатора.

Формула изобретения

СигнатурньЕй анализатор, содержащий формирователь сигнатур, информационный и синхронизирующий входы которого являются соответственно информационным и синхронизирующим входами анализатора, отличающийся тем, что, с целью повышения надежности за счет обеспечения самоконтроля, он содержит блок свертки по модулю два, два триггера, сумматор по модулю два, элемент И и три элемента задержки, причем группа входов блока свертки по модулю два соединена с группой информационных выходов формирователя сигнатур, выход блока свертки по

3

модулю два соединен с D-входами триггеров, синхронизирующий вход анализатора соединен с синхровходом первого триггера, через первый элемент задержки - с синхровходом второго триггера и через второй элемент задержки - с первым входом эле мента И, второй вход которого соеди нен с выходом результата сумматора

2478764

по модулю два, выход элемента И является выходом сигнала ошибки анализатора, первый и второй входы сумматора по модулю два соединены с 5 выходами соответственно первого и второго триггеров, третий вход сум-. матора по модулю два через третий элемент задержки соединен с информационным входом анализатора.

PUt.1

(put. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Сигнатурный анализатор | 1987 |

|

SU1499349A1 |

| Многофункциональный модуль для устройств встроенного контроля | 1987 |

|

SU1529222A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1336010A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Сигнатурный анализатор | 1989 |

|

SU1635184A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового и функционального диагностирования, цифровых устройств. Отличительной особенностью предлагаемого сигнатурного анализатора является обеспечение возможности самоконтроля непосредственно в процессе его функционирования. Это обеспечивается выбором образующего номинала формирователя сигнатур определенного вида, а именно, вида f (x) (x+1)F(x). При этом подобные номиналы имеют свойство сохранения четности сигнатуры при подаче на вход формирователя сигнатуры сигнала логического нуля и перемены четности - при подаче сигнала логической единицы. Дополнительные элементы, вводимые в анализатор, позволяют оперативно выявлять все неисправности анализатора, которые нарушают это свойство. 3 ил. i (П ГС 4 00 о

| Патент США № 3976864, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Электроника, 1977 | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-17—Подача