изобретение относится к области вычислительной техники и предназначено для построения контролепригодных цифровых устройств.

Цель изобретения - расширение функциональных возможностей за счет обеспечения дополнительно режимов параллельного многоканального сигнатурного анализатора, анализатора четности информационной последовательности, генерирования детерминированной последовательности и режима регистра сдвига.

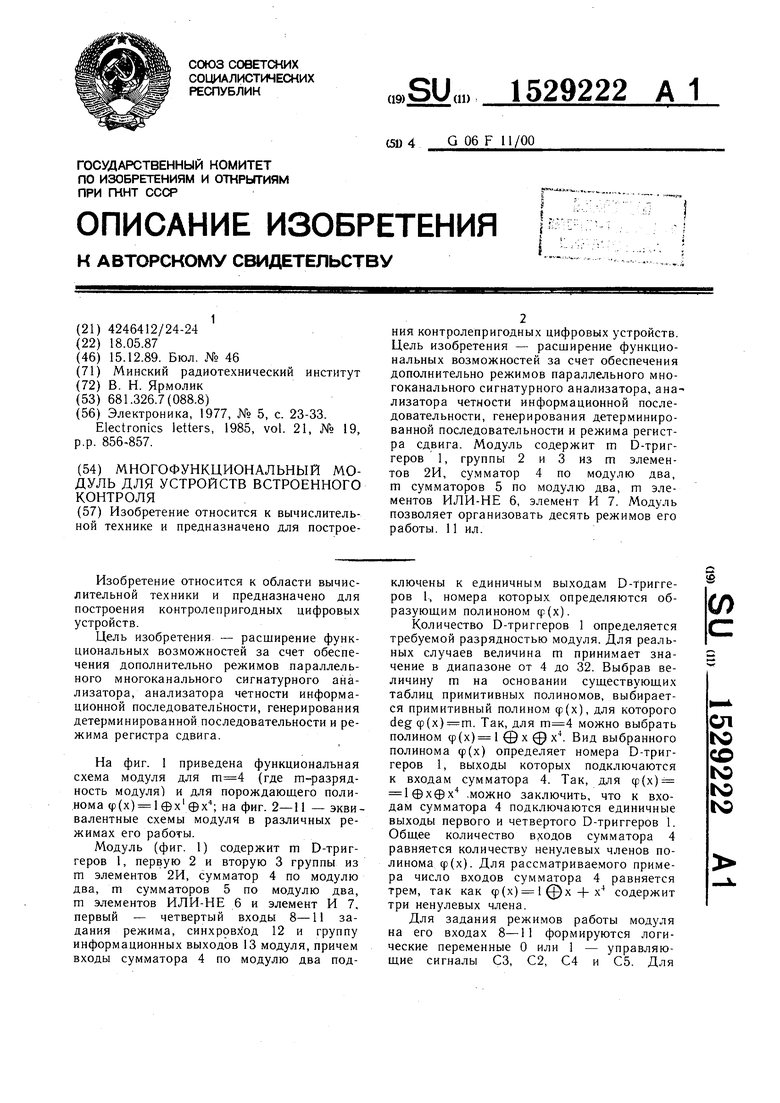

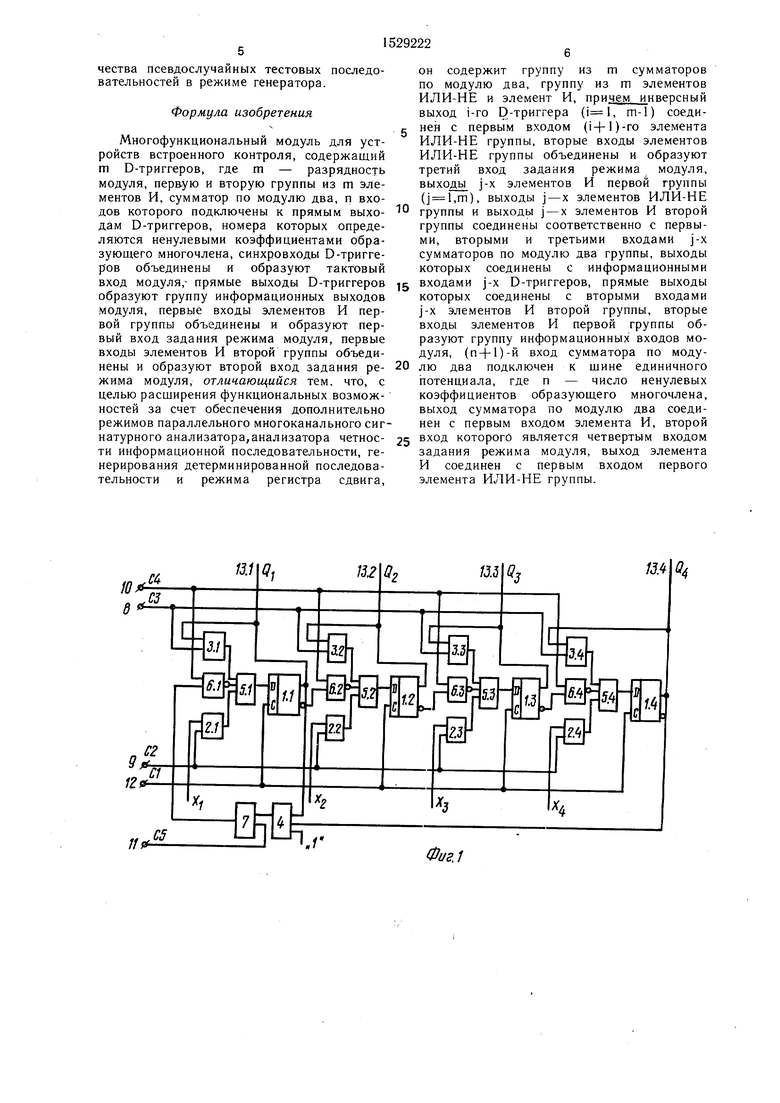

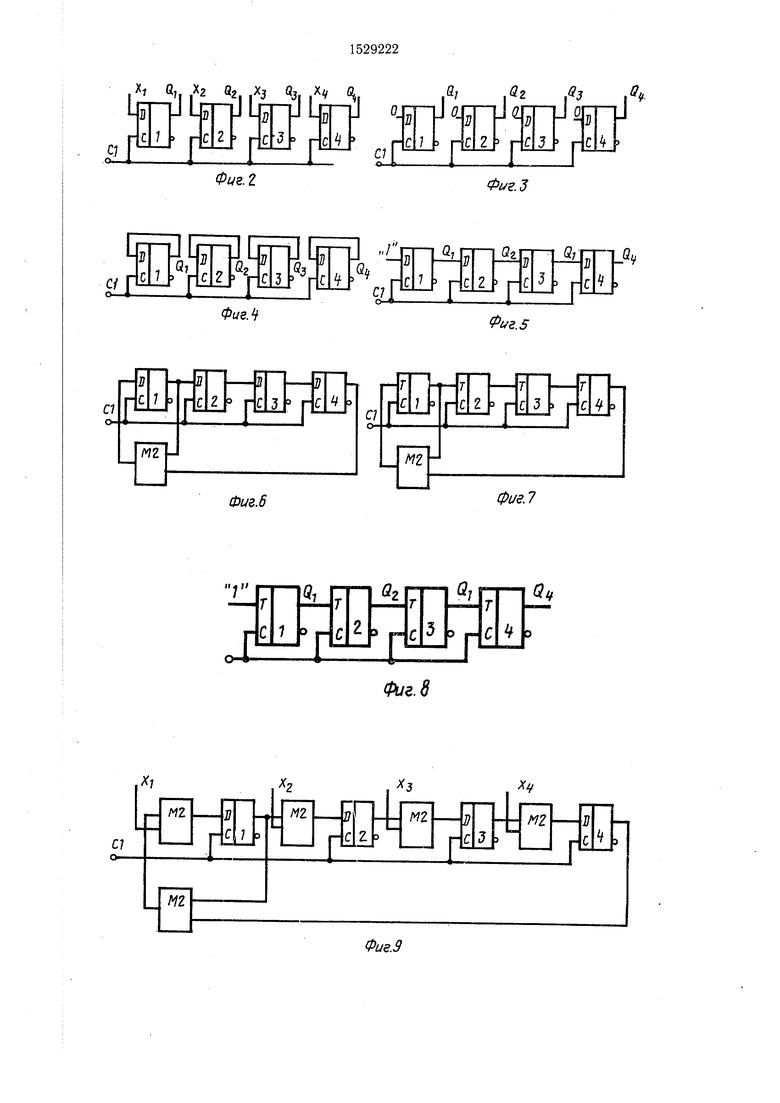

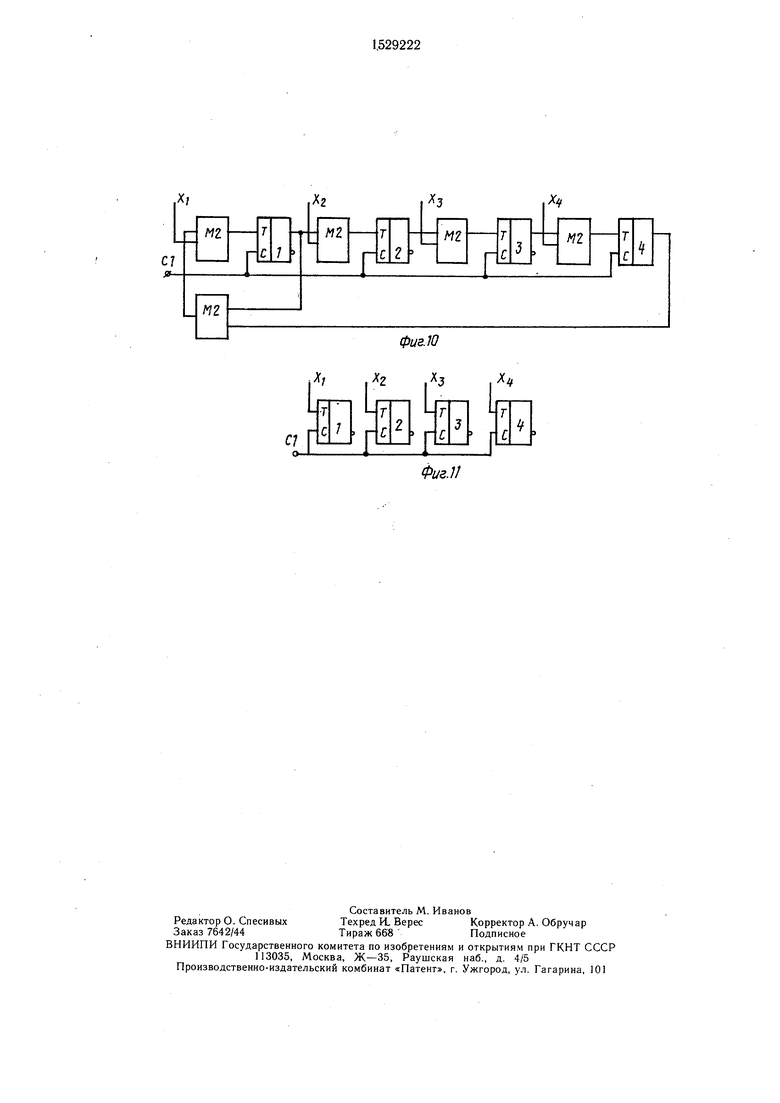

На фиг. 1 приведена функциональная схема модуля для (где ш-разряд- ность модуля) и для порождающего полинома ф(х) 1ех фх ; на фиг. 2-11 - эквивалентные схемы модуля в различных режимах его работы.

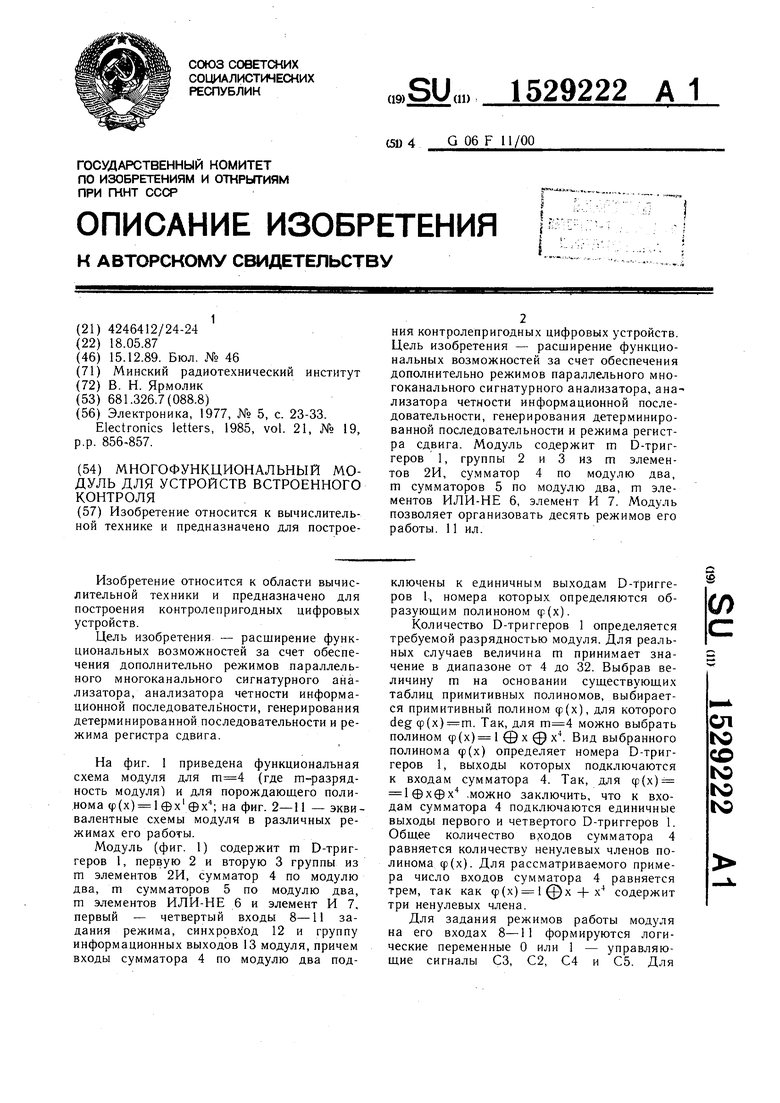

Модуль (фиг. 1) содержит m D-триг- геров 1, первую 2 и вторую 3 группы из m элементов 2И, сумматор 4 по модулю два, m сумматоров 5 по модулю два, ш элементов ЙЛИ-НЕ 6 и элемент И 7, первый - четвертый входы 8-11 задания режима, синхррвх од 12 и группу информационных выходов 13 модуля, причем входы сумматора 4 по модулю два подключены к единичным выходам D-Тригге- ров 1, номера которых определяются образующим полиноном ф(х).

Количество D-триггеров 1 определяется требуемой разрядностью модуля. Для реальных случаев величина m принимает значение в диапазоне от 4 до 32. Выбрав величину m на основании существующих таблиц примитивных полиномов, выбирается примитивный полином ф(х), для которого deg9(x)m. Так, для можно выбрать полином ф(х) 1 ® X ф X . Вид выбранного полинома ф(х) определяет номера D-триггеров 1, выходы которых подключаются к входам сумматора 4. Так, для ф(х) ISxffix .можно заключить, что к входам сумматора 4 подключаются единичные выходы первого и четвертого D-триггеров 1. Общее количество входов сумматора 4 равняется количеству ненулевых членов полинома ф(х). Для рассматриваемого примера число входов сумматора 4 равняется трем, так как ф(х) 1фх + х содержит три ненулевых члена.

Для задания режимов работы модуля на его входах 8-11 формируются логические переменные О или 1 - управляющие сигналы СЗ, С2, С4 и С5. Для

(в

(Л

01

ю

со ю |С ю

этих целей можно использовать двухпо- зиционные переключатели, формирующие на выходе значение О или 1, а также генераторы логической единицы и логического нуля.

Модуль работает следующим образом.

В зависимости от значений управляющих сигналов С2, СЗ, С4 и С5 возможны следующие режимы работы, все множество которых можно разбить на три подПоследовательный генератор псевдослучайных тестовых наборов.

В данном режиме , , , и схема модуля преобразуется в генератор М-последовательности (фиг. 6).

Параллельный генератор псевдослучайных тестовых наборов.

В данном режиме , , , и схема модуля преобразуется в генератор псевдослучайных чисел, при этом

множества. Последовательно рассмотрим 10 последующий тестовый набор полностью отвсе режимы каждого из них.личается от текущего (фиг. 7).

Генератор детерминированной последоваПодмножество режимов работы модуля, когда его элементы памяти используются по своему прямому назначению, т. е. выпо- няют функцию хранения информации.

Режим ш элементов памяти.

Данный режим обеспечивается следующими значениями управляющих сигналов , , , , где X означает, что сигнал С5 может принимать значение нуля либо единицы. В этом ре- 20 жиме для схема модуля преобразует- ся к следующему эквивалентному виду (фиг. 2). Как видно из фиг. 2, устройство представляет собой набор элементов памяти, в которые записывается информация путем подачи синхронизирующего импульса на вход устройства 01. Под действием данного сигнала входной вектор Х1Х2ХзХ4 записывается на элементы памяти.

тельности. Для случая при , , , на выходах 13.1 - -g 13.4 устройства (фиг. 8) формируется следующая детерминированная тестовая последовательность.

Q, Q2 Рз Q4

о о о, о

1000 0100

1 Г 1 000 1 О О

01 О

11 1

О 1 1 1 1

0000

Подмножество режимов работы модуля в качестве анализирующей схемы.

Многоканальный сигнатурный анализаРежим установки в ноль элементов памя- зо ройс туры

ти модуля.

Данный режим обеспечивается следующими значениями управляющих сигналов , , , . Все элементы памяти установятся в нулевое состояДля обеспечения данного режима , , , . В данном режиме устройство будет формировать значение сигнатуры как результат сжатия ш входных

последовательностей х, ,m. Для

н-ие под действием синхроимпульса С1 35 эквивалентная схема устройства приведена (фиг. 3). на фиг. 9.

Режим хранения.Параллельный многоканальный сигнаВ этом режиме , , , турный анализатор.

и при подаче синхроимпульсов наВ этом случае С2 1, С3 1, , С5 1

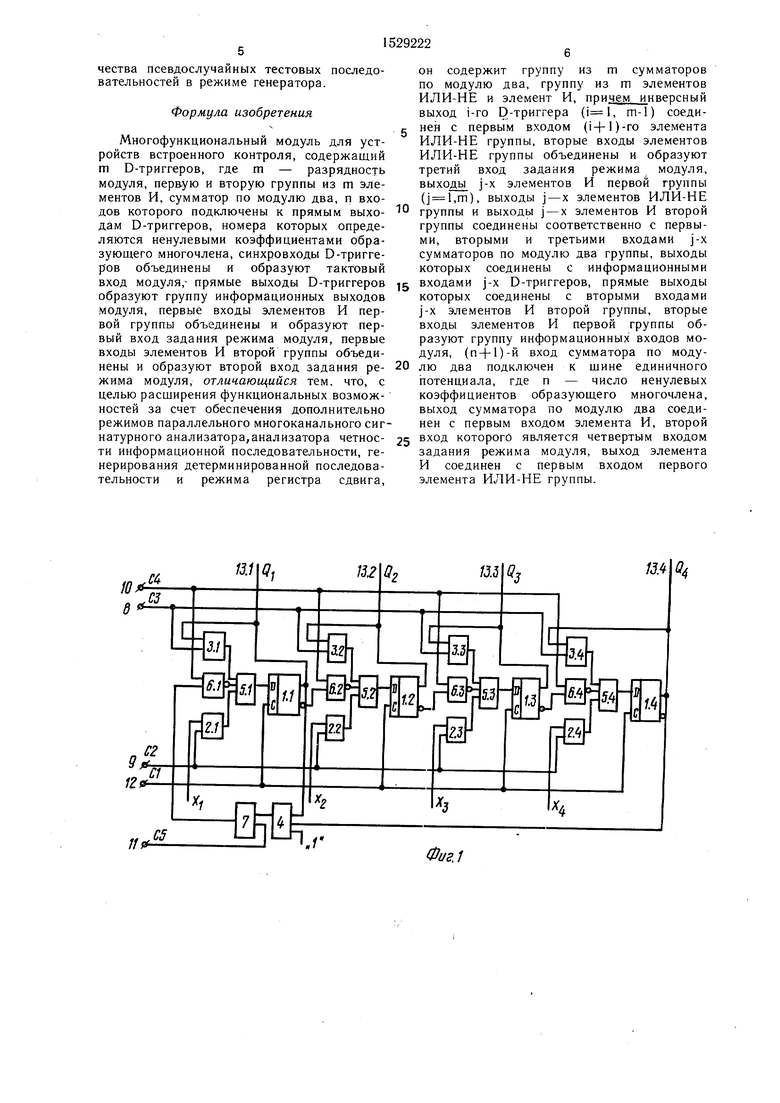

вход 12 (сигнал С1) элементы памяти и схема устройства будет представлять будут сохранять свое предыдущее состоя-собой параллельный многоканальный сигнатурный анализатор (фиг. 10).

Схема, определяющая четность количестние (фиг. 4).

Режим регистра сдвига.

В этом режиме , , , . Эквивалентная схема устройства для данного режима приведена на фиг. 5. 45 этом случае , , ,

ва единиц в последовательностях х/, / 1, т.

Она представляет собой регистр сдвига, сдвигающий на один разряд вправо. При сдвиге информации на первый элемент памяти записывается значение единицы. Микрооперация сдвига осуществляется под действием синхроимпульса С1.50

Последовательно используя приведенные режимы первой группы, можно выполнять и ряд других действий. Так, например, последовательное выполнение режимов 1.2 и 1.4 позволяет установить все элементы памяти в единичное состояние.55

Подмножество режимов работы модуля, обеспечивающих генерирование тестовых воздействий.

и эквивалентная схема примет вид (фиг. 11). Содержимое элементов памяти устройства будет определять четность единичных символов в анализируемой последовательности.

Таким образом, данное техническое реще- ние позволяет организовать десять режимов его работы, за счет чего заметно расширяются функциональные возможности устройства.

Кроме того, надежность модуля повышается за счет увеличения достовернос- и контроля в режиме многоканального сигнатурного анализатора и улучшения каПоследовательный генератор псевдослучайных тестовых наборов.

В данном режиме , , , и схема модуля преобразуется в генератор М-последовательности (фиг. 6).

Параллельный генератор псевдослучайных тестовых наборов.

В данном режиме , , , и схема модуля преобразуется в генератор псевдослучайных чисел, при этом

последующий тестовый набор полностью отГенератор детерминированной последова

тельности. Для случая при , , , на выходах 13.1 - 13.4 устройства (фиг. 8) формируется следующая детерминированная тестовая последовательность.

Q, Q2 Рз Q4

о о о, о

1000 0100

1 0 О

О

1

О 1 1 1 1

0000

Подмножество режимов работы модуля в качестве анализирующей схемы.

Многоканальный сигнатурный анализа РДля обеспечения данного режима , , , . В данном режиме устройство будет формировать значение сигнатуры как результат сжатия ш входных

этом случае , , ,

ва единиц в последовательностях х/, / 1, т.

этом случае , , ,

и эквивалентная схема примет вид (фиг. 11). Содержимое элементов памяти устройства будет определять четность единичных символов в анализируемой последовательности.

Таким образом, данное техническое реще- ние позволяет организовать десять режимов его работы, за счет чего заметно расширяются функциональные возможности устройства.

Кроме того, надежность модуля повышается за счет увеличения достовернос- и контроля в режиме многоканального сигнатурного анализатора и улучшения качества псевдослучайных тестовых последовательностей в режиме генератора.

Формула изобретения

он содержит группу из m сумматоров по модулю два, группу из m элементов ИЛИ-НЕ и элемент И, причем инверсный выход i-ro D-триггера (, m-l) соединен с первьГм входом (i+l)-ro элемента ИЛИ-НЕ группы, вторые входы элементов ИЛИ-НЕ группы объединены и образуют третий вход задания режима модуля, Быход 1 J-X элементов И первой группы (j l,m), выходы J-X элементов ИЛИ-НЕ

Многофункциональный модуль для устройств встроенного контроля, содержащий m D-триггеров, где m - разрядность модуля, первую и вторую группы из m элементов И, сумматор по модулю два, п вхо-vj - , l, - j -- „ „„rvu

дов которого подключены к прямым выхо-10 группы и выходы J-X элементов И второй

дам D-триггеров, номера которых опреде-группы соединены соответственно с первыляются ненулевыми коэффициентами обра-ми, вторыми и третьими ходами j-x

зующего многочлена, синхровходы D-тригге-сумматоров по модулю два вь1ходы

ров объединены и образуют тактовыйкоторых соединены с информационньши

вход модуля,- прямые выходы D-триггеров,5 D-триггеров, прямь.е вь1ходь1

образуют группу информационных выходовкоторых соединены с вторыми входами

модуля, первые входьГ элементов И пер-j-x элементов И второй группы, вторьте

вой группы объединены и образуют пер-входы элементов И первой группы оОвый вход задания режима модуля, первыеразуют группу информационных входов мовходы элементов И второй группы объеди-дуля, (п + 1)-и вход сумматора по моду

нены и образуют второй вход задания ре-20 лю два подключен к шине единично™

жима модуля, отличающийся тем. что, спотенциала, где п - число ненулевь1х

целью расширения функциональных возмож-коэффициентов образующего многочлена,

ностей за счет обеспечения дополнительновыход сумматора по модулю два соеди - режимов параллельного многоканального сиг- нен с первым входом элемента И, второй

натурного анализатора,анализатора четное-25 которого является четвертым входом

ти информационной последовательности, ге-задания режима модуля, выход элемента

нерирования детерминированной последова-И соединен с первым входом первого

тельности и режима регистра сдвига,элемента ИЛИ-Hh группы.

он содержит группу из m сумматоров по модулю два, группу из m элементов ИЛИ-НЕ и элемент И, причем инверсный выход i-ro D-триггера (, m-l) соединен с первьГм входом (i+l)-ro элемента ИЛИ-НЕ группы, вторые входы элементов ИЛИ-НЕ группы объединены и образуют третий вход задания режима модуля, Быход 1 J-X элементов И первой группы (j l,m), выходы J-X элементов ИЛИ-НЕ

vj - , l, - j -- „ „„rvu

0 группы и выходы J-X элементов И второй

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль для устройств встроенного контроля | 1989 |

|

SU1619275A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многоканальный сигнатурный анализатор | 1983 |

|

SU1193678A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Многоканальный сигнатурный анализатор | 1983 |

|

SU1160416A1 |

Изобретение относится к вычислительной технике и предназначено для построения контролепригодных цифровых устройств. Цель изобретения - расширение функциональных возможностей за счет обеспечения дополнительно режимов параллельного многоканального сигнатурного анализатора, анализатора четности информационной последовательности, генерирования детерминированной последовательности и режима регистра сдвига. Модуль содержит M Д-триггеров 1, группы 2 и 3 из M элементов 2И, сумматор 4 по модулю два, M сумматоров 5 по модулю два, M элементов ИЛИ-НЕ 6, элемент И 7. Модуль позволяет организовать десять режимов его работы. 11 ил.

,«

l/Sj

Фиг. 2

Qj

Q

.%

a

о-

Фие.

Фиг.6

lit II

5

2

ITTrnP

ьп

-

riillJ

Фt/г.3

„/

L«

L-Qv

.S

фие.1

6,

fi;

Фиг. 6

x

J) J

| Электроника, 1977, № 5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Electronics letters, 1985, vol | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Опорные части для крестовин, подшипников и т.п. | 1925 |

|

SU856A1 |

Авторы

Даты

1989-12-15—Публикация

1987-05-18—Подача