Изобретение относится к вычислительной технике и может быть использовано в системах тестового и функционального диагностирования цифровых устройств.

Целью изобретения является увеличение быстродействия анализатора.

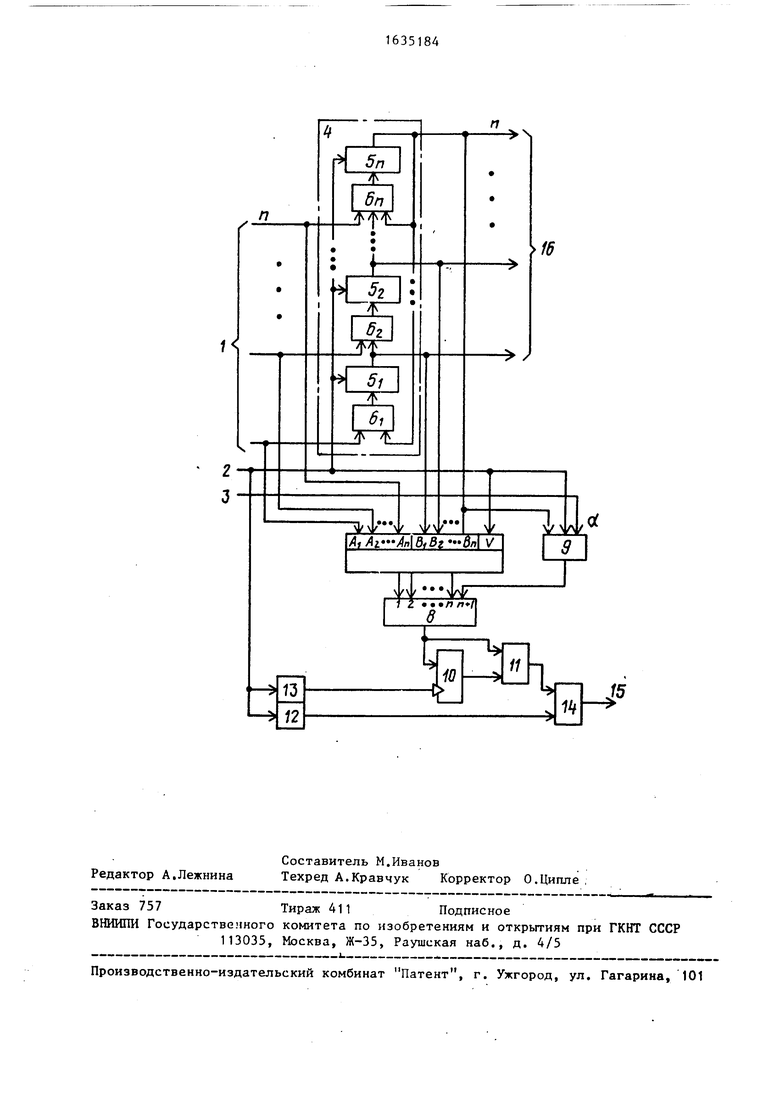

На чертеже приведена схема сигнатурного анализатора.

Анализатор содержит группу информационных входов 1, тактовый вход 2, вход 3 режима работы, формирователь 4 сигнатур, состоящий из триггеров 5( , ..,, 5 Јд и сумматоров 6, , ..., 6п по модулю два, мультиплексор 7, сумматор 8 по модулю два, элемент И 9, триггер 10, сумматор 11 по мопу- лю два, элементы 12 и 13 задержки, элемент И 14, выход 15 сигнала ошибки и группу информационных выходов 16.

Так как формирователь сигнатур может быть реализован по любому образующему полиному, то предварительно перед его работой необходимо по виду используемого полинома осуществить

с

(О

настройку схемы контроля. Такая настройка осуществляется выбором значения коэффициента cvi , которое определяется значением сигнала на входе 3.

Анализатор работает следующим об-- разом.

Перед началом работы анализатора на вход 3 подается О, если количество обратных связей нечетно, или 1, если количество обратных связей четно. Триггеры 5 формирователя 4 и триггер 10 устанавпиваются в нулевое состояние (цегги установки не показаны).

В начале произвольного (i+1)-ro такта триггер 10 хранит значение свертки по модулю два содержимого триггеров 5 предыдущего i-ro такта. На входы 1 подается контролируемая информация в виде вектора длиной п. По фронту сигнала на вхо; с 2 текущая свертка информации заносится в триггеры 5. Одновременно по этому сигналу входная информация поступает на пер(Л

о со ел

оо

Јь

вую группу входов мультиплексора 7 и передается через него на входы сумматора 8. При наличии сигнала 1 на входе 3 состояние n-го триг.гера 5 через элемент И 9 поступает на (п+1)-й вход сумматора 8. Сформированная на выходе сумматора 8 свертка поступает на информационный вход триггера 10. Синхросигнал с входа 2, за- держанный на элементе 13, поступает на тактовый вход триггера 10.

Таким образом, в триггер 10 записывается первая контрольная сумма.

По отрицательному уровню сигнала на входе 2 полученная текущая сигнатура с выходов триггеров 5 поступает на вторую группу входов мультиплексора 7 и передается через него на входы сумматора 8, на выходе которого формируется вторая контрольная сумма. ,При этом на (п+1)-й вход сумматора 8 поступает О. На сумматоре 11 осуществляется сравнение первой и второй контрольных сумм.

В случае появления какой-либо неисправности, приводящей к нарушению правильной работы анализатора, на выходе сумматора 11 фиксируется единичный сигнал, который по задержанному на элементе 12 сигналу через элемент И 14 передается на выход 15 в виде сигнала ошибки.

Предлагаемый анализатор обрабатывает информацию по всем выходам проверяемого объекта.

Формула изобретения

Сигнатурный анализатор, содержащий формирователь сигнатур, первый элемент И, два сумматора по модулю два, два элемента задержки и триггер, первый информационный вход формирователя сигнатур является первым информа- ционным входом анализатора, тактовый

, Q

5 0 5

0

,. -

5

вход формирователя сигнатур объединен с входами первого и второго элементов задержки и является тактовым входом анализатора, группа выходов формирователя сигнатур является группой информационных выходов анализатора, выход первого сумматора по модулю два соединен с D-входом триггера, тактовый вход и выход которого соединены соответственно с выходом первого элемента задержки и первым входом второго сумматора по модулю два, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом второго элемента задержки, выход первого элемента И являемся выходом ошибки анализатора, отличающийся тем, что, с целью увеличения быстродействия, он содержит мультиплексор и второй элемент И, причем информационные входы с второго по n-й формирователя сигнатур являются одноименными входами анализатора, выход первого сумматора по модулю два соединен с вторым входом второго сумматора по модулю два, управляющий вход мультиплексора объединен с первым входом второго элемента И и подключен к тактовому входу анализатора, второй вход второго элемента И является входом режима работы анализатора, третий вход второго элемента И подключен к n-му выходу формирователя сигнатур, где п разрядность сигнатуры, первая и вторая группы информационных входов мультиплексора соединены соответственно с группой информационных входов и группой выходов формирователя сигнатур, п входов первого сумматора по модулю два соединены с выходами мультиплексора, выход второго элемента И соединен с (п+1)-м входом первого сумматора по модулю два.

П

Н 5п Ж

бп

J2

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Сигнатурный анализатор | 1988 |

|

SU1587509A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1451772A1 |

| Сигнатурный анализатор | 1985 |

|

SU1247876A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах тестового диагностирования. Цель изобретения - увеличение быстродействия. Анализатор содержит формирователь сигнатур, два сумматора по модулю два, мультиплексор, два элемента задержки, два элемента И и триггер. Анализатор позволяет обрабатывать информацию, поступающую одновременно по нескольким каналам, при этом обеспечивается контроль за прг.зтыюстью процесса формирования сигнатуры. 1 ил.

О

JL

ОТ

1/Ф

A, V

у л

| Формирователь сигнатур с контролем | 1988 |

|

SU1553975A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1985 |

|

SU1247876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,(54) СИГНАТУРНЫЙ АНАЛИЗАТОР | |||

Авторы

Даты

1991-03-15—Публикация

1989-03-27—Подача