просные входы 4.1, 4.2-4.N и запросный выход 3 коммутатора, разрешающий вход 5 и разрешающие выходы 6.1, 6.2-6.N, информационные входы 7.1, 7.2-7.N, адресные входы 8.1, 8.2-8.N, адресные выходы 9.1, 9.2-9.К, уста- новочный вход 10 и управляющие вхо-.

10

15

I

Изобретение относится к коммутаионной технике, автоматике, вычисительной технике и может быть использовано в системах поиска и об- служивания запросов, а также дпя установления информационной связи между множествами источников и при- емников информации.

Цель изобретения - повьппение быстродействия за счет уменьшения времени поиска сигнала запроса и установления связи входов коммутатора с выходом.

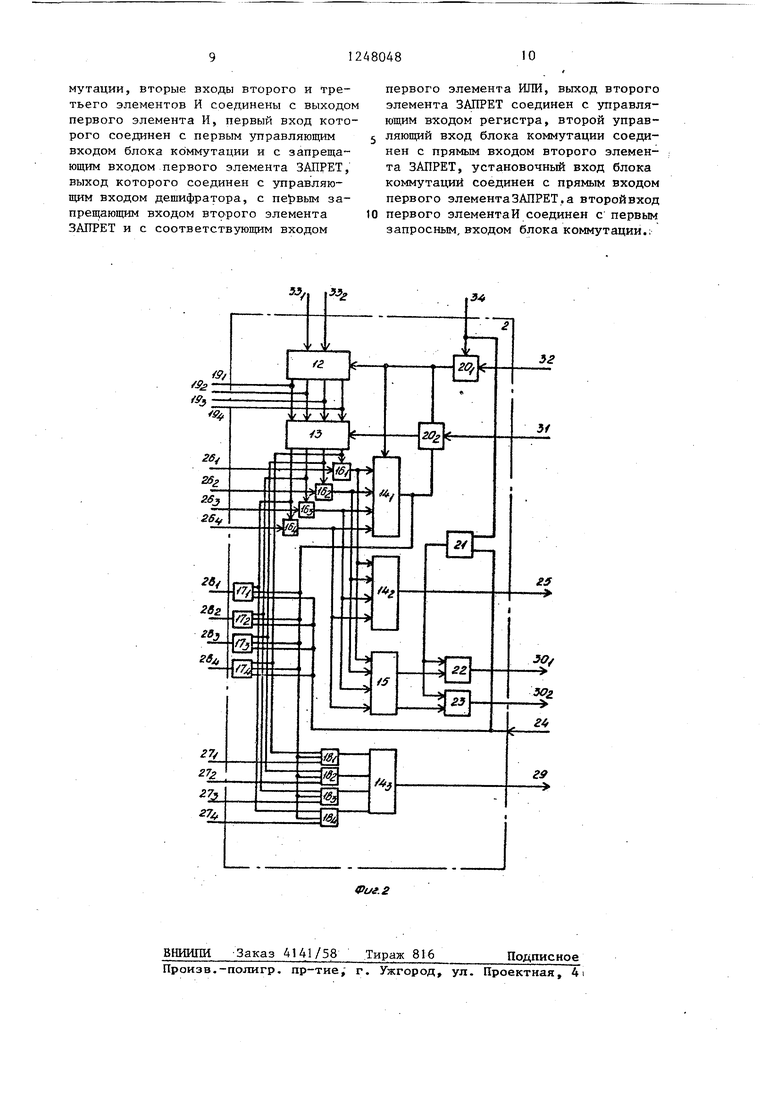

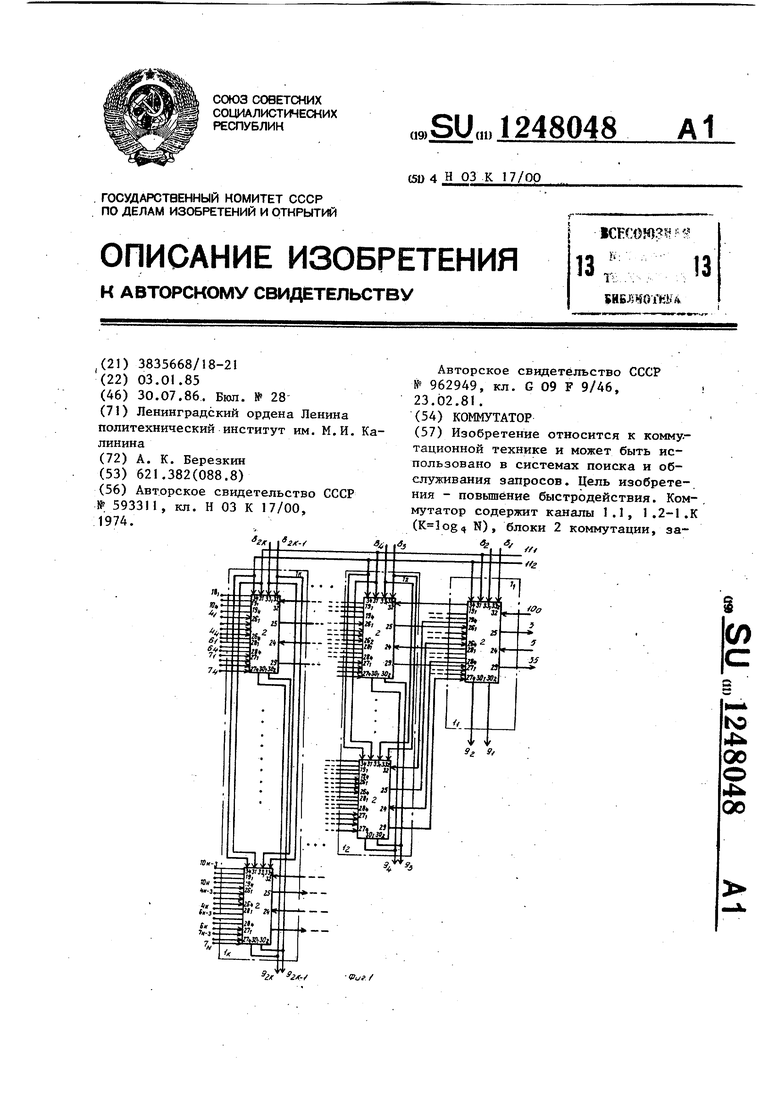

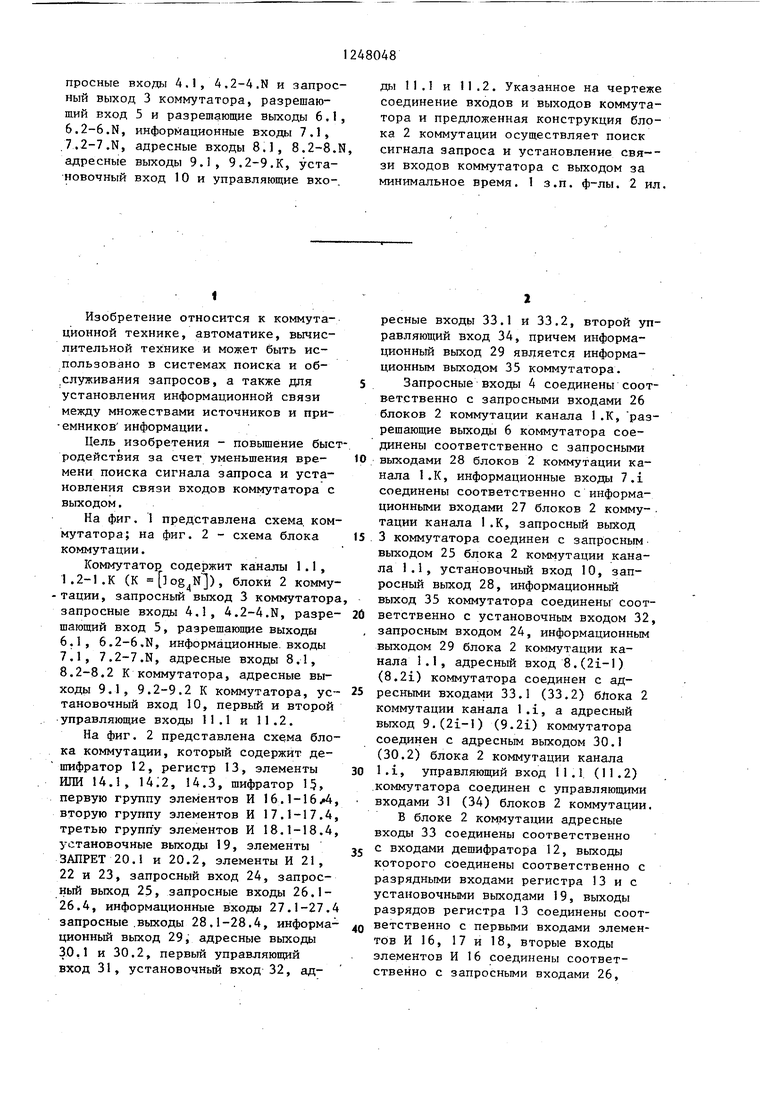

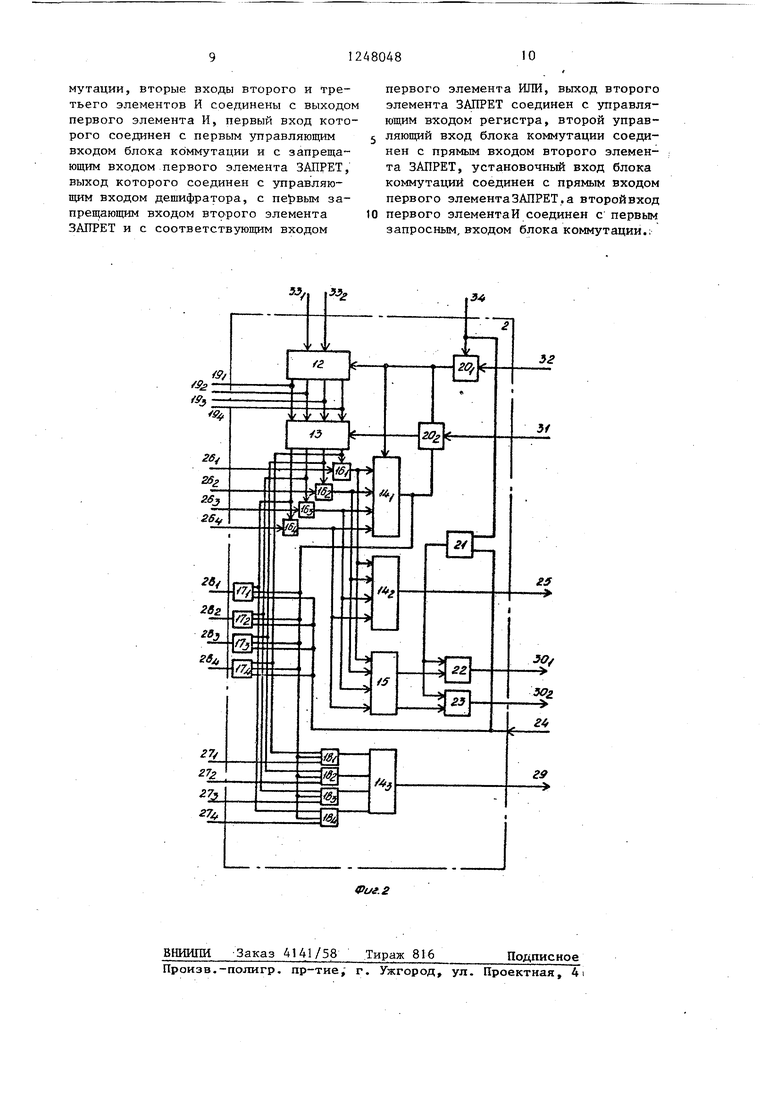

На фиг. 1 представлена схема, коммутатора; на фиг. 2 - схема блока коммутации.

Коммутатор содержит каналы I.I, 1.2-1.К (К ), блоки 2 комму- тации, запросный выход 3 коммутатора, запросные входы 4.1, 4.2-4.N, разре- 2б шающий вход 5, разрешающие выходы 6.1, 6.2-6.N, информационные, входы 7.1, 7.2-7.N, адресные входы 8.1, 8.2-8.2 К коммутатора, адресные выходы 9.1, 9.2-9.2 К коммутатора, ус- 25 тановочный вход 10, первый и второй управляющие входы 11.1 и 11.2.

На фиг. 2 представлена схема блока коммутации, который содержит дешифратор 12, регистр 13, элементы ИЖ 14.1, 14:2, 14.3, шифратор 15) первую группу элементов И 16.1-16/4, вторую группу элементов И 17.1-17.4, третью группу элементов И 18.1-18.4, установочные выхода 19, элементы ЗАПРЕТ 20.1 и 20.2, элементы И 21, 22 и 23, запросный вход 24, запросный выход 25, запросные входы 26.1- 26Л, информационные входы 27.1-27.4 запросные .выходы 28.1-28.4, информа- о ционный выход 29, адресные выходы 30.1 и 30.2, первый управляющий вход 31, установочный вход 32, ад30

35

ды 11,1 и 11.2. Указанное на чертеже соединение входов и выходов коммутатора и предложенная конструкция блока 2 коммутации осуществляет поиск сигнала запроса и установление свя-- зи входов коммутатора с выходом за минимальное время. 1 з.п. ф-лы. 2 ил.

ресные входы 33.1 и 33.2, второй управляющий вход 34, причем информа- ционньШ выход 29 является информационным выходом 35 коммутатора.

Запросные входы 4 соединены соответственно с запросными входами 26 блоков 2 коммутации канала 1.К, разрешающие выходы 6 коммутатора соединены соответственно с запросными выходами 28 блоков 2 коммутации канала 1.К, информационные входы 7.1 соединены соответственно с информа- ционньми входами 27 блоков 2 комму- . тации канала 1.К, запросный выход 3 коммутатора соединен с запросным выходом 25 блока 2 коммутации канала 1.1, установочный вход 10, запросный выход 28, информационный выход 35 коммутатора соединены соответственно с установочным входом 32, запросным входом 24, информационным выходом 29 блока 2 коммутации канала 1.1, адресный вход 8.(21-1) (8.21) коммутатора соединен с адресными входами 33.1 (33.2) бйока 2 коммутации канала 1.1, а адресный выход 9.(21-1) (9.21) коммутатора соединен с адресным выходом 30.1 (30.2) блока 2 коммутации канала 1.1, управляющий вход 11.1. (11.2) .коммутатора соединен с управляющими входами 31 (34) блоков 2 коммутации.

В блоке 2 коммутации адресные входы 33 соединены соответственно с входами дешифратора 12, выходы которого соединены соответственно с разрядными входами регистра 13 и с установочными выходами 19, выходы разрядов регистра 13 соединены соответственно с первыми входами элементов И 16, 17 и 18, вторые входы элементов И 16 соединены соответственно с запросными входами 26,

3

запросные выходы 28 соединены соответственно с выходами элементов И 1 выходы которых соединены соответственно, с входами элемента ИЛИ 14.3 выход которого соединен с информационным выходом 29, запросный вход 24 соединен с третьими входами элементов И 17 и с вторым входом эле- мента И 21, выходы элементов И 16 соединены соответственно с входами элемента ЮШ 14.1, входами элемента ИЛИ 14.2 и с входами шифратора 15, выходь которого соединены с вторыми входами элементов И 22 и 23 соответственно , выход элемента ИЛИ 14.1 соединен с вторыми входами элементов И 17 и с вторыми входами элементов И 18, а также с вторым запрещающим входом элемента ЗАПРЕТ 20.2, выход которого соединен с управляющим входом регистра 13, выход элемента ИЛИ 14.2 соединен с запросным выходом 25 i установочный вход 32 соединен с вхо- дом элемента ЗАПРЕТ 20.1, выход которого соединен с управляющим входом дещифратора 12, первым запрещающим входом элемента ЗАПРЕТ 20.2 и с соответствующим входом элемента ИЛИ 14.1, управляющий вход 34 соединен с запрещающим входом элемента ЗАПРЕТ 20.1 и с соответствующим входом элемента И 21, выход которого соединен с первыми входами тов И 22 и 23, выходы которых соединены соответственно с адресными выходами 30.1 и 30.2, управляющий вход 31 соединен с входом элемента ЗАПРЕТ 20.2, установочный вход 32 соединен с прямым входом элемента ЗАПРЕТ 20.1.

Коммутатор работает следующим образом.

Подключение информационных входов 7.1 к информационному выходу 35 коммутатора осуществляется как по адресу входа, устанавливаемому на адресных входах 8, так и в результате нахождения сигнала запроса на соответствующем запросном входе 4. Сигналы запроса, поступая на запросные входы 4 коммутатора от источников, опращиваются в блоках 2 коммутации канала 1.К и передаются на их запросные вькоды 25, причем в каждом блоке 2 коммутации канала 1.1, на запросные входы 26 которых поступил запросный сигнал, фиксируется вход, сигнал запроса с которо480484

го передан на запросный выход 25.

Б следующем канале 1. (К-1) каждый . блок 2 коммутации также опращивает

запросные входы 26, которые связаны 5 с запросными выходами 25 соответствующих блоков 2 коммутации канала 1.К. Таким образом, число блоков 2 коммутации, осуществляющих опрос и выбор сигналов запроса в каждом 10 последующем канале, уменьшается в 4 раза, что соответствует наличию К log+NJ каналов в коммутаторе, причем с выхода 25 блока 2 коммутации канала 1.1 сигнал з апроса посту- 15 пит на запросный выход 3 коммутатора. Поиск и передача поступившего на любой из запросных входов 4 коммутатора сигнала запроса на выход 3 будет осуществляться за минимальное 20 время. Это следует из рассмотрения времени опроса и передачи сигнала запроса с запросных входов 4 на выход 3 как функции числа К каналов 1.1 и числа М запросных входов 26 25 в блок 2 коммутации. Пусть время опроса одного входа 26 в блоке 2 коммутации и передача сигнала запроса с входа 26 на выход 25 равно t . Тогда время поиска и передачи сигиа- 0 ла запроса на выход 3 коммутатора в худшем случае составит T(MK+K) i « (М+1) ()T. Ближайшее целое М, при котором эта функция достигает минимума, равно 4. Учитывая, что среднее время поиска и обнаружения

М

сигнала запроса равно Т(- К+К),

то минимальное среднее время Т достигается также при .

0 Опрос запросных входов 26 в блоках 2 коммутации осуществляется под управлением синхроимпульсов, поступающих на вход 11.2 коммутатора и далее на входы 31 блоков 2 коммута ции.

По сигналу на входе 11.1 осуществляется выдача на адресные выходы 9 коммутатора кода номера запросного входа 4, сигнал с которого

0 передан на выход 3 коммутатора. При отсутствии сигнала на входе 11.1 воспринимается сигнал на установо - ном входе 10.9, в результате чего, при единичном значении сигнала на

5 входе 10.0, код адреса на входах 8 обеспечит подключение соответствующего запросного входа 4 к выходу 3. В канале I.1 сигнал установки с

входа 10.0 коммутатора пройдет на вход 32 блока 2 коммутации первого канала и далее на один из установочных выходов 19, определяемый разрядами адреса, поступившими на два первых адресных входа 8.1 и 8.2-. Во втором канале 1.2 установочный сигнал пройдет на один из выходов 19 блока 2 коммутации, который соответствует выходу 19 блока 2 коммутации канала 1.1, куда поступил сигнал установки. Таким образом в каждом канале 1 сигнал установки будет поступать только на вход 32 одного блока 2 коммутации и передаваться на один его выход 19, определяемый значением двух адресных входов 8, соответствующих этому каналу. Б результате прохождения всех каналов 1 сигнал установки в соответствии с кодом адреса на входах В обеспечит путь прохождения сигналов с входа 4, соответствующего коду адреса на входах 8, на выход 3 коммутатора. Одновременно устанавливается путь прохождениясигналов с информационного входа 7.1, соответствующего адресу на входах 8, на информационный вход 35 коммутатора, а также путь прохождения сигналов с входа 5 на выход 6, соответствующий адресу на входах 8i -Сигнал запрса на входе 4 обеспечивает удержани связи между соответствующими выходом 6, входом 7 и входом 5, выходом 35, как и в случае опроса сигналов запроса на входах 4 и передачи его на выход 3.. .

Блок 2 коммутации по синхросигналам на входе 31 осуществляет опрос запросных входов 26 путем последовательного сдвига по кольцу в регистре 13 одного единичного значения разряда. Так как выходы разрядов регистра 13 связаны с входами элементов И 16, то при наличии сигналов запроса на входах 26, один из . них пройдет, на выход одного элемент И 16 и далее на выход элемента ИЛИ .14, и далее на запрещающий вход элемента ЗАПРЕТ 20.2, что приведет к прекращению сдвига и фиксации положения едд1ничного разряда регистра 13. Кроме того, сигнал с выхода элемента ИЛИ 14.1 откроет по одному входу элементов И 17 и элементов И 18, а так как по другим входам эти элементы связаны с выходами

o

5

разрядов регистра 13, то с запросного входа 24 сигнал будет передаваться на соответствующий выход 28, а на. выход 29 сигнал будет переда ваться с соответствующего входа 27. Одновременно сигнал запроса поступит на запросный выход 25. При наличии установочного сигнала на входе 32 и отсутствии сигнала на управляющем входе 34 |)азряды регистра 13 устанавливаются в соответствии с кодом на адресных входах 33.1 и 33.2. Одновременно установочный сигнал проходит на соответствующий выход 19. Так как сдвиг регистра при этом не осуществляется, то происходит фиксированное пoдкJГoчeниe запросного входа, который соответствует коду на

Q входах 33, к выходу 25, а также вхо- да 27 к вьпсоду 29 и,входа 24 к соот- ветст ующему выходу 28. По запросному сигналу на входе 24 и наличии- управляющего сигнала на входе 34

5 на выходы 30 поступает код адреса одного из четырех входов 26, сигнал запроса с которого найден путем опроса на.элементе И 16. Элементы И 22, 23 являются согласующими, т.е.

- позволяют объединять выхода по схеме проводного РШИ.

Таким образом, коммутатор имеет более высокое быстродействие, так как осуществляет поиск сигнала запро- са и установление связи входов коммутатора с выходом за минимальное время, а именно за время Т 5 (log,N)t.

40

Формула изобретения

1. Коммутатор, содержащий N запросных входов, каналы, каждый из которых включает блоки коммутации, причем второй и третий запросные входы каждого блока коммутации каждого i-ro канала, кроме последнего, соединены с первыми запросными выходами соответствующих блоков комму- таци;и (i+l)-ro канала, а второй и третий запросные входы блоков коммутации последнего канала соединены соответственно с соответствующими запросными входами коммутатора, второй и третий запросные выходы каж- дрго блока коммутации каждого i-ro канала, кроме последнего, соединень ; с первыми запросными входами соответствующих блоков коммутации

(i+l)-ro канала, второй и третий запросные выходы блоков коммутации последнего канала соединены с соответствующими разрешающими выходами коммутатора, отличающий- с я тем, что, с целью повьшения быстродействия, четвертый и пятый запросные входы каждого блока коммутации каждого i-ro канала, где ,2, (xj - ближайшее большее целое к х), кроме последнего, соединены с первыми запросными выходами соответствующих блоков коммутации (i+l)-ro канала, а четвертый и пятый запросные входы блоков коммутации последнего канала соединены соответственно с соответствующими запросными входами коммутатора, четвертый и пятый запросные выходы каждого блока коммутации каждого i-ro канала, кроме последнего, соединены соответственно с первыми запросными входами соответствующих блоков коммутации (i+l)-ro канала, четвертый и пятый запросные выходы блоков коммутации последнего канала соединены соответственно с соответствующими разрещающими выходами коммутатора, первьй, второй, третий и четвертый установочные выходы каждого блока коммутации i-ro канала, кроме последнего, соединены с установочкы т входами соответствующих блоков коммутации (i+l)-ro канала, первый, второй, третий и четвертый информационные входы каждого блока коммутации i-ro канала, кроме последнего, соединены соответственно с информационными выходами соответствующих блоков коммутации (ifl)-ro канала, а для последнего канала - с соответствующими информационными входами коммутатора, разрешающий вход коммутатора, информационный выход коммутатора, вход установки коммутатора соединены соответственно с первым запросным выходом, первым запросным входом, информационным выходом, входом установки блока коммутации первого канала, а вторые адресные входы блоков коммутации каждого i-ro канала соединены с (2i-l)-M адресным

входом коммутатора, первые адресные выходы блоков коммутации каждого i-ro канала соединены с 2i-M адресным выходом коммутатора, первые адресные входы коммутатора каждого i-ro кана-, ла соединены с 2i-M адресным входом

10

15

0

5

0

5

0

5

0

коммутатора, вторые адресные выходы блоков коммутации соединены с (2i- -I )-м адресным выходом коммутатора, первые управляющие входы блоков коммутации соединены с первым управляющим входом коммутатора, вторые управляющие входы блоков коммутации соединены с вторьв-j управляющим входом коммутатора.

2. Коммутатор тто п. 1 , о т- л и - чающийся тем, что блок коммутации содержит первую, вторую и третью группы элементов И, первый, второй и третий элементы ИЛИ, регистр, дешифратор, шифратор, первый и второй элементы ЗАПРЕТ, первый, второй и третий элементы И, причем первый и второй адресные входы блока коммутации соединены соответственно с входами дешифратора, выходы которого соединены соответственно с входами разрядов регистра и с установочными выходами блока коммутации, выходы разрядов регистра соединены соответственно с первыми входами первой, второй и третьей группы элементов И, второй, третий, четвертый и пятый запросные входы блока коммутации соедииены соответственно с вторыми входами элементов И первой группы, выходы которых соединены соответственно с входами первого и второго элементов ИЛИ и с входами шифратора, .второй, третий, четвертый и пятый запросные вьрсоды блока коммутации соединены соответственно с выходами элементов И второй группы, вторые входы которых соединены с первь1М запросным входом блока коммутации, а третьи входы соединены с выходом первого элемента ИЛИ и с вторым запрещающим входом второго элемента ЗАПРЕТ, информационные входы блока коммутации соединены соответственно с вторыми входами элементов И третьей группы, третьи входы которых соединены с выходом первого элемента ИЛИ, а выходы соединены соответственно с входами третьего элемента ИЛИ, выход которого соединен с информационным выходом блока коммутации, выход второго элемента ИЛИ соединен с первым запросным выходом блока коммутации, выходы шифратора соединены соответственно с первьгми входами второго и третьего элементов И, выходь: которых соединены соответственно с адресными выходами блока коммутации, вторые входы второго и третьего элементов И соединены с выходом первого элемента И, первый вход которого соединен с первым управляющим входом блока коммутации и с запрещающим входом первого элемента ЗАПРЕТ, выход которого соединен с управляющим входом дешифратора, с пе рвын запрещающим входом второго элемента ЗАПРЕТ и с соответствующим входом

первого элемента ИЛИ, выход второго элемента ЗАПРЕТ соединен с управляющим входом регистра, второй управ5 ляющий вход блока коммутации соединен с прямым входом второго элемента ЗАПРЕТ, установочный вход блока коммутаций соединен с прямым входом первого элементаЗАПРЕТ.а второйвход

10 первого элементаИ соединен с первым запросным, входом блока коммутации.:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Многоканальное устройство для управления очередностью запросов | 1982 |

|

SU1061143A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство для управления обслуживанием запросов | 1991 |

|

SU1824637A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Децентрализованная система коммутации | 1985 |

|

SU1282150A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1985 |

|

SU1401459A1 |

| Децентрализованная система коммутации | 1985 |

|

SU1282149A1 |

| Устройство для многоуровневой коммутации процессоров и блоков памяти | 1983 |

|

SU1213474A1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

Изобретение относится к комму.- тационной технике и может быть использовано в системах поиска и обслуживания запросов. Цель изобретения - повышение быстродействия. Коммутатор содержит каналы 1.1, 1.2-1 .К ( N), блоки 2 коммутации, за- Ог . W ю 4 00 о 4 00 fuf. f

3

| Приспособление для предотвращения изгибания вагонных шеек при распрессовке колесных пар | 1940 |

|

SU59331A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальное устройство для приоритетного обслуживания запросов | 1981 |

|

SU962949A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-03—Подача