1

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства умножения и деления сне- циализированного вычислителя.

Цель изобретения - повышение быстродействия устройства.

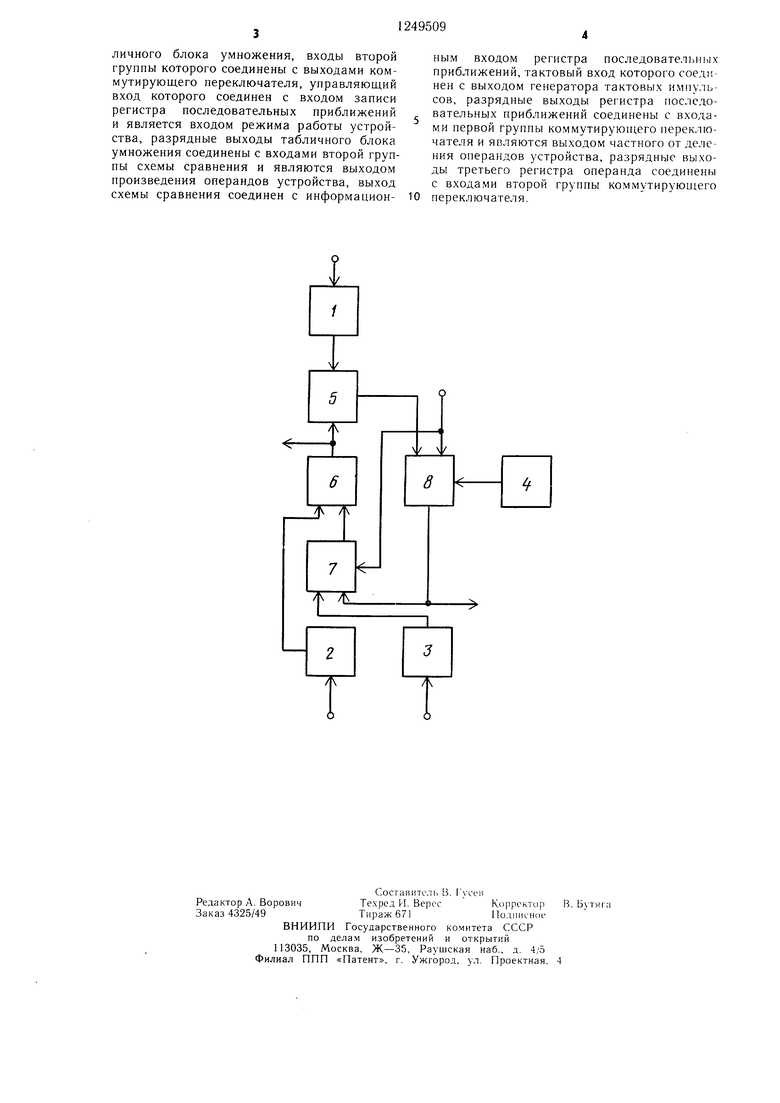

На чертеже представлена функциональная схема устройства.

Устройство содержит первый, второй и третий регистры 1-3 операндов, генератор 4 тактовых импульсов, схему 5 сравнения, табличный блок 6 умножения, коммутирующий переключатель 7 и регистр 8 последовательных приближений, причем информационные входы первого, второго, и третьего регистров 1-3 операндов являются соответственно входами делимого (множимого), делителя и множителя устройства, разрядные выходы регистра 1 соединены соответственно с входами первой группы схемы 5 сравнения, входы второй груины которой соедипе1п.1 соответственно с разрядными выходами табличного блока 6 умножения, являются выходом произведения операндов устройства, а выход схемы 5 сравнения соединен с информационным входом регистра 8 ноеледовательных приближений, вход записи которого соединен с управляющим входом коммутирующего переключателя 7 и является входом устройства, выход генератора 4 тактовых импульсов соединен с тактовым входом регистра 8 последовательных приближений, разрядные выходы которого соединены соответственно с входами первой группы коммутируюп;его переключателя 7 и являются выходом частного от деления операндов устройства, разрядные выходы регистра 3 соединены соответственно с входами второй группы коммутируюпхего переключателя 7, разрядные выходы которого соединены соответственно с входами нервой грунпы табличного блока 6 умножения, входы второй 1-руппы которо о соединенЕ) соответственно с разрядными выходами регистра 2.

стройство работает следую1цим образом.

В режиме л,е 1ения сигна.л зануска, гю- стунаюпдий па унравля1ОН1.ий вход ко.ммути- рующего переключателя 7, подключает к входам первой группы табличпо1Ч) блока 6 умножения выход регист1)а S п()следователыпэ1х приближе1П1Й. На входы второй таб- личпого блока 6 умножения с регистра 2 поступает дслите.пь.

Первым тактовым импул 1сом Hoc;ie зануска устройства на выходе регистра 8 последовательных приближений Стапав;1ивает- ся двоичный код 011 ... 1, ра:;.рядиость которого определяется максимальным числом разрядов частного.

Табличный блок б умножении осуществляет перемножение делителя па чис.;1О с выхода коммутирующего переключателя 7. Результат умножения с выхода табличного блока 6 умножения с)авнивается на схеме 5 сравнения с делимым, поступаюн,им с реV

49509

гистра

1 (делимого) на входы первой группы схемы 5 сравнения.

Если результат умножения меньше делимого, схема 5 сравнения формирует выходной сигнал уровнем логической единицы, по- 5 ступающий на инфор.мационный вход регистра 8 последовательных приближений (если результат умножения больше или равен делимому, на информационный вход регистра 8 последовательных приближений поступает 0 сигнал уровнем логического нуля).

В начале второго такта происходит запись в старший разряд регистра 8 последовательных приближений сигнала, поступившего на его информационный вход, и установка следующего разряда в нуль, т. е. 15 устанавливается двоичный код в зависимости от результата сравнения 1011 ... 1 или ООП ... 1.

Этот код снова умножается на делитель, результат умножения сравнивается с делимым и онределяется в следующий разряд двоичного кода частного и т. д.

В режиме умножения коммутирующий переключатель 7 подключает к входам первой группы табличного блока 6 умножения множитель с регистра 3 (множителя). На 25 входы второй грунпы табличного блока 6 умножения с регистра 2 поступает .множимое. Результат умножения снимается с выхода табличного блока 6 умножения.

Время вычисления Г5 режиме умножения определяется только задержками элемента- 30 ми табличного умножителя и составляет, .например, при разрядности двоичного кода множимого и множителя, равной восьми, 100--150 НС. В режиме деления время вычисления частного онределяется разрядностью частного.

3.S Таким образом, положительный технико- экономический эффект устройства состоит в существенном увеличении его быстродействия.

Формула изобретения

20

Устройство для умножения-деления, содержащее нервый и второй регистры операндов, генератор тактовых импульсов, схему сравнения, умножитель операндов и коммутирующий переключатель, причем информационные входы первого регистра операнда являются входами делимого устройства, разрядные выходы первого регистра операн- .la соединены с входами первой группы схе.мы сравнения, отличающееся те.м, что, с целью повьнпения быстродействия устройства, в пего введень регистр последовательных приближений и третий регистр операндов, а ум- ножите.пь операндов выполнен в виде таб- .личного блока умножения, причем информационные входы второго и третьего регистров операндов являются входами де.тителя и множителя устройства соответственно, разрядные выходы второго регистра операнда соединены с входа.ми нервой группы таб

личного блока умножения, входы второй группы которого соединены с выходами коммутирующего переключателя, управляющий вход которого соединен с входом записи регистра последовательных приближений и является входом режима работы устройства, разрядные выходы табличного блока умножения соединены с входами второй группы схемы сравнения и являются выходом произведения операндов устройства, выход схемы сравнения соединен с информацион

ным входом регистра последовательных приближений, тактовый вход которого соединен с выходом генератора тактовых импуль сов, разрядные выходы регистра последовательных приближений соединены с входами первой группы коммутируюп1,его переключателя и являются выходом частного от деления операндов устройства, разрядные выходы третьего регистра операнда соединены с входами второй группы коммутируюп1его переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Вычислительное устройство | 1979 |

|

SU794635A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для сопряжения с микроЭВМ | 1986 |

|

SU1709322A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано, в частности, в качестве устройства деления и умножения в специализированном вычислителе. Целью изобретения является повышение быстродействия устройства. Устройство содержит генератор тактовых импульсов, регистр делителя (или множимого), коммутирующий переключатель, регистр делимого, схему сравнения, регистр последовательных приближений, табличный блок умножения и регистр множителя. В режиме деления устройство осуществляет последовательное умножение делителя на число, поступающее через коммутирующий переключатель с регистра последовательного приближения, и сравнение полученного произведения с дели.мым. В режиме умножения устройство перемножает с помощью табличного блока умножения операнды, находящиеся в регистрах множимого и множителя. 1 ил. ISD 4 СО СЛ

| Множительно-делительное устройство | 1978 |

|

SU813419A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1979 |

|

SU794635A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1985-01-29—Подача