Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных процессорах.

Целью изобретения является повышение быстродействия при выполнении операции деления.

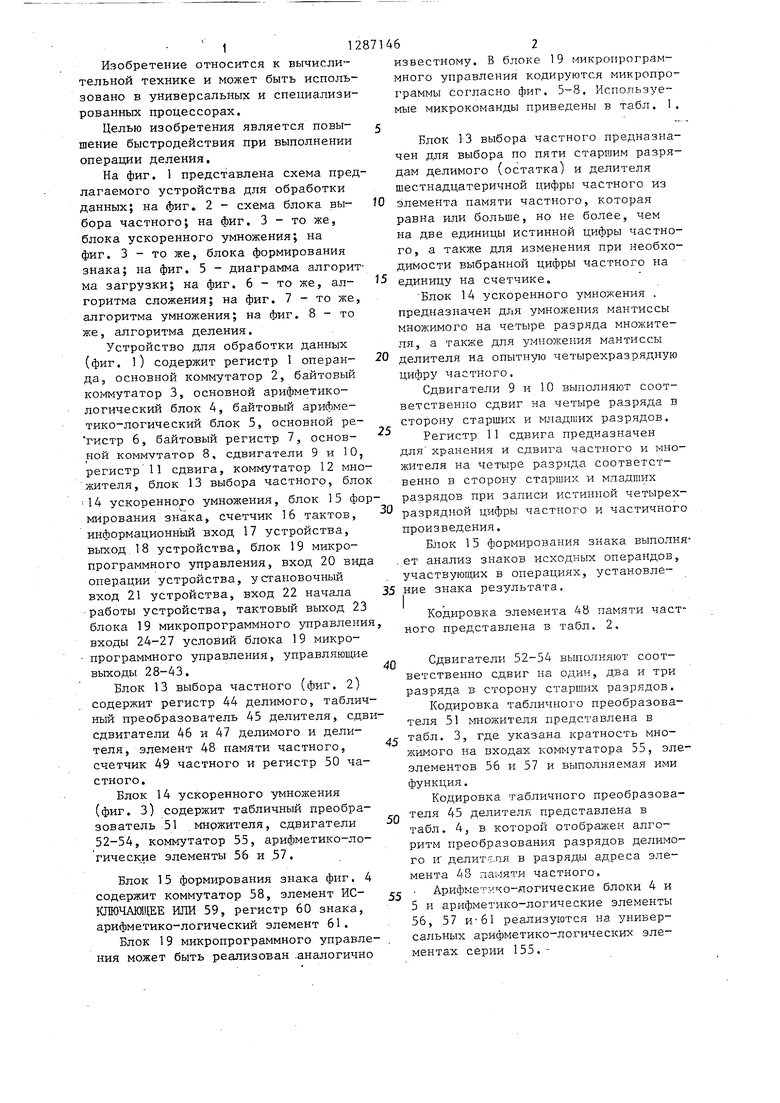

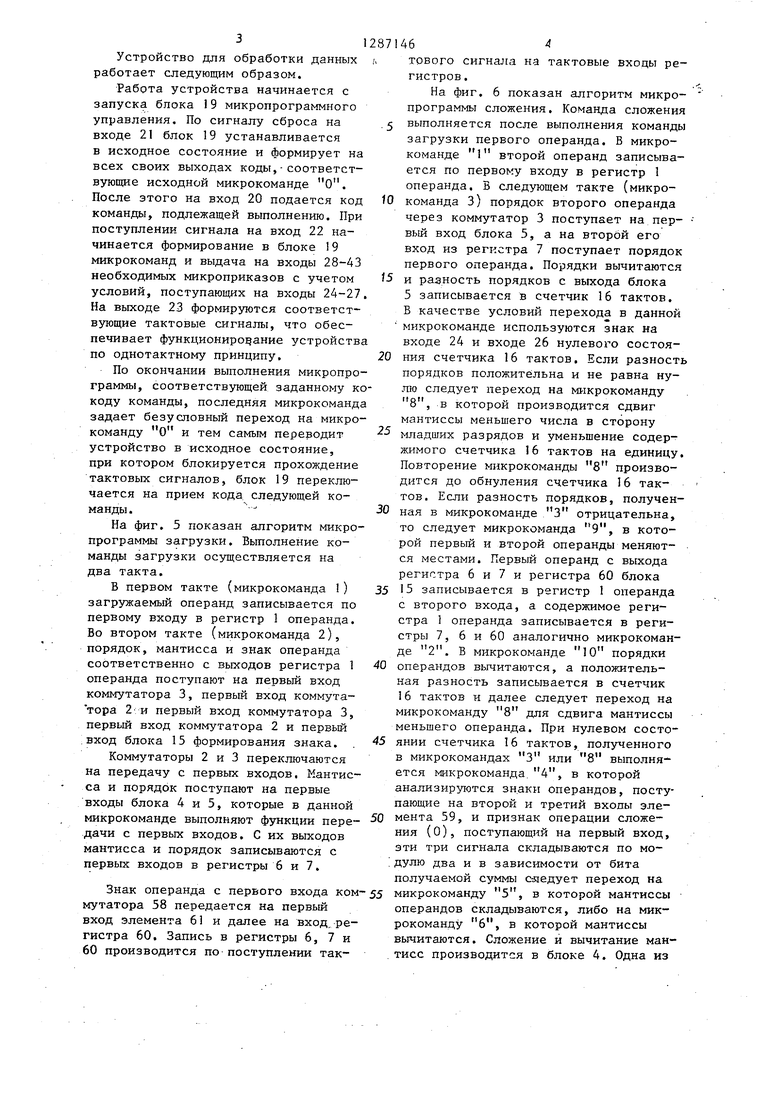

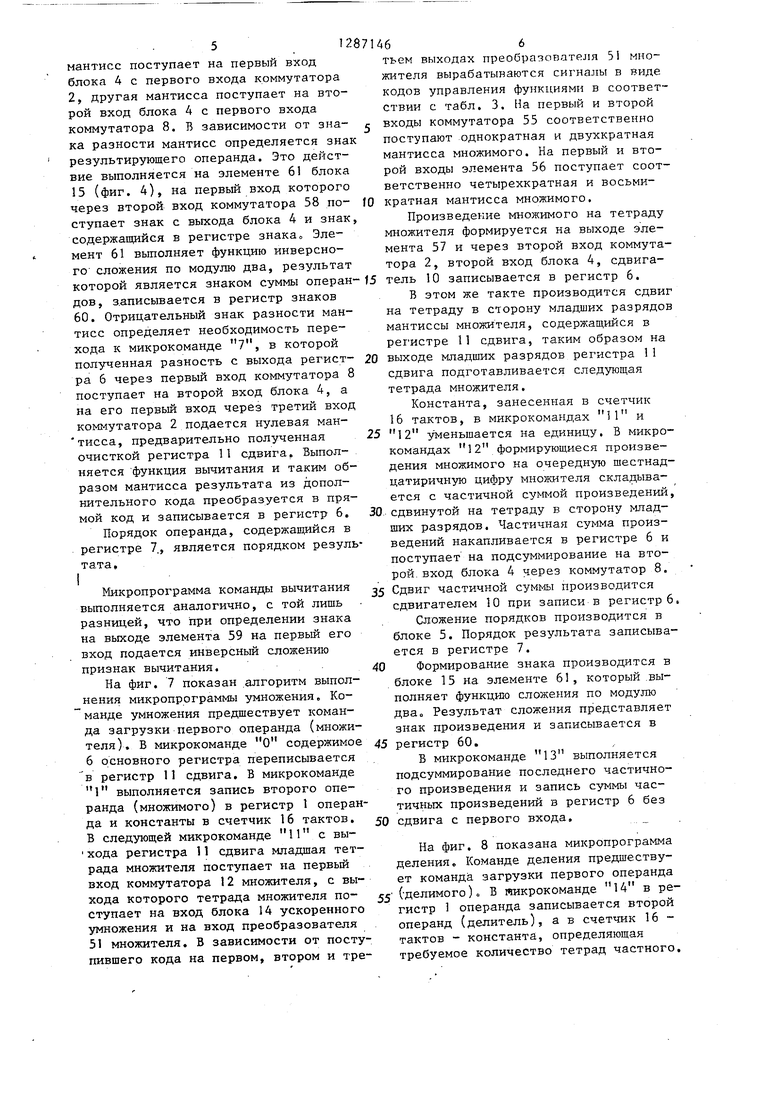

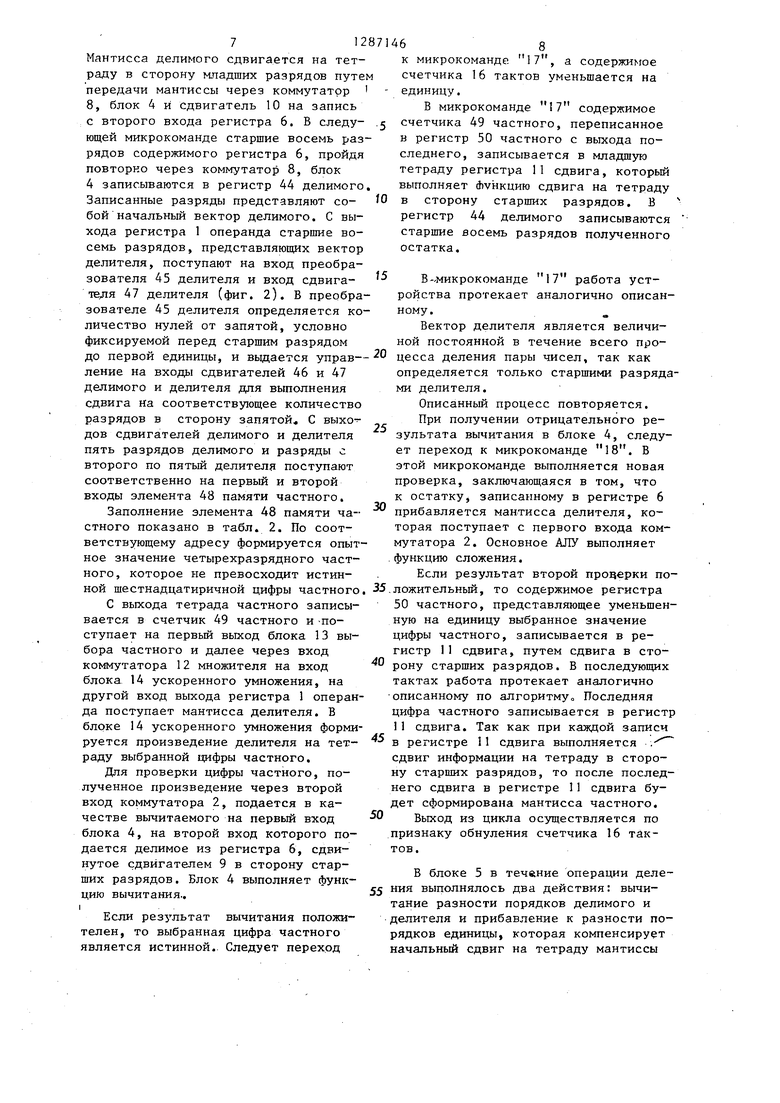

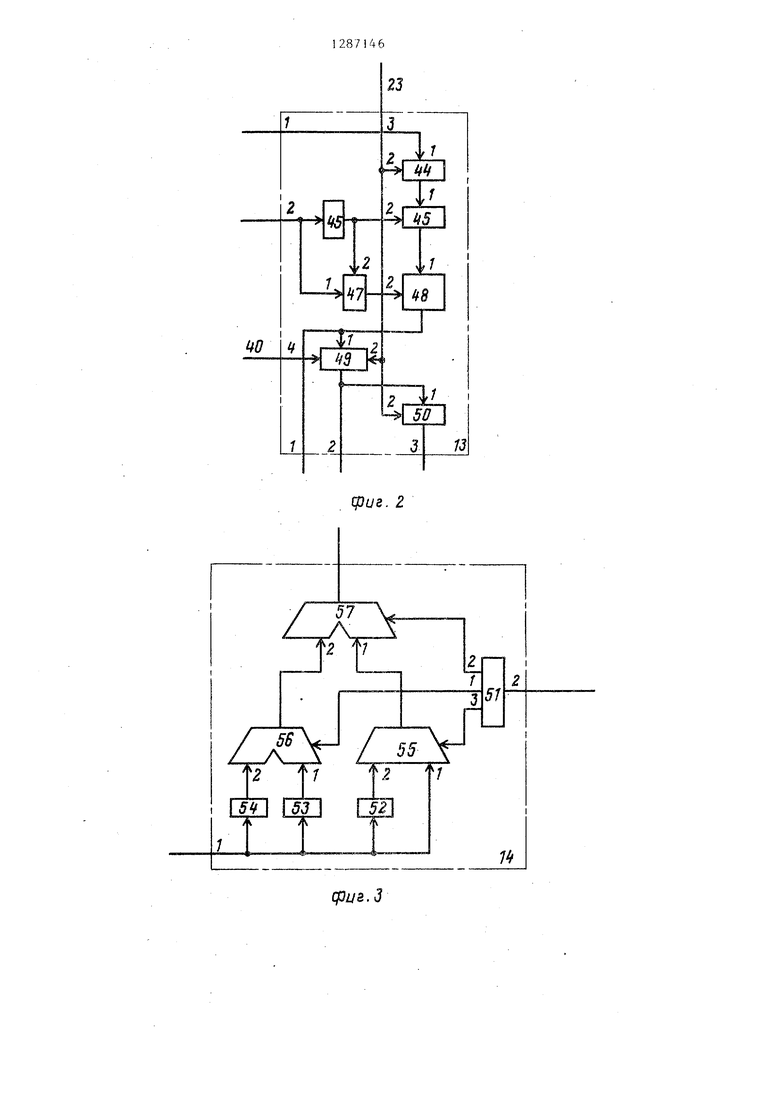

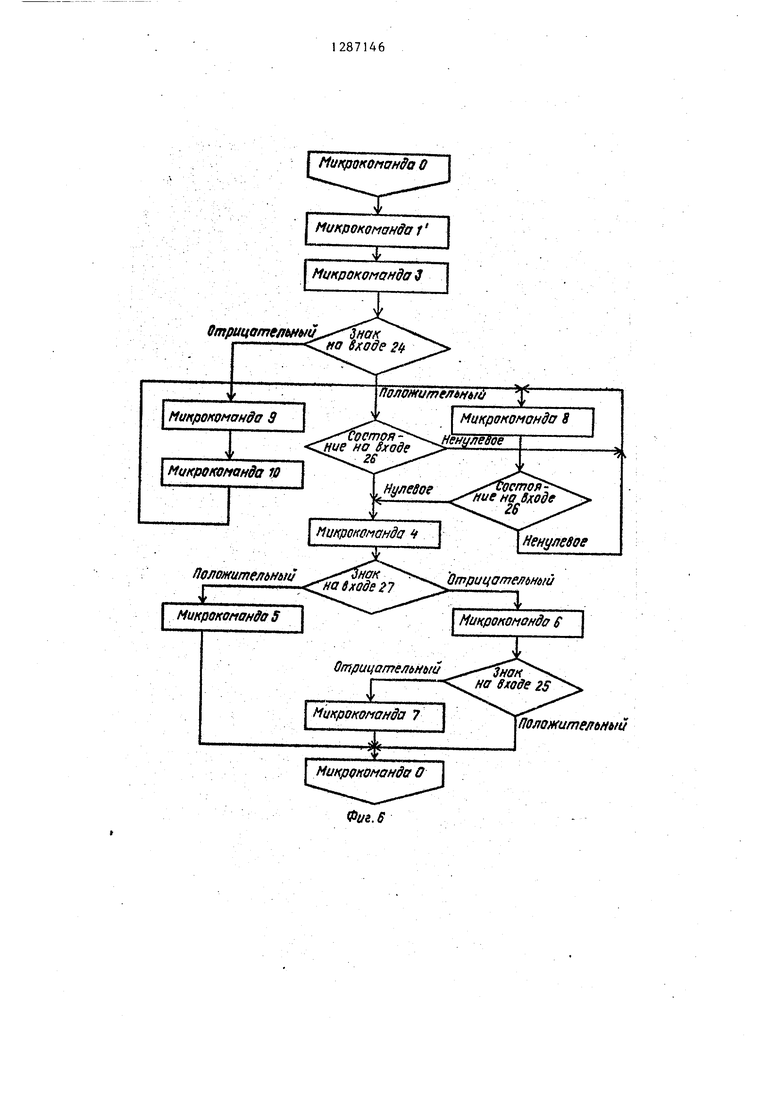

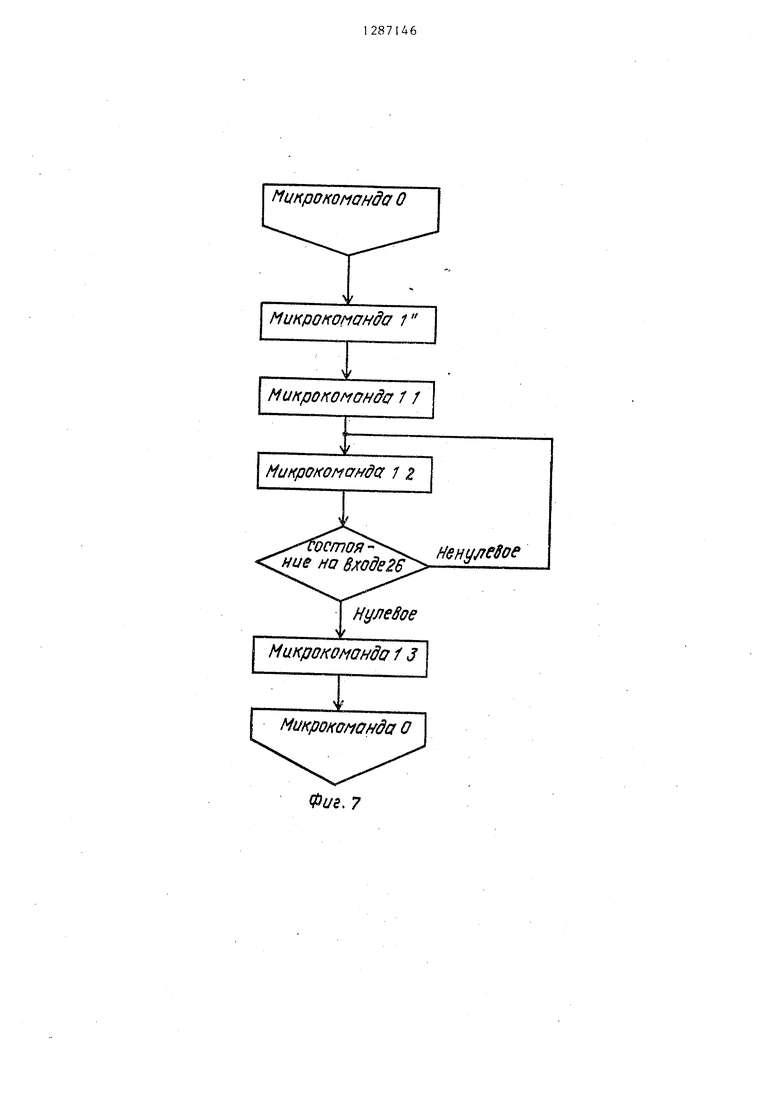

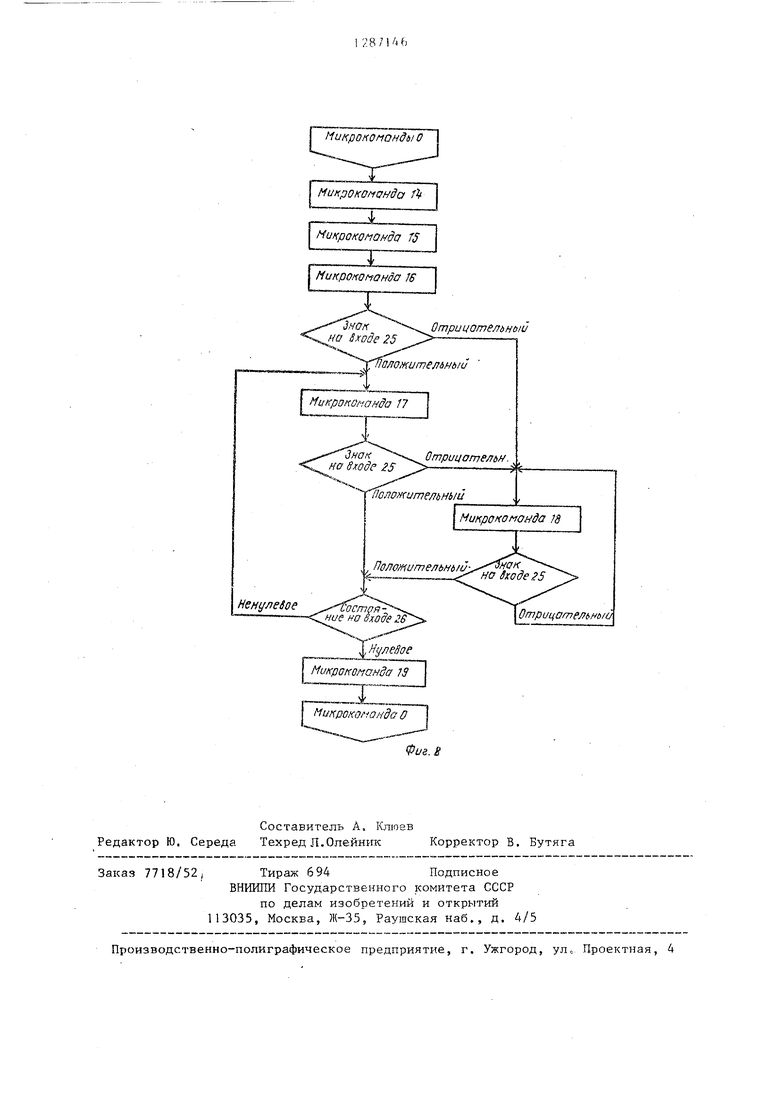

На фиг, 1 представлена схема предлагаемого устройства для обработки данных; на фиг. 2 - схема блока выбора частного; на фиг, 3 - то же, блока ускоренного умножения; на фиг, 3 - то же, блока формирования знака; на фиг. 5 - диаграмма алгоритма загрузки; на фиг. 6 - то же, алгоритма сложения; на фиг. 7 - то же, алгоритма умножения; на фиг, 8 - то же, алгоритма деления,

Устройство для обработки данных (фиг, 1) содержит регистр 1 операнда, основной коммутатор 2, байтовый коммутатор 3, основной арифметико- логический блок 4, байтовый арифметико-логический блок 5, основной ре- гистр 6, байтовый регистр 7, основной коммутатор 8, сдвигатели 9 и 10, регистр 11 сдвига, коммутатор 12 множителя, блок 13 выбора частного, бло

14 ускоренного умножения, блок 15 формирования знака, счетчик 16 тактов, информационней вход 17 устройства, выход,18 устройства, блок 19 микропрограммного управления, вход 20 вида операции устройства, установочный вход 21 устройства, вход 22 начала работы устройства, тактовый выход 23 блока 19 микропрограммного з правления, входы 24-27 условий блока 19 микропрограммного управления, управляюидае выходы 28-43.

Блок 13 выбора частного (фиг. 2) содержит регистр 44 делимого, табличный преобразователь 45 делителя, сдви- сдвигатели 46 и 47 делимого и делителя, элемент 48 памяти частного, счетчик 49 частного и регистр 50 частного.

Блок 14 ускоренного умножения (фиг. З) содержит табличный преобразователь 51 мнржителя, сдвигатели 52-54, коммутатор 55, арифметико-ло- гические элементы 56 и .57,

35

45

50

Блок 15 формирования знака фиг. 4 содержит коммутатор 58, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 59, регистр 60 знака, арифметико-логический элемент 61.

Блок 19 микропрограммного управления может быть реализован .аналогично

5

0

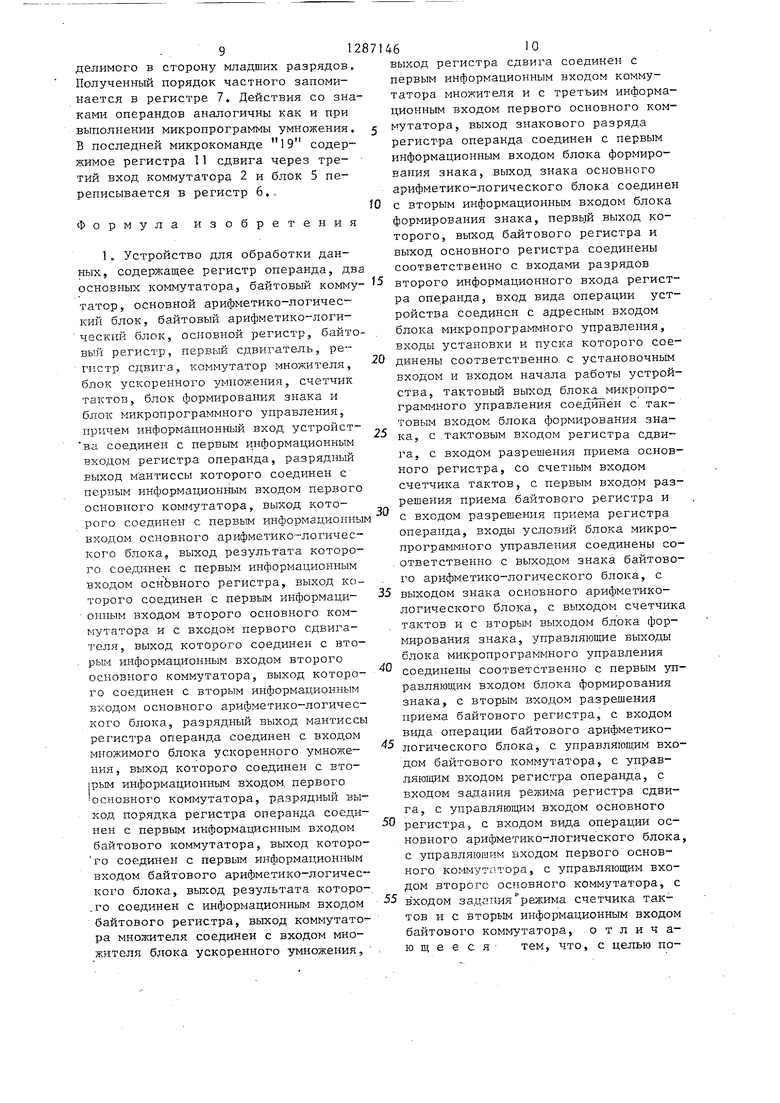

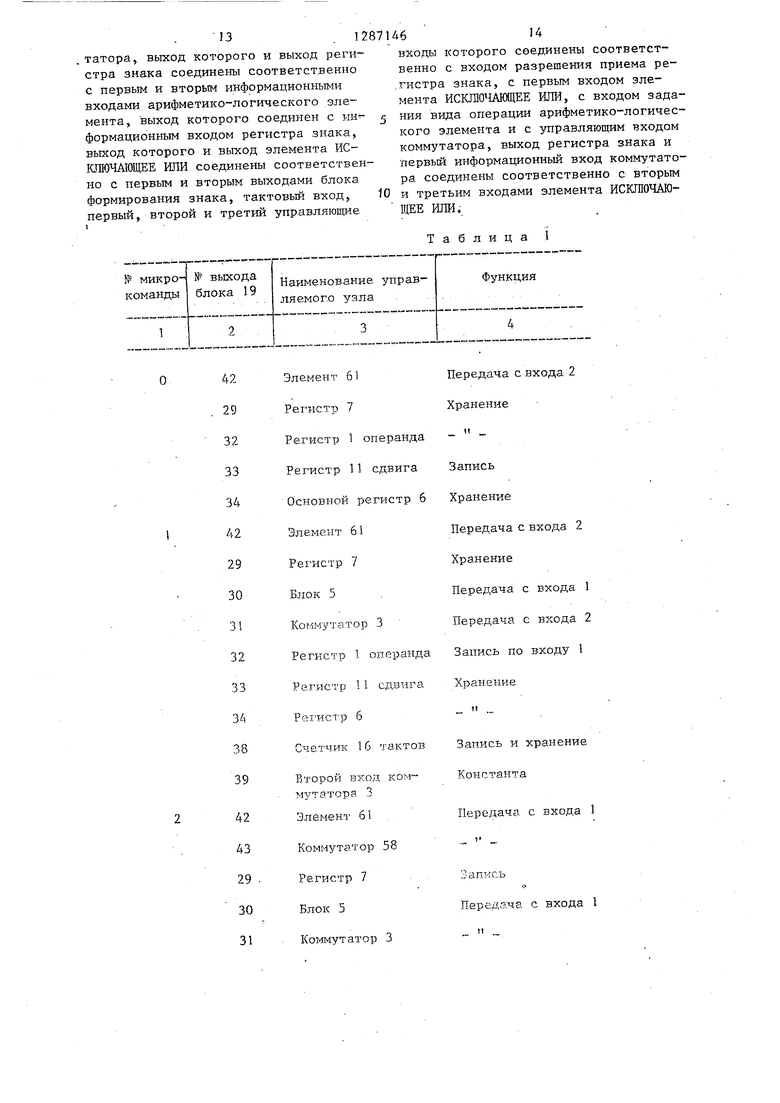

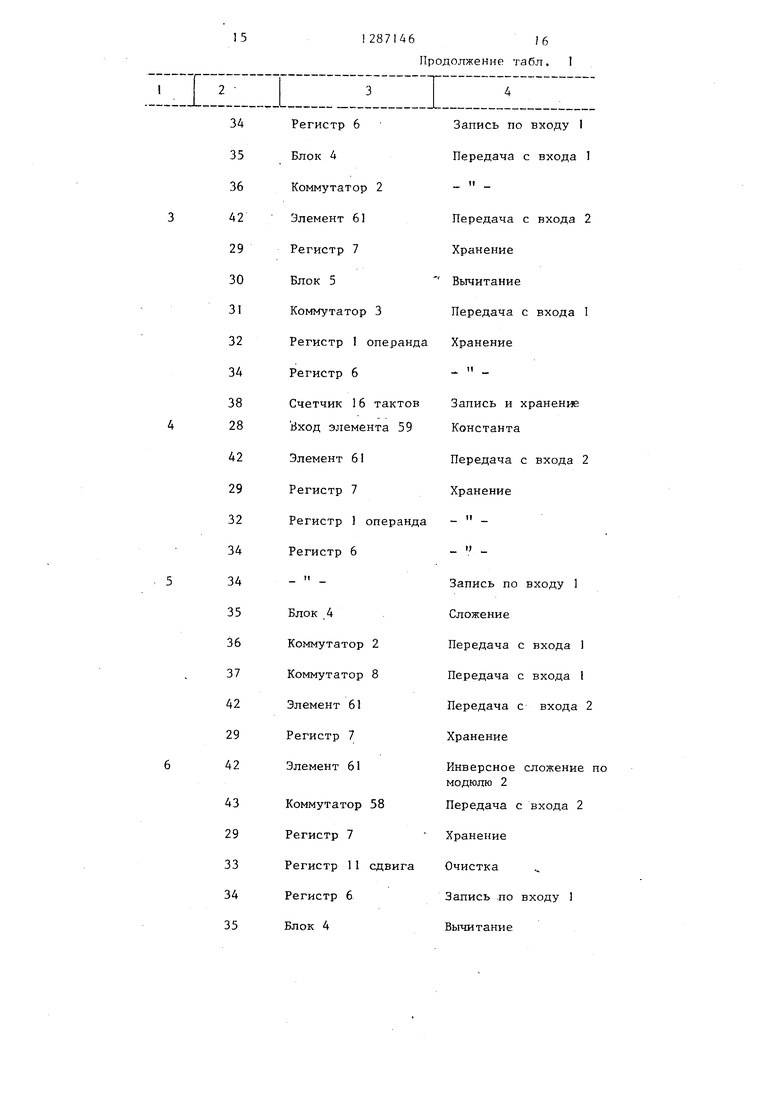

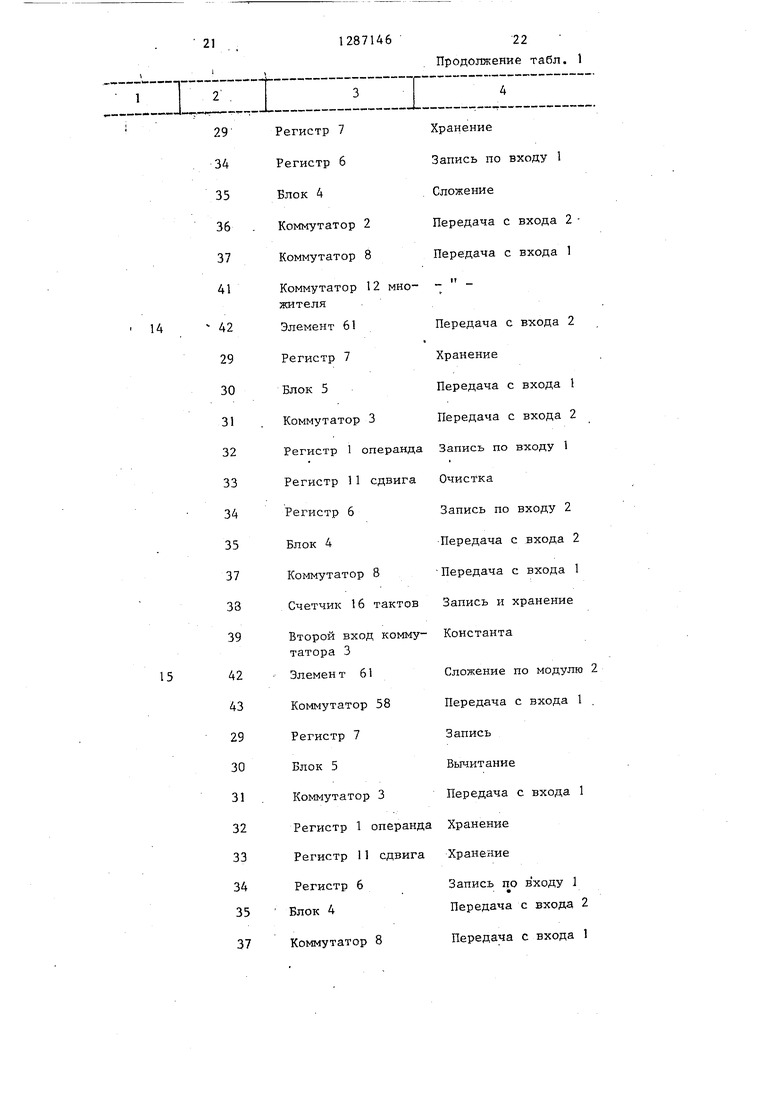

известному. В блоке 19 микрогфограм- много управления кодируются микропрограммы согласно фиг. 5-8. Используемые микрокоманды приведены в табл. 1.

Блок 13 выбора частного предназначен для выбора по пяти старшим разрядам делимого (остатка) н делителя шестнадцатеричной цифры частного из элемента памяти частного, которая равна или больше, но не более, чем на две единицы истинной цифры частного , а также для изменения при необходимости выбранной цифры частного на единицу на счетчике.

Блок 14 ускоренного умножения . предназначен для умножения мантиссы множимого на четыре разряда множителя, а также для умножения мантиссы

четырехразрядную

5

делителя на опытную цифру частного.

Сдвигатели 9 и 10 выполняют соответственно сдвиг на четыре разряда в сторону старших и младших разрядов.

Регистр 11 сдвига предназначен для хранения и сдвига частного и множителя на четыре разряда соответственно в сторону старших и младших разрядов при записи истинной четырехразрядной цифры частного и частичного произведения.

Блок 15 формирования знака выполня- .ет анализ знаков исходньк операндов, участвуюш;их в операциях, установле- 5 ние знака результата.

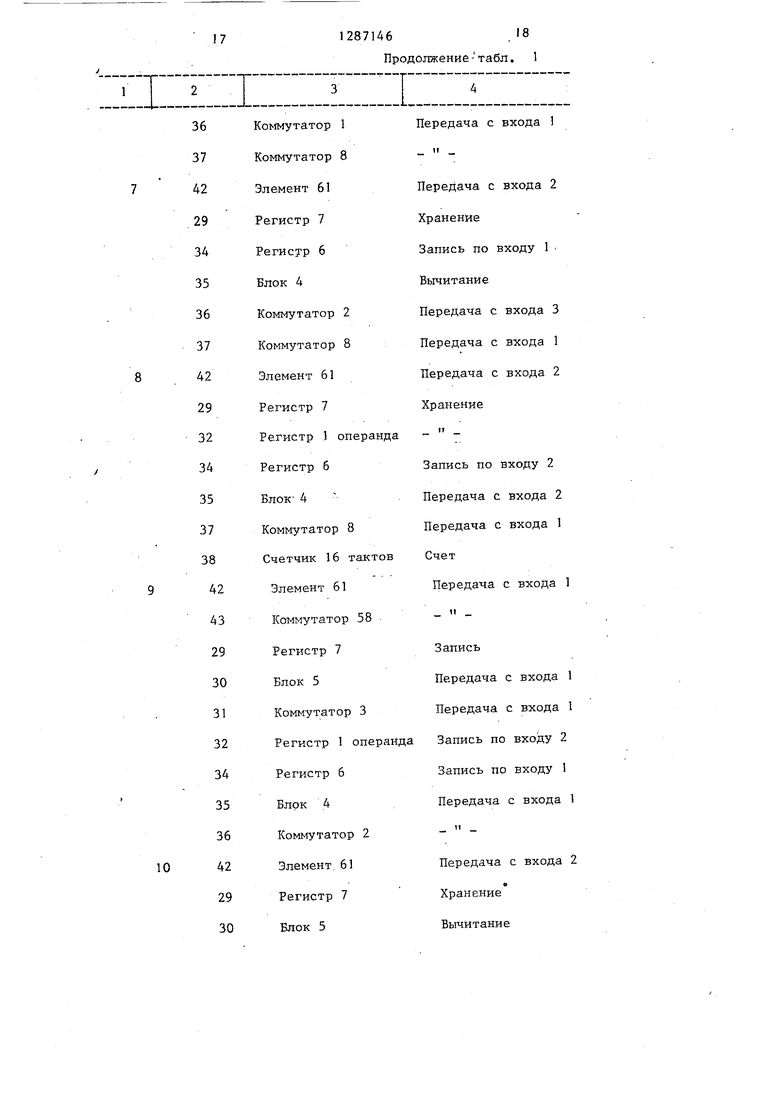

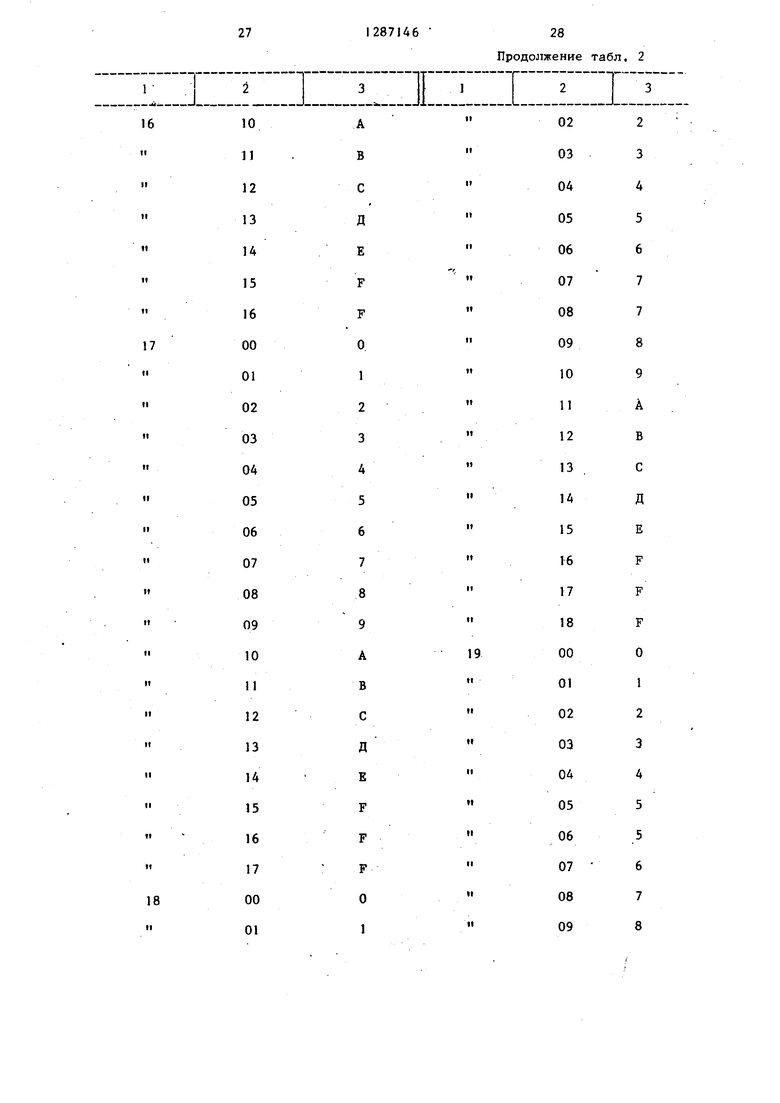

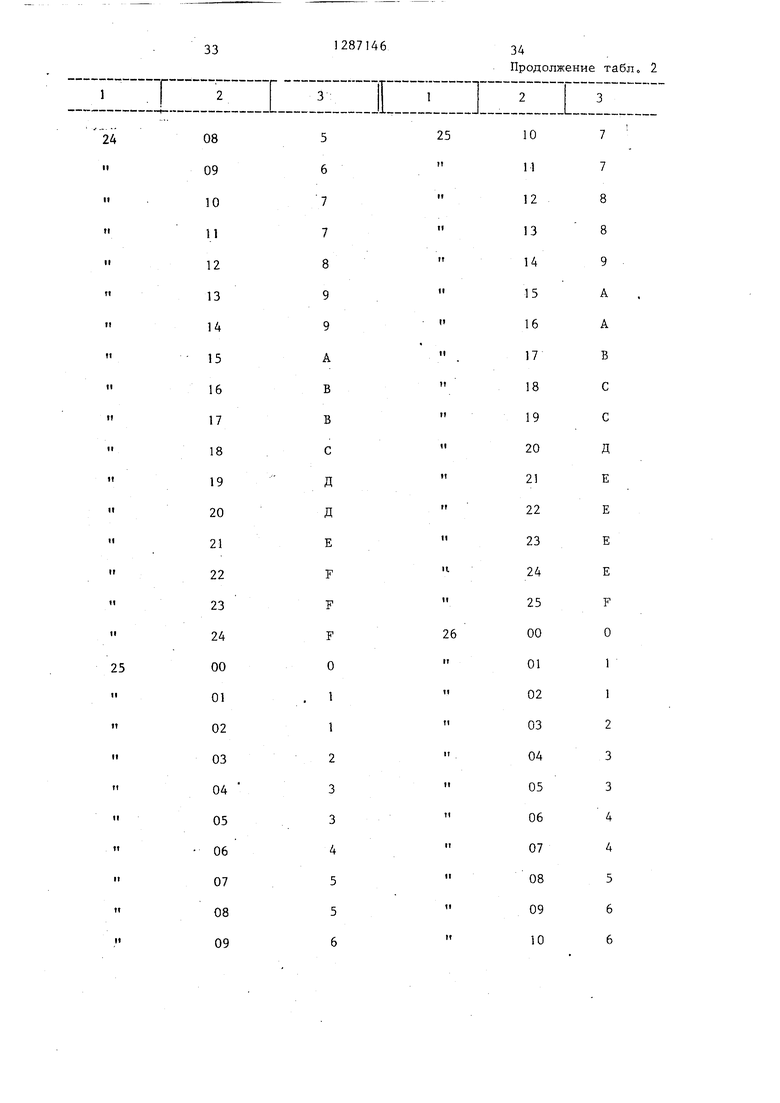

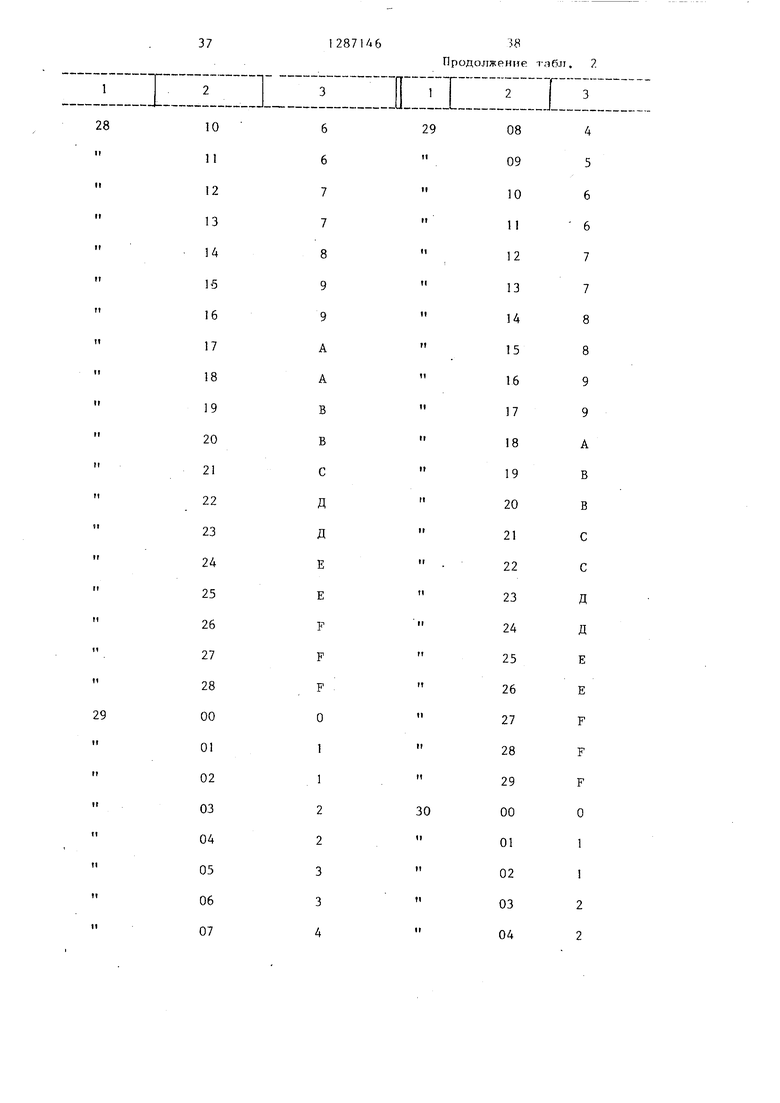

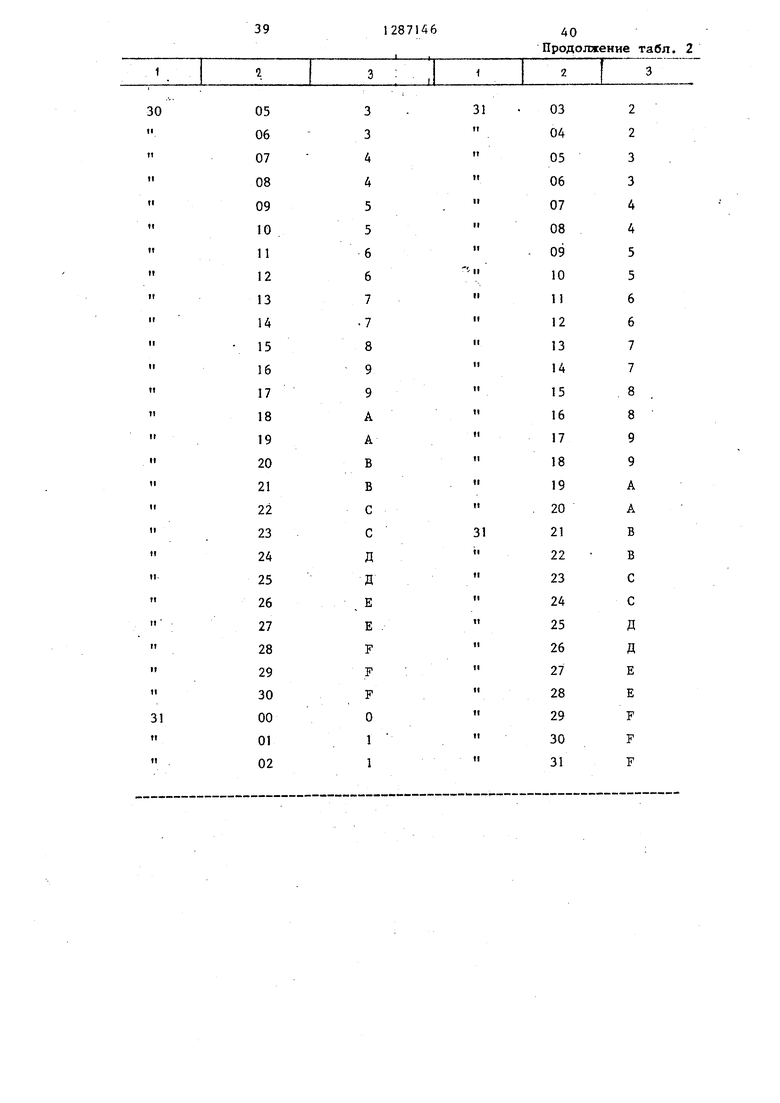

Код,ировка элемента 48 памяти частого представлена в табл. 2.

Сдвигатели 52-54 выполняют соответственно сдвиг на один, два и три разряда в сторону старших разрядов.

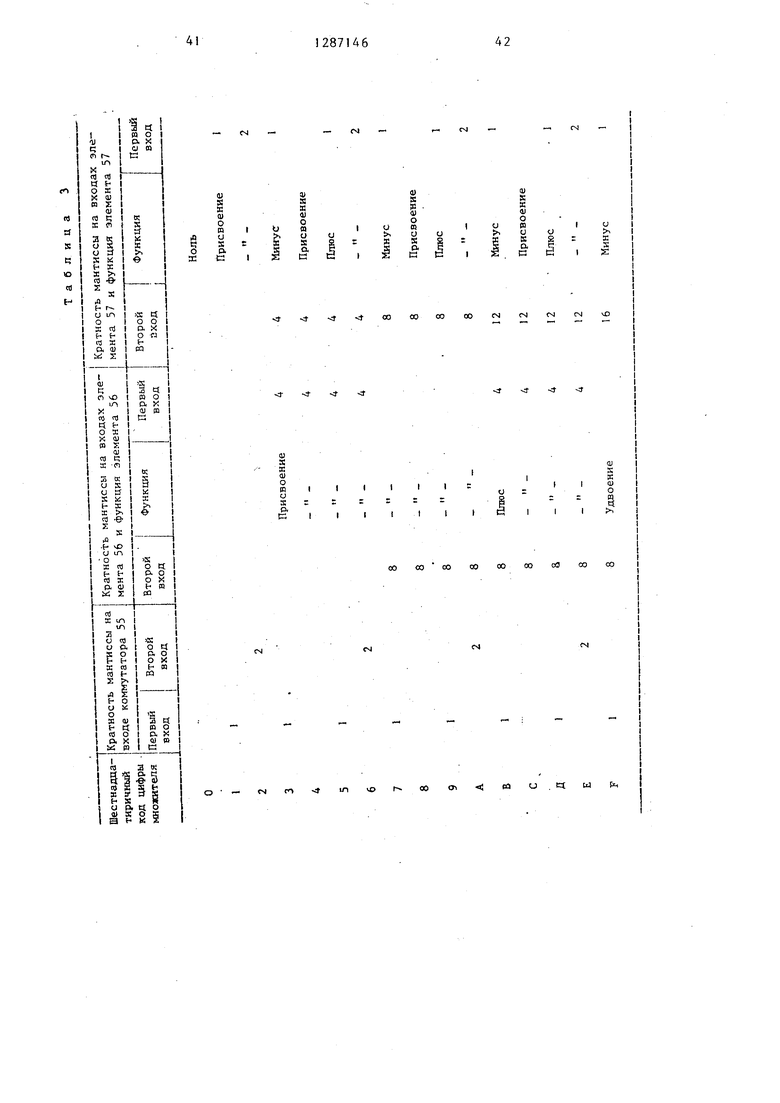

Кодировка табличного преобразователя 51 множителя представлена в табл. 3, где указана кратность множимого на входах коммутатора 55, эле- элементов 56 и 57 и выполняемая ими функция.

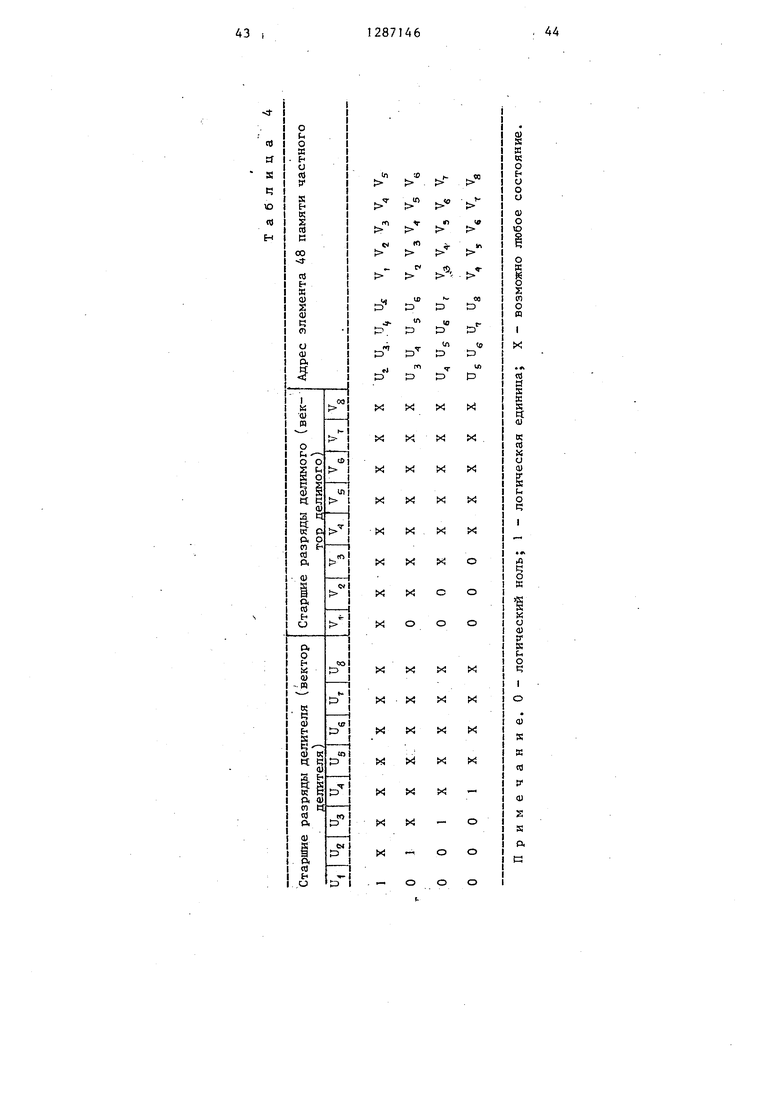

Кодировка табличного преобразователя 45 делителя представлена в табл. 4, в которой отображен алгоритм преобразования разрядов делимого и делителя в разряды адреса элемента 48 памяти частного,

Арифме гмко-яогические блоки 4 и 5 и арифметико-логические элементы 56, 57 и-61 реализуются на универсальных арифметико-логических элементах серии 155.

Устройство для обработки данных работает следующим образом.

Работа устройства начинается с запуска блока i 9 микропрограммного управления. По сигналу сброса на входе 21 блок 19 устанавливается в исходное состояние и формирует на всех своих выходах коды,-соответствующие исходной микрокоманде О. После этого на вход 20 подается код команды, подлежащей выполнению. При поступлении сигнала на вход 22 начинается формирование в блоке 19 микрокоманд и выдача на входы 28-43 необходимых микроприказов с учетом условий, поступающих на входы 24-27 На выходе 23 формируются соответствующие тактовые сигналы, что обеспечивает функциониро 5ание устройства по однотактному принципу.

По окончании выполнения микропрограммы, соответствующей заданному ко коду команды, последняя микрокоманда задает безусловный переход на микрокоманду о и тем самым переводит устройство в исходное состояние, при котором блокируется прохождение тактовых сигналов, блок 19 переключается на прием кода следующей команды .

На фиг. 5 показан алгоритм микропрограммы загрузки. Выполнение команды загрузки осуществляется на два такта.

В первом такте (микрокоманда 1) загружаемый операнд записывается по первому входу в регистр 1 операнда. Во втором такте (микрокоманда 2), порядок, мантисса и знак операнда соответственно с выходов регистра 1 операнда поступают на первый вход коммутатора 3, первый вход коммута- тора 2 и первый вход коммутатора 3, первый вход коммутатора 2 и первый вход блока 15 формирования знака. .

Коммутаторы 2 и 3 переключаются на передачу с первых входов. Мантисса и порядок поступают на первые входы блока 4 и 5, которые в данной микрокоманде выполняют функции пере- дачи с первых входов. С их выходов мантисса и порядок записываются с первых входов в регистры 6 и 7.

Знак операнда с первого входа ком мутатора 58 передается на первый вход элемента 61 и далее на вход, регистра 60. Запись в регистры 6, 7 и 60 производится по поступлении так64

тового сигнала на тактовые входы регистров .

На фиг. 6 показан алгоритм микропрограммы сложения. Команда сложения выполняется после выполнения команды загрузки первого операнда. В микрокоманде 1 второй операнд записывается по первому входу в регистр 1 операнда. В следующем такте (микрокоманда З) порядок второго операнда через коммутатор 3 поступает на пер- вход блока 5, а на второй его вход из регистра 7 поступает порядок первого операнда. Порядки вычитаются и разность порядков с выхода блока 5 записывается в счетчик 16 тактов. В качестве условий перехода в данной

микрокоманде используются знак на входе 24 и входе 26 нулевого состояния счетчика 16 тактов. Если разность порядков положительна и не равна нулю следует переход на микрокоманду 8, в которой производится сдвиг мантиссы меньшего числа в сторону младших разрядов и уменьщение содержимого счетчика 16 тактов на единицу. Повторение микрокоманды 8 производится до обнуления счетчика 16 тактов. Если разность порядков, полученная в микрокоманде 3 отрицательна, то следует микрокоманда 9, в которой первый и второй операнды меняются местами. Первый операнд с выхода регистра 6 и 7 и регистра 60 блока

15записывается в регистр 1 операнда с второго входа, а содержимое регистра 1 операнда записывается в регистры 7, 6 и 60 аналогично микрокоманде 2. В микрокоманде 10 порядки операндов вычитаются, а положительная разность записывается в счетчик

16тактов и далее следует переход на микрокоманду 8 для сдвига мантиссы меньшего операнда. При нулевом состоянии счетчика 16 тактов, полученного в микрокомандах 3 или 8 выполняется микрокомандаV4, в которой анализируются знаки операндов, постуающие на второй и третий входы элемента 59, и признак операции сложения (0), поступающий на первый вход, эти три сигнала складываются по модулю два и в зависимости от бита получаемой суммы сяедует переход на микрокоманду 5, в которой мантиссы операндов складываются, либо на микрокоманду 6, в которой мантиссы вычитаются. Сложение и вычитание мантисс производится в блоке 4. Одна из

512

мантисс поступает на первый вход блока 4 с первого входа коммутатора 2, другая мантисса поступает на второй вход блока 4 с первого входа коммутатора 8. В зависимости от зна- ка разности мантисс определяется зна результирующего операнда. Это действие выполняется на элементе 61 блока 15 (фиг. 4), на первый вход которого через второй вход коммутатора 58 по- ступает знак с выхода блока 4 и знак содержащийся в регистре знака Элемент 61 выполняет функцию инверсного сложения по модулю два, результат которой является знаком суммы операн дов, записывается в регистр знаков 60. Отрицательный знак разности мантисс определяет необходимость перехода к микрокоманде 7, в которой полученная разность с выхода регист- ра 6 через первый вход коммутатора 8 поступает на второй вход блока 4, а на его первый вход через третий вход коммутатора 2 подается нулевая ман- тисса, предварительно полученная очисткой регистра 11 сдвига. Выполняется функция вычитания и таким образом мантисса результата из дополнительного кода преобразуется в прямой код и записывается в регистр 6.

Порядок операнда, содержащийся в регистре 7., является порядком результата,

Микропрограмма команды вычитания

выполняется аналогично, с той лишь разницей, что при определении знака на выходе элемента 59 на первый его вход подается инверсньш сложению признак вычитания.

На фиг. 7 показан .алгоритм выполнения микропрограммы умножения. Команде умножения предшествует команда загрузки первого операнда (множителя). Б микрокоманде О содержимое 6 основного регистра переписывается в регистр 11 сдвига, В микрокоманде 1 выполняется запись второго операнда (множимого) в регистр 1 операнда и константы в счетчик 16 тактов. В следующей микрокоманде 11 с вы- хода регистра 11 сдвига младшая тетрада множителя поступает на первый вход коммутатора I2 множителя, с выхода которого тетрада множителя по- ступает на вход блока 14 ускоренного умножения и на вход преобразователя 51 множителя. В зависимости от поступившего кода на первом, втором и тре

5 0 5 0

5 0 5

5

0

466

тьем выходах преобразователя 51 множителя вырабатываются сигналы в виде кодов управления функциями в соответствии с табл. 3. На первый и второй входы коммутатора 55 соответственно поступают однократная и двухкратная мантисса множимого. На первый и второй входы элемента 56 поступает соответственно четырехкратная и восьмикратная мантисса множимого.

Произведение множи1 {ого на тетраду множителя формируется на выходе элемента 57 и через второй вход коммутатора 2, второй вход блока 4, сдвига- тель 10 записывается в регистр 6.

В этом же такте производится сдвиг на тетраду в сторону младших разрядов мантиссы мнозштеля, содержащийся в рег истре 11 сдвига, таким образом на выходе младших разрядов регистра 11 сдвига подготавливается следующая тетрада множителя.

Константа, занесенная в счетчик 16 тактов, в микрокомандах 11 и 12 уменьшается на единицу. В микрокомандах 12 формирующиеся произведения множимого на очередную шестнадцатиричную цифру множителя складывается с частичной суммой произведений, сдвинутой на тетраду в сторону младших разрядов. Частичная сумма произведений накапливается в регистре 6 и поступает на подсуммирование на второй, вход блока 4 через коммутатор 8. Сдвиг частичной суммы производится сдвигателем 10 при записи в регистр 6.

Сложение порядков производится в блоке 5, Порядок результата записывается в регистре 7.

Формирование знака производится в блоке 15 на элементе 61, который .выполняет функцрю сложения по модулю два Результат сложения представляет знак произведения и записывается в регистр 60.

В микрокоманде 13 выполняется подсуммирование последнего частичного произведения и запись суммы частичных произведений в регистр 6 без сдвига с первого входа.

На фиг. 8 показана микропрограмма деления. Команде деления предшествует команда, загрузки первого операнда (делимого). В микрокоманде 14 в регистр 1 операнда записывается второй операнд (делитель), а в счетчик 16 - тактов - константа, определяющая требуемое количество тетрад частного.

712

Мантисса делимого сдвигается на тетраду в сторону младших разрядов путе передачи мантиссы через коммутатор 8, блок 4 и сдвигатель 10 на запись с второго входа регистра 6. В следу- ющей микрокоманде старшие восемь разрядов содержимого регистра 6, пройдя повторно через коммутатор 8, блок 4 записываются в регистр 44 делимого Записанные разряды представляют со- бой начальный вектор делимого, С выхода регистра 1 операнда старшие восемь разрядов, представляющих вектор делителя, поступают на вход преобразователя 45 делителя и вход сдвига- тедя 47 делителя (фиг. 2), В преобразователе 45 делителя определяется количество нулей от запятой, условно фиксируемой перед старшим разрядом

ДО первой единицы, и вьщается управ- ление на входы сдвигателей 46 и 47 делимого и делителя для выполнения сдвига Ка соответствующее количество разрядов в сторону запятой, С выходов сдвигателей делимого и делителя пять разрядов делимого и разряды с второго по пятый делителя поступают соответственно на первый и второй входы элемента 48 памяти частного.

Заполнение элемента 48 памяти частного показано в табл, 2, По соответствующему адресу формируется опытное значение четырехразрядного частного, которое не превосходит истинной шестнадцатиричной цифры частного

С выхода тетрада частного записывается в счетчик 49 частного и -поступает на первьй выход блока 13 выбора частного и далее через вход коммутатора 12 множителя на вход блока 14 ускоренного умножения, на другой вход выхода регистра 1 операнда поступает мантисса делителя, В блоке 14 ускоренного умножения формируется произведение делителя на тет- раду выбранной цифры частного,

Для проверки цифры частного, полученное произведение через второй вход коммутатора 2, подается в качестве вычитаемого на первый вход блока 4, на второй вход которого подается делимое из регистра 6, сдвинутое сдвйгателем 9 в сторону старших разрядов, Блок 4 выполняет функцию вычитания., I

Если резз льтат вычитания положителен, то выбранная цифра частного является истинной,- Следует переход

5

71

.5 О

П

35

0

468

к микрокоманде. 17, а содержимое счетчика 16 тактов уменьшается на единицу.

В микрокоманде 17 содержимое счетчика 49 частного, переписанное в регистр 50 частного с выхода последнего, записывается в младшую тетраду регистра 11 сдвига, который выполняет ФУНКЦИЮ сдвига на тетраду в сторону старших разрядов, В регистр 44 делимого записываются старшие восемь разрядов полученного остатка,

В-микрокоманде 17 работа устройства протекает аналогично описанному.

Вектор делителя является величиной постоянной в течение всего процесса деления пары чисел, так как определяется только старшими разрядами делителя.

Описанный процесс повторяется.

При получении отрицательного результата вычитания в блоке 4, следует переход к микрокоманде 18, В этой микрокоманде выполняется новая проверка, заключающаяся в том, что к остатку, записанному в регистре 6 прибавляется мантисса делителя, которая поступает с первого входа коммутатора 2, Основное АЛУ выполняет .функцию сложения.

Если результат второй прочерки по- .ложительньй, то содержимое регистра 50 частного, представляющее уменьшенную на единицу выбранное значение цифры частного, записывается в регистр 11 сдвига, путем сдвига в сторону старших разрядов, В последующих тактах работа протекает аналогично описанному по алгоритму Последняя цифра частного записывается в регистр 11 сдвига. Так как при каждой записи в регистре 11 сдвига выполняется . сдвиг информации на тетраду в сторону старших разрядов, то после последнего сдвига в регистре 11 сдвига будет сформирована мантисса частного. Выход из цикла осуществляется по признаку обнуления счетчика 16 тактов,

В блоке 5 в течение операции деления выполнялось два действия: вычитание разности порядков делимого и делителя и прибавление к разности порядков единицы, которая компенсирует начальный сдвиг на тетраду мантиссы

91

делимого в сторону младших разрядов. Полученный порядок частного запоминается в регистре 7. Действия со знаками операндов аналогичны как и при выполнении микропрограммы умножения, В последней микрокоманде 19 содержимое регистра 11 сдвига через тре- тий вход коммутатора 2 и блок 5 переписывается в регистр 6.,

Формула изобретения

1„ Устройство для обработки данных, содержащее регистр операнда, два

выход регистра сдвига соединен с первым информационным входом коммутатора множитепя и с третьим информационным входом первого основного коммутатора, выход знакового разряда регистра операнда соединен с первым информационным входом блока формирования знака, :Выход знака основного арифметико-логического блока соединен с вторым информационным входом блока формирования знака, первый выход которого, выход байтового регистра и выход основного регистра соединены соответственно с входами разрядов

основных ком1 татора, байтовый комму- второго информационного входа регисттатор, основной арифметико-логический блок, байтовый арифметико-логический блок, основной регистр, байтовый регистр, первый сдвигатель, регистр сдвига, коммутатор множителя, блок усрчОренного умножения, счетчик тактов, блок формирования знака и блок микропрограммного управления, причем информационный вход устройст- ва соединен с первым информационным входом регистра операнда, разрядный выход мантиссы которого соединен с первым информационным входом первого основного коммутатора, выход которого соединен с первым информационны входом основного арифметико-логического блока, выход результата которого соединен с первым информационным входом оснЬвного регистра, выход которого соединен с первым информационным входом второго основного коммутатора и с входом первого сдвига- теля, выход которого соединен с вторым информационным входом второго основного коммутатора, выход которого соединен с вторым информационным входом основного арифметико-логического блока, разрядный выход мантиссы регистра операнда соединен с входом множимого блока ускоренного умножения, выход которого соединен с вторым информационным входом, первого основного коммутатора, разрядный выход порядка регистра операнда соединен с первым информационным входом байтового коммутатора, выход которо- го соединен с первым информационным входом байтового арифметико-логического блока, вьщод результата которо.го соединен с информационным входом байтового регистра, выход коммутатора множителя соединен с входом множителя блока ускоренного умножения,

10

выход регистра сдвига соединен с первым информационным входом коммутатора множитепя и с третьим информационным входом первого основного коммутатора, выход знакового разряда регистра операнда соединен с первым информационным входом блока формирования знака, :Выход знака основного арифметико-логического блока соединен с вторым информационным входом блока формирования знака, первый выход которого, выход байтового регистра и выход основного регистра соединены соответственно с входами разрядов

ра операнда, вход вида операции устройства соединен с адресным входом блока микропрограммного управления, входы установки и пуска которого соединены соответственно с установочным входом и входом начала работы.устройства, тактовый выход блока микропрограммного управления соединен с тактовым входом блока формирования знака, с тактовым входом регистра сдвига, с входом разрешения приема основного регистра, со счетным входом счетчика тактов, с первым входом разрешения приема байтового регистра и с входом разрешения приема регистра операнда, входы условий блока микропрограммного управления соединены соответственно с выходом знака байтово- I o арифметико-логического блока, с выходом знака основного арифметико- логического блока, с выходом счетчика тактов и с вторым выходом блока формирования знака, управляюш;ие выходы блока микропрограммного управления соединены соответственно с первым управляющим входом блока формирования знака, с вторым входом разрешения приема байтового регистра, с входом вида операции байтового арифметикологического блока, с управля1ош,им входом байтового коммутатора, с управляющим входом регистра операнда, с вхо.дом задания режима регистра сдвига, с управляюнщм входом основного

регистра, с входом вида операции основного арифметико-логического блока, с управляющим входом первого основного коммутатора, с управляющим входом второго основного коммутатора, с

входом задапня режима счетчика тактов и с вторым информационным входом байтового коммутатора, отличающееся- тем, что, с целью по

вьаиеиия бьютродействия при выполнении операции деления, оно содержит второй.сдвигатель и блок выбора частного, причем второй информационный вход регистра операнда соединен с выходом устройства, выход результата байтового арифметико-логического блока соединен с информационным входом счетчика тактов, выход результата

основного арифметико-логического бло- О счетным входом счетчика частного, с

ка С9единен с входом второго сдвигателя, выход которого соединен с вторым информационным входом основного регистра, выход которого соединен с

входом разрешения приема регистра делимого и с тактовым входом блока выбора частного, управляющий вход и первый, второй и третий выходы кото первым информационным входом регистра 5 рого„соединены соответственно с вхо- jсдвига, выход байтового регистра со- ДОм задания режима счетчика частного, единен с вторым информационным входом байтового арифметико-логического бло- ка, выход результата основного ариф20

метико-логического блока и разрядный выход мантиссы регистра операнда со- I единены соотйетственно с входами делимого и делителя блока выбора частного, тактовый вход и управляющий вход которого соединены соответственно с тактовым выходом и с тринадцатым управляющим выходом блока микропрограммного управления, четырнадцатый, пятнадцатый и щестнадцатый управляющие выходы которого соединены соответственно с управляющим входом коммутатора множителя, с вторым и третьим управляющими входами блока формирования знака; первый, второй

25

30

с выходом элемента памяти частного, с выходом счетчика частного и с выходом регистра частного.

3. Устройство по п. 1, отличающееся тем, что блок ускоренного умножения содержит табличный преобразователь множр;теля, три сдвигателя, коммутатор и два арифметико- логических элемента, причем вход множимого блока ускоренного умножения соединен с первым информационным входом коммутатора и с входами первого, второго и третьего сдвигателей, выход первого сдвигателя соединен с вторым информационным входом коммутатора, выходы второго и третьего сдвигателей соединены соответственно с первым и вторым информационнь1ми входами первои третий выходы блока выбора частно- 35 го арифметико-логического элемента,

выходы коммутатора и первого арифметико-логического элемента соединены соответственно с первым и вторым информационными входами второго ариф- 40 метико-логического элемента, выход которого является выходом блока ускоренного умножения, вход множителя которого соединен с входом табличного преобразователя множителя, выходы

го соединены соответственно с вторым и третьим информационными входами коммутатора множителя, с вторым ин- . формационным входом регистра сдвига.

2. Устройство по п. 1, .отличающееся тем, что блок выбора частного содержит регистр делимого, табличный преобразователь делителя, сдвигатели делимого и делителя, 45 которого соединены соответственно с элемент памяти частного, счетчик частного и регистр частного, причем вход делимого блока выбора частного соединен с информационным входом регистра делимого, выход которого соединен с информационным входом сдвигателя делимого, выход которого соединен с первым адресным входом элемента памяти частного, второй адресный вход которого соединен с выходом сдвигателя делителя, вход величины сдвига которого соединен с входом величины сдвига сдвигателя делимого и с выходом табличного преобразователя

входами задания вида операции первого и второго арифметико-логических элементов и с управляющим входом ком мутатора.

50

4. Устройство по п. 1, о т л и чающееся тем, что блок формирования знака содержит коммутатор элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр зна ка и арифметико-логический элемент, причем первый и второй информационные входы блока формирования знака соединены соответственно с первым и вторым информационными входами комму

делителя, вход которого соединен с информационным входом сдвигателя делителя и с входом делителя блока выбора частного, выход элемента памяти частного соединен с информационным входом счетчика частного, выход которого соединен с информационным входом регистра частного, вход разрешения приема которого соединен со

5 рого„соединены соответственно с вхо- ДОм задания режима счетчика частного,

20

25

30

с выходом элемента памяти частного, с выходом счетчика частного и с выходом регистра частного.

3. Устройство по п. 1, отличающееся тем, что блок ускоренного умножения содержит табличный преобразователь множр;теля, три сдвигателя, коммутатор и два арифметико- логических элемента, причем вход множимого блока ускоренного умножения соединен с первым информационным входом коммутатора и с входами первого, второго и третьего сдвигателей, выход первого сдвигателя соединен с вторым информационным входом коммутатора, выходы второго и третьего сдвигателей соединены соответственно с первым и вторым информационнь1ми входами перво45 которого соединены соответственно с

входами задания вида операции первого и второго арифметико-логических элементов и с управляющим входом коммутатора.

50

4. Устройство по п. 1, о т л и

чающееся тем, что блок формирования знака содержит коммутатор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр зна ка и арифметико-логический элемент, причем первый и второй информационные входы блока формирования знака соединены соответственно с первым и вторым информационными входами комму1312871

татора, выход которого и выход регистра знака соединены соответственно с первым и вторым информационными входами арифметико-логического элемента, выход которого соединен с ин- формационным входом регистра знака, выход которого и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым выходами блока формирования знака, тактовый вход, 10 первый, второй и третий управляющие

Элемент 61

Регистр 7

Регистр 1 операнда

Регистр 11 сдвига

Основной регистр 6 Элемент 61

Регистр 7

Блок 5

Коммутатор 3

Регистр 1 операнда

Регистр 11 сдвига Pei HCTp 6

Счетчик 16 тактов

Второй вкод коммутатора 3

Элемент 61

Коммутатор 58

Регистр 7

Блок 5

Коммутатор 3

U614

входы которого соединены соответственно с входом разрешения приема ре.гистра знака, с первым входом элемента ИСКЛ10ЧАЩЕЕ ИЛИ, с входом задания вида операции арифметико-логического элемента и с управляющим входом коммутатора, выход регистра знака и первый информациоиньй вход коммутатора соединены соответственно с вторым и третьим входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Таблица

Передача с входа 2

Хранение и

Запись

Хранение

Передача с входа 2

Хранение

Передача с входа 1

Передача с входа 2

Запись по входу 1

Хранение - .„

Запись и хранение Константа

Передача с входа 1 .„. .

Запись

о

Передача с входа 1 и

17

lill

2

36

37

42

29

34

35

36

37

42

29

32

34

35

37

38 42 43 29 30 31 32 34 35 36 42 29 30

10

Коммутатор 1 Коммутатор 8 Элемент 61 Регистр 7 Регистр 6 Блок 4 Коммутатор 2 Коммутатор 8 Элемент 61 Регистр 7

Регистр 1 операнда Регистр 6 Блок-4

Коммутатор 8 Счетчик 16 тактов

Элемент 61

Коммутатор 58

Регистр 7

Блок 5

Коммутатор 3

Регистр 1 операнда

Регистр 6

Блок 4

Коммутатор 2

Элемент, 61

Регистр 7

Блок 5

1287146.18

Продолжение- табл. 1

Передача с входа 1 II

Передача с входа 2

Хранение

Запись по входу 1

Вычитание

Передача с входа 3

Передача с входа 1

Передача с входа 2

Хранение 1

Запись по входу 2 Передача с входа 2 Передача с входа 1 Счет

Передача с входа 1

ч

Запись

Передача с входа 1 Передача с входа 1 Запись по входу 2 Запись по входу 1

Передача с входа 1 11

Передача с входа 2

Хранение

Вычитание

21 128714622

Продолжение табл. 1

23128714624

Продолжение табл. 1 IР

2

38 Счетчик 16 тактовХранение

1642 Элемент 61Передача с входа 2 29Регистр 7Хранение

32Регистр 1 операнда- 33Регистр 11 сдвига- 34Регистр 6Запись по входу 1

35Блок 4Вычитание

36Коммутатор 2Передача с входа 2

37Коммутатор 8 .- 40Счетчик 49 частногоЗапись и счет

41Коммутатор 12 мно-Передача с входа 2 жителя

38Счетчик 16 тактовСчет

17. 42Элемент 61 .Передача с входа 2

29Регистр 7Хранение

32Регистр 1 операнда- 33Регистр 11 сдвигаСдвиг на тетраду в

сторону старших разрядов

34Регистр 6Запись по входу 1

35Блок 4Вычитание

36Коммутатор 2Передача с входа 2

37Коммутатор 8- 4QСчетчик 49 частногоЗапись и счет

41Коммутатор 12 мно-Передача с входа 2 жителя

38Счетчик 16 тактовСчет

1.8 42Элемент 61Передача с входа 2

л.

29Регистр 7Хранение

32Регистр 1 операнда- 9

33Регистр 11 сдвига

34Регистр 6

35Блок 4

36Коммутатор 2

37Коммутатор 8

40 Счетчик 49 частного

38Счетчик 16 тактов 42 Элемент 61

29Регистр 7

30Блок 5

31Коммутатор 3

34Регистр 6

35Блок 4

36Коммутатор 2

39 Второй вход коммутатора 3

Запись по входу 1 Сложение

Передача с входа 1 Передача с входа 1

Счет

Хранение

Передача с входа 2

Запись

Сложение

Передача с входа 2

Запись по входу 1

Передача с входа 1

Передача с входа 3

Единица

Таблица 2

Продолжение табл. 2

05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 00 01 02

31

tt tt II

II II II II II

I II II tl tl II tl

31 tl

tl II

tl tl tl II tl

03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

2 2 3 3 4 4 5 5 6 6 7 7 8 8 9 9 A A В В С С

д д

Е Е

F F F

ш о

0)

и

S

с

- м -

0)

к

S

о

0)

о

S

о.

и

и

X X

11 о ш о к

ё

и

X S

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ, Целью изобретения является повышение быстродействия при выполнении операции деления. Поставленная цель достигается тем, что в устройство, содержащее регистр 1 операнда, основной коммутатор 2, байтовый коммутатор 3, основной арифметико-логический блок 4, байтовый арифметико-логический блок 5, основной регистр 6, байтовьй регистр 7, сдвигатель 9, регистр 11 сдвига, коммутатор 12 множителя, блок 14 ускоренного умножения, блок 15 формирования знака, счетчик 16 тактов, блок 19 микропрограммного управления, введены сдвигатель 10 и блок 13 выбора частного, 3 з.п, ф-лы, 8 ил., 4 табл. 1со to 00 Од

CU

и о m о я р, с

01 X

и о п

:

00

00

ОО00

ра

и

14 ы

1

фиг. г

срцг.З

Микрокоманда О

Микромманда /

Микрокоманда 2

Микрокомонда о

Фи9.5

ЛоложитемнбШ

Мцкрокомонда О

MUHpOHOfiCfHdO 1

Микрокоманда / /

Минро«онанда / z

остоя -. ние на Входе26

Мцкроконандо 1 3

Нулевое

MuKpOf ofia fda О

Фиг. 7

uxpoKOfiOHda Г5 j ---T-Составитель A. Клюев Редактор Ю. Середа Техред Л.Опейнгас Корректор В. Бутяга

7718/52,

Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, уло Проектная, 4

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| М | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-17—Подача