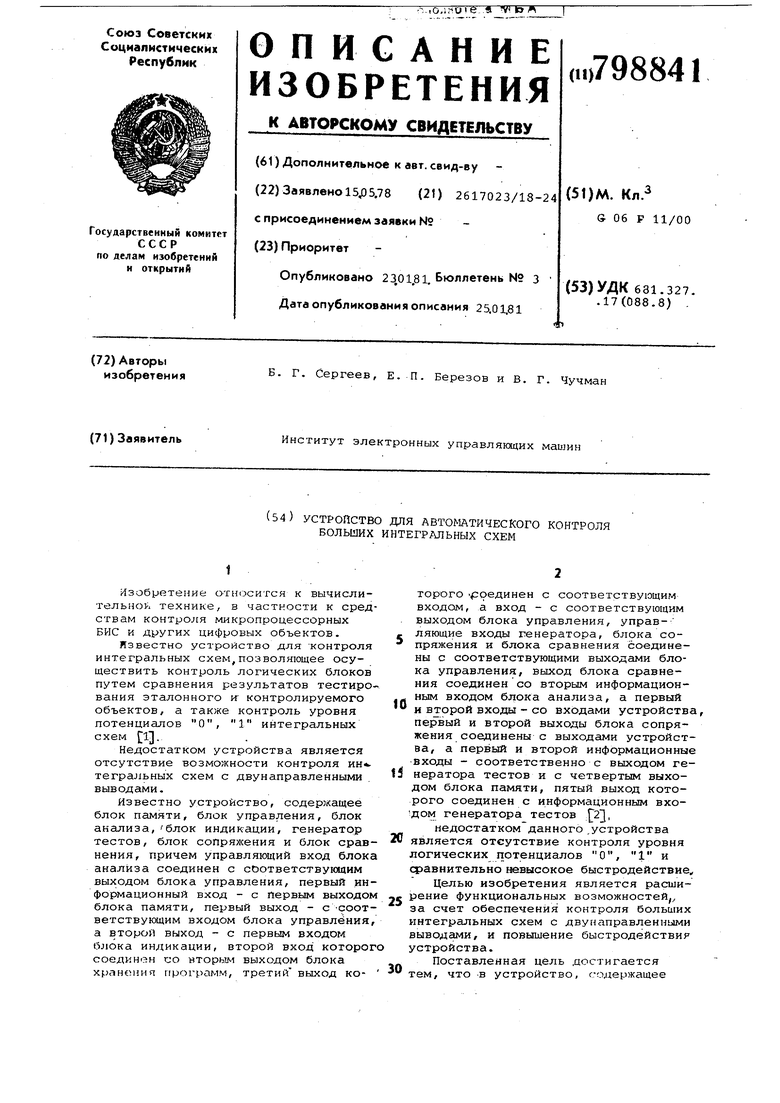

reriepkxop тестов, блок формирования входных сигналов, контролируемый блок, эталонный блок,; блок сравнен я, блок управления,блок памяти и блок индикации,I причем информа11ИОЙЙЫЙ вход блока памяти соединен с JBXOAOM ввода данных устройства, упfiliBJimwiiHtt вход - с выходом paapeimeнйя блока управления, командный,пер вый и второй информационные и тестов выходы блока памяти соединены с пер вым входом блока управления, информационныьШ: входами блоков индикации и формирования входных сигналов и информационным входом генератора те тов .соответственно управляющий вход генератора тестов соединен с запускающим выходом блока управления, а выход - со вторым информационным вх дом блока фо,Е 4ирования входных сигналов, диагностический и эталонный выходы KOTOjporo соединены с входами конт4к)лируемого и эталонного блоков coOTJieTCTBeHHO, выход блока сравнения соединен со вторым входом блока управления, первый блокируюгций выхо которого соединен с соответствующим входом блока сравнения, а сигнальный выход .- с управляющим входо блока индикации. В устройство введены первый и второй блоки перекодировки данных в двуразрядный двоичный код, селектор ёщресов и дешифратор состояния выходов эталонного блока, выход котор го соединен с третьим входом блока управления, а вход.-с выходами эталонного блока и информационным входом селектора адресов, управляющий вход которого соединен с задающим выходом блока управления, а выход с .адресным входом блока памяти, вто рой бJЗЮкиpyклaий выход блока управле ния соединен с соответствующим входом блока формирования входных-сигналов, входы первого и второго блоков перекодировки данных в двураэря ный двоичный код соединены с выход«1МИ контролируемого и эталонного блоков, соОтветствено, а выходы соответственно, с первьасм и вторым ин формацирннш4и входами блока «:равнения На чертеже приведена блок-схема предлагаемого устройства. Предлагаемое устройство для конт роля микропроцессорных. БИС содержит генератор 1 тестов, предназначенный для выработки тЮследовательностей синхронизации объектов и псевдослучайны} последовательностей, на базе которых фо1 1ируется тест. Выходы ге ратора 1 tecTOB соединены со входам блока 2 фО{ «йрованйя входных сигналов, обеспечивающего згшоминание набора сигналов, соотвётствунлцего текущему такту теста, и приложение его к выводам контролируемой БИС 3 и ОДНОТИПНОЙ эталонной ВИС 4, Выводы Обеих БИС подключены соответ.ст венно ко входам первого 5 и второго 6 блоков перекодировки данных:, которые обеспечивают перекодировку выход-: ных сигналов ВИС в двухразрядный двоичный код. Выходы первого 5 и второго б блоков перекодировки данных соединены с соответствуквдими входами Злока 7 сравнения, который сложит для обнаружения логического неравенства выходных сигналов контролируемой и эталонной БИС. Выход блока 7 сравнения соединен с одним из входов блока 8 управления, .йлкоды .эталонной ВИС 4 соединены со входами дешифратора 9 состояния выводов, предназначенного для анализа состояния двунаправленных выводов ВИС перед подачей на них входных сигналов, и с одним из входов блока 10 селектора адресов. Выход блока 10 селектора адреса соединен с одним из входов блока 11 памяти, имеющего также вход 2 Дляввода данных. Блок 11 памяти служит для хранения команд, реализуемых устройством, а также соответствующих данных и тестов, необходимых при контроле. Выходы блока 11 памяти соединены соответственно с одним из входов 8 управления, с одним из входов блока 2 формирования входных сигналов, с одним из входов генератора 1 тестов, с одним из входов блока 13 индикации,предназначенного для вывода результатов контроля. Блок 8 управления обеспечивает взаимодействие всех блоков устройства в процессе проверки путем выработки соответстБУ1с«дих управляющих сигналов и распределения команд и данных, поступающих из блоков 11 памяти по остальным блокам устройства. С этой целью выходы блока управления соединены соответственно с управлякядим входом блока 7 сравнения, управляющим входом блока 2 формирования входных сигналов, одним из входов генератора 1 тестов, одним из входов блока 13 индикации с одним из входов блока 11 памяти, с одним из входов блока Юселектора адресов. Предлагаемое устройство обеспечивает функциональный контроль БИС на псевдослучайных тестах, формируемых генератором 1 тестов на детерминированных тестах, задаваемых от внешнего источника (при большой длине теста или предварительно эаписайных в блок 11 памяти на детерминированных тестах, задаваемых в виде программно реализуемого алгоритма с помощью команд, хранящихся в блоке 11 памяти. Выполнение типовой программы контроля БИС на псевдослучайных. тестах происходит следующим образом. Входные выводы контролируемой 3 и эталонной 4 БИС (в том числе двунаправленные) подключаются к выходам блока 2 формирования входных

сигналов Выходные выводы контролируемой 3 и эталонной 4 БИС { в том числе двунаправленные) соединяютдя соответственно со входами первогбБ и второго 6 блоков перекодировки данных, в блок 11 памяти записываются последовательности команд, обеспечивающие программирование следующих операций: задание последовательности синхронии контролируемой и эталонной БИС; задание псевдослучайного теста путем установки требуе мого начального состряния генератора 1 тестов, алгоритма формирования псевдослучайной пбследовательнсхзти и ее длины; запуск генератора тестов с целью приложения к выводам контролируемой и эталонной БИС псевдослучайного теста, определяемого соответствующими начальным условиями;приложение к выводам контролируемой и эталонной БИС, указанной в программе последовательности сигналов привадения БИС в известное начальное состояние.

После запуска устройства, с помощью соответствующих команд программы производится засылка в генератор тестов начальных условий, определяющих псевдослучайный тест и последовательность сигналов синхронизации. После этого из блока 11 памяти поступает последовательность команд и данных, с помощью которой на входы к онтролируемой и эталонной БИС через блок 2 формирования входных, сигналов подается соответству ощая последовательность сигналов, приводящая обе БИС в известное начальное состояние. Затем генератор 1 тестов по команде из блока памяти обеспечивает приложение к входам контролируемой и эталонной БИС псевдослучайного теста. , В п оцессе приложения теста к входам контролируемой и эталонной БИС в каждом его такте сигналы с одноименных выходов БИС поступают в блоки 5 и б перекодировки данных, где перекодируются в двуразрядные двоичн КОДУ, которые затем сравнивайтся в блоке 7 сравнения. Если в тс а ком-либо такте теста обнаруживается неравенство значений сигналов на одноименных выходах БИС, то генератор 1 тестов ос11Г4на.вливается, и блок индикаци сигнализирует о неисправности контролируемой БИС 3. При этом в каждом такте проверки дешифратор 9 состояния выводов выявляет те выводы эталонной БИС 4, которые в данный момент находятся в .состоянии логической 1 или О, и сообщает об этом в блок 8 управления, который выдает соответствующий сигнал в блок 2 формирования входных сигналов, запрещакяций подавать в данном такте на указанные выводы какой-либо двоичный сигнал. .

При проверке БИС на детермирированных тестах, задаваемых от вг1ешнего источника программ или предварительно записанных в блок памяти, запуска генератора тестов не производится. Последовательность наборов входных сигналов контролируемой и эталонной ВИС 3 и 4 задается через блок 2 формирования входных сигнало непосредственно с помощью команд и данных программ также, как это имее место в случае последовательности приведения БИС 3 и 4 в известное начальное состояние.

Контроль микропроцессорной БИС на детерминированных тестах в общем случае требует тесты очень большой длины. Так, например только при проверке программного счетчика и регистровой памяШ микропроцессора Лп1.е& 3080 необходимо соответственно 262ilO H 50-10 детерминированных кодов, а для проверки всего микропроцессора требуется не менее 1 10 кодов. Для хранения тестов такой длины необходим очень большей объем памяти. Если же в процессе проверки вводить в блЪк памяти проверочный тест из какого-либо внешнего устройства (например, с магнитны дисков или от другой внешней памяти по частям, то время ввода будет большим, что ухудшает производительность устройства. Так для переписи с магнитного диска в блок 11 памяти теста обьемом потребуется время около 50 с, в дополнение к времени выполнения теста. С целью сокращения времени проверки БИС путем минимизации объема вводимых данных, определяющих тест, в предлагаемом устройстве предусмотрен еще один способ получения детерминированных тестов с помощью алгоритма, программно реализуемого эталонной БИС совместно с блоком 11 памяти. Этот способ применим в тех случаях, когда проверяемая(и соответственно эталонная БИС)представляет собой устройство, способное обеспечить выборку программы из внешней по отношению к- нему памяти и выполнение программы. К таким БИС относятся однокристальные микропроцессоры, контролеры внешних устройств ЭВМ и некоторые другие.

При контроле на детерминированных тестах, .задаваемых в виде программно реализуемого алгоритма, в блок 11 памяти устройства, кроме команд, обеспечивающих начальную уста; овку БИС и требуемую последовательность синхрониза ции, вводятся команды, обеспечивающие алгоритмическую генерацию тестов. Объем памяти, необходимый для хранения указанных команд, незначителен. Так для микропроцессора типа diTteb 3080 он составляет (без учета, управляющих

микрокоманд) всего лмль 1,4 байта. При алгоритмическом способе-контроля последовательность требуемого контрольного теста формируется с помощью эталонной БИС 4, которая вместе с блоком 11 памяти устройства образует микро-ЭВМ. Сигналы, возникающие на входах эталонной БИС при выполнении этой микро-ЭВМ заданной программы,. прикладываются в качестве теста ко входам проверяемой ВИС. Выходные сигналы эталонной БИС также, как и при других рассмот енных ранее способах формирования тестов, используются в качестве эталонных сигналов с которыми сравниваются выходные сигналы проверяемой БИС.

При выборе программы алГоритмической генерации теста проверяемая БИС условно разделяется на внутреннее модули, к которым обеспечивается досту с помощью соответствующих команд. Контроль ВИС заключается в проверке выполнения характерных для каждого е модуля команд, так для-проверки модуля программного счетчика микропроцессора dnteC. 8080 достаточно убедится, что его содержимое может постепено увеличиваться до максимального значения. Для выполнения этого теста в программе необходимо всего 6 команд, часть из которых повторяется многократно, что требует, естественн небольшого объема памяти и незначительного времени на перезапись программы из внешнего запоминающего устройства. (Общее число команд в программе микропроцессора ЗпЬеЙ. 8080, необходимое для его контроля методом алгоритмической генерации тестов 100)..

Вьтолнение типовой программы функционального контроля на основе алгоритмической генерации тестов в предлагаемом устройстве осуществляется следующим образом.

В блок 11 памяти вводятся команды обеспечи-вагацие начальную .установку контролируемой и эталонной БИС, заданную последовательность синхронизации, а также программа (на языке проверяемой ВИС, обеспечив гацая управление процессом контроля, в том числе генерацию контролирующего теста на выводах эталонной ВИС . 4.

После запуска устройства по сигнгшу блока 8 управления из блока 11 памяти .извлекаются соответствующие команды и данные,, которые поступают через блок .2 формирования входных сигналов на выводы контролируемой 3 и эталонной 4 ВИС и устанавливают их в одинаковое известное начальное состояние. Далее из блока 11 поступает первая команда программы алгоритмической генерации теста, которая передает управление процессом выборки и выполнения программы эталонной ВИС 4. При этом блок 10 селектор адресов осуществляет коммутацию соответствующих выводов эталонной БИС со входами блока 11, обеспечивая тем самым возможность выборки из блока 11 команд и данных программы алгоритмической генерации тестов в соответствии с управляющими сигналами и адресами, поступающими с выводов .эталонной ВИС, а такж передачу данных от этой БИС в блок 11. После передачи управления эталонной ВИС начинается выборка и выполнение последуквдих команд программы алгоритмической генерации теста. Команда и данные этой программы .постпают на соответствующие входьл эталонной БИС через блок 2 формирования входных сигналов. Эти :i.e команды и данные подаются на входы проверяемой БИС. Выходные cHPHaJiu обеих ВИС после их перекодировки блоками 5 и 6 сравниваются блоком 7также, как это имеет место и при других способах формирования тестов. Аналогичным образом протекает работа и дешифратора 9 состояния выводов, который управляет процессом приложения сигналов к двунаправленным выводам o6ekx ВИС. Выполнение программьа алгоритмической генерации теста заканчивается .либо при обнаружении несовпадения выходных сигналов ВИС блоком 7 (в этом случае блок 8 управления останавливает генератор синхронизации, входящей в состав генератора 1 тестов), либо по команде передачи управления блоку 8. После этого выборка команд из блока 11 памяти обеспечивается уже не эталонной БИС,а блоком 8.

Введение в предлагаемое устройство с дешифратора состояния яыводов селектора адресов и двух блоков перекодировки данных позволяет повысить достоверность и быстродействие контроля, а также- обеспечить проверку ВИС на их рабочих частотах. Быстродействие по сравнению с известным устройством повышается примерно в 5 раз. Например, проверка с помощью известного устройства микропроцессора .Л 2- 8080 на тестах, хранящихся во внешнем запоминающем устройстве требует, как отмечалось выше, не менее 50 с. в то время как контроль на алгоритмически генерируемых тестах с помощью предлагаемого устройства - примерно 10 сек.

По сравнению с известным предлагаемое устройство-требует меньшего .объема внутренней памяти, за счет меньшего количеств,:. команд в программе,- необходимой для реализации процесса контроля.

Формула изобретения

Устройство для автоматичесгкого контроля больших HHTeipa.ribffbix ::х(м.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Устройство для контроля цифровых объектов | 1974 |

|

SU546888A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для контроля параллельных микропроцессорных интерфейсов | 1982 |

|

SU1040489A1 |

| Устройство для формирования тестов | 1974 |

|

SU477413A1 |

| Устройство для автоматического контроля цифровых объектов | 1977 |

|

SU656063A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

Авторы

Даты

1981-01-23—Публикация

1978-05-15—Подача