I;

Изобретение, относится к вычисли- тельной технике и может использо- ваться в устройствах с непозиционным представлением информагр1и, в устройствах контроля по модулю

Цель изобретения расширение функциональных возможностей лутем обеспечения суммирования по произвольному модулю и повьпоения быстро- действия о :

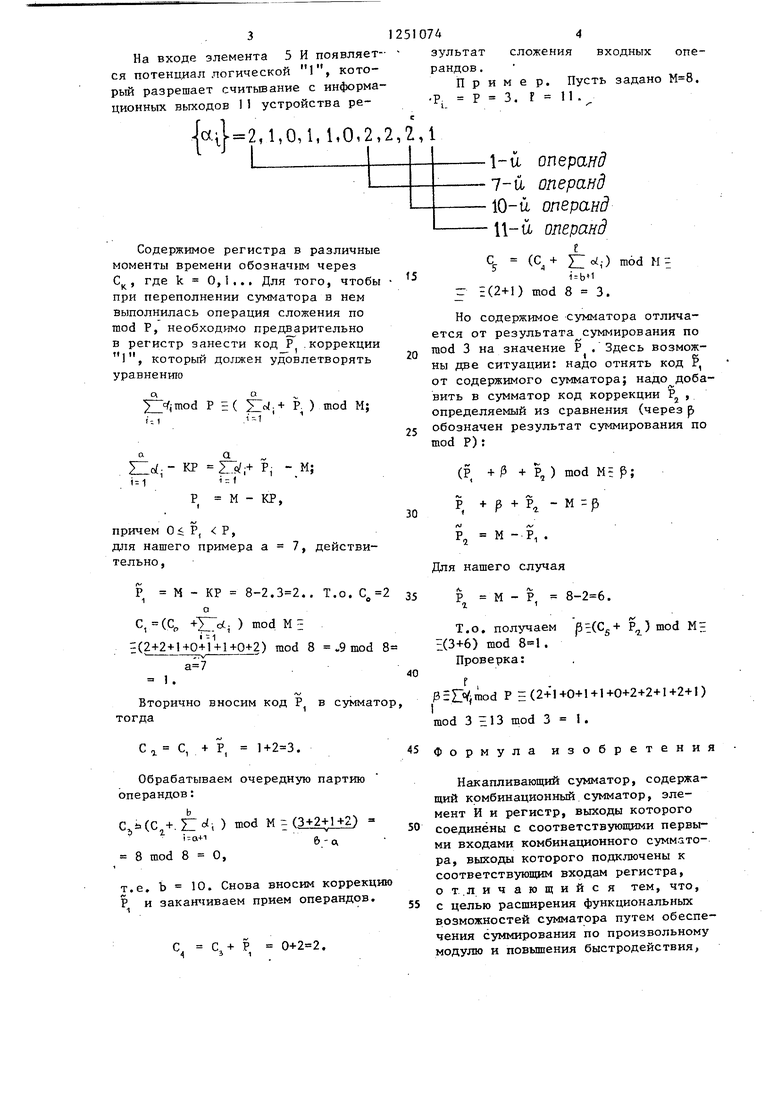

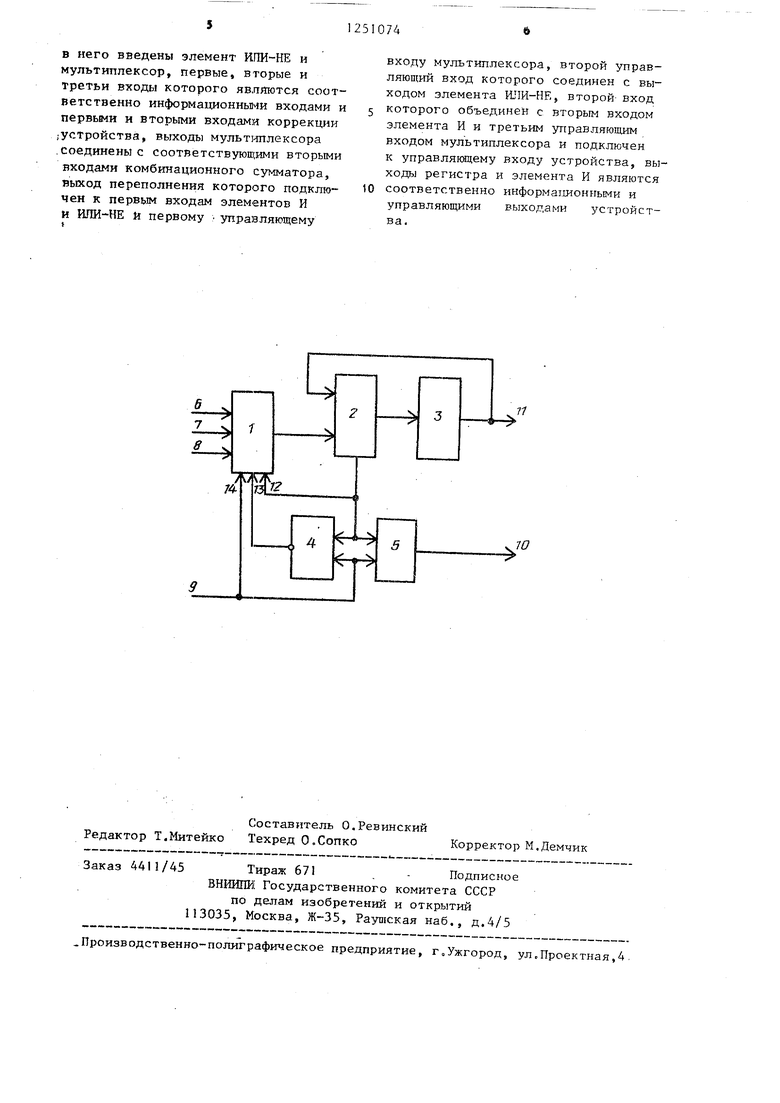

На чертеже представлена функциональная схема предлагаемого устройства.

Накапливающий сумматор содержит мультиплексор 1, комбинационный сумматор 2, регистр 3, элемент 4 ИПИ-НЕ, элемент 5 И, информационные входы 6, первые и вторые входы 7 и 8 коррекции, управляющий вход 9, управляющий выход 10р информационные входы П устройства, первый 12, второй 13 и третий 14- управляющие входы мультиплексора I,

Модуль М комбинационного сумматора 2 выбирается больше модуля Р/

1

/ Jу с тройства BJ х , где I - среднее количество входных кодов (операндов), а Z - ближайшее целое число, не прев.ышающее Z,

Накапливающий сумматор работает следующим образом

В исходном состоянии в регистр 3 занесен код Р коррекции I , на информационных входах 6, входах 7 и 8 коррекции выставлены коды первого операнда коррекции I и коррекции 2 соответственно. На всех остальных входах и выходэ-х устройства и входящих в него блоках (за исключением выхода блока 4, вторых входов комбинационного сумматора 2 и входов регистра 3) присутствуют потенциалы логического О, Потенциал логической 1 с выхода элемента 4 ИЛИ-НЕ поступает на второй управляющий вход 13 мультиплексора 1 и подключает информационные входы б устройства к вторым входам комбинационного сумматора 2. Код первого операнда присутствует на входах регистра 3, В первом такте код первого операнда записывается в регистр 3 без изменений Перед вторым и последующими тактами работы на информационных входах устройства выставляются второй и последующие операнды, которые в каждом так

51074

те работы устройства суммируются с содержимым регистра. В случае переполнения комбинационного сумматора 2 потенциал логической с его

-5 выхода переполнения поступает на первый упракляющий вход 12 мультиплексора 1 и снимает потенциал логической 1 второго утгравляющего входа 13 мультгшлексора I, Следователь10 но, только на первом управляющем входе 12 мультиплексора 1 есть потенциал логической 1, под действием которого мультиплексор 1 подключает вход 7 коррекции к второму

t5 входу комбинационного сумматора 2. В следующем такте работы устройства содержимое регистра 3 суммируется с выставленным на входах комбинационного сумматора кодом Р. коррекции

20 5 причем

11

М - К-Р

i

Где К - целое число, выбираемое из условия р. , н записьшается в регистр 3, Таким образом вьтолняется промежуточная коррекция результата суммирования накапливающего сумматора. Дальнейшая работа накапливающего сумматора происходит аналогичным образоМс

По окончании суммирования с шины Конец приема 9 на вторые входы

элементов ИЛИ-НЕ 4 и И 5 поступает потенциал логической 1, тогда На выходах этих элементов присутствует потенгдаалы логических О, а на третьем входе управления 14 мультиплексора 1 есть потенциал логической 1, которьй подключает вход 8 коррекции 2 устройства к второму входу комбицационного сумматора. Код коррекции 2, равный

45

М - р. ,

суммируется с содержимым регистра 3 в каждом такте работы устройства. Сложение кода коррекции 2 с содержимым регистра 3 продолжается до появления единичного потенциала с выхода переполнения комбШ1ационного сумматора 2j который поступает на первые входы элементов 4 ИЛИ-НЕ и 5 И, Тое осуществляется конечная коррекция, и результат сложения операндов вводится в диапазон

(Oj-Pi

),

3

На входе элемента 5 И появляет-

ся потенциал логической 1, который разрешает считьюание с информационных выходов 11 устройства ре

с(.,1,0,1, 1,0,2,2Д,1

I J IIII

Содержимое регистра в различные моменты времени обозначим через С, где k 0,1... Для того, чтобы при переполнении сумматора в нем выполнилась операция сложения по mod Р, необходимо предварительно в регистр занести код Р .коррекции 1, который должен удовлетворять уравнению

ао

q jmod Р Е( 51«(|+ Р, ) mod М;

Elof - КР О,-+ Pi - М; Ы 1

Р М - КР,

причем О Р, Р,

для нашего примера а 7, действительно ,

Р М - КР 8-2... Т.о.

D

С, (С„ ) mod М Е 1

Но содержимое сумматора отличается от результата суммирования по mod 3 на значение Р . Здесь возможны две ситуации: над о отнять код f, от содержимого сумматора; надо доба вить в сумматор код коррекции Pj , определяемый из сравнения (через 25 обозначен результат суммирования по mod Р):

(Р + + р ) mod ME ; Р + + ,

30

35

Р, М -.Р, . Для нашего случая

Р М - Р, .

г

40

Т.О. получаем ( Р) mod Mf Е(3+6) mod . Проверка:

(2+2-1-1+0+1+1+0+2) mod 8 .9 mod 8

7 1.f

В Гч mod Р (2+1+0+1+1+0+2+2+1+2+1)

Вторично вносим код Р в сумматор, v

mod mod .

тогда С

С. + Р, .

5 Формула изобретения

Обрабатываем очередную партию операндов:

С,,ь(. i: о(О mod М 3 (3+2+1+2)

i--a+i6-0

8 mod 8 о,

т.е. Ъ 10. Снова вносим коррекцию Р и заканчиваем прием операндов.

S С,+ Р .

сложения входных опе

мер. Пусть задано . 3. F 11 . ,

1-й операнд

7-й операнд

10-й операнд

11-U операнд

Е

S А Ц-,-) m6d М5

ЬЬН Р г(2+1) mod .

Но содержимое сумматора отличается от результата суммирования по mod 3 на значение Р . Здесь возможны две ситуации: над о отнять код f, от содержимого сумматора; надо добавить в сумматор код коррекции Pj , определяемый из сравнения (через обозначен результат суммирования по mod Р):

(Р + + р ) mod ME ; Р + + ,

Р, М -.Р, . Для нашего случая

35

Р М - Р, .

г

Т.О. получаем ( Р) mod Mf Е(3+6) mod . Проверка:

f

Формула изобретения

Накапливающий сумматор, содержащий комбинационный сумматор, элемент И и регистр, выходы которого

соединены с соответствующими первыми входами комбинационного сумматора, выходы которого подключены к соответствующим входам регистра, от..личающийся тем, что,

с целью расширения функциональных возможностей сумматора путем обеспечения суммирования по произвольному модулю и повышения быстродействия,

в него введены элемент ИПИ-НЕ и мультиплексор, первые, вторые и третьи входы которого являются соответственно информационными входами и первьми и вторыми входами коррекции ;устройства, выходы мульт1 тлексора .соединены с соответствующими вторыми входами комбинационного сумматора, выход переполнения которого подключен к первьм входам элементов И И ИЛИ-НЕ и первому : заправляющему

входу мультиплексора, второй управляющий вход которого соединен с выходом элемента ИЛИ-НЕ, второй- вход которого объединен с вторым входом элемента И и третьим управляющим входом мультиплексора и подключен к управляквдему входу устройства, выходы регистра и элемента И являются соответственно информационными и управляющими выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю | 1982 |

|

SU1134939A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Арифметико-логическое устройство для умножения чисел по модулю | 2017 |

|

RU2653263C1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Линейно-круговой интерполятор | 1987 |

|

SU1462250A2 |

| Арифметическое устройство | 1987 |

|

SU1441397A1 |

Изобретение относится к вычислительной технике,, Оно позволяет расширить функциональные возможности накапливающих сумматоров цутем обеспечения суммирования по произвольному модулю и повысить быстродействие Накапливающий сумматор содержит регистр, комбинационный сумматор и элемен т И. Введение муль- тшшексора и элемента ИЛИ-НЕ обеспечивает возможность суммирования по любому основанию, а также повышение быстродействия. 1 ил.

Составитель О.Ревинский Редактор Т.Митейко Техред О.Сопко

Заказ 4411/45 Тираж 671- Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

.Производственно-полиграфическое предприятие, г,Ужгород, ул„Проектная,4

Корректор М.Демчик

| Сумматор по модулю | 1975 |

|

SU570052A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1984-07-30—Подача