4i liU

09

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1654835A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

Изобретение относится к области вычислительной техники и может использоваться при обработке информации, представленной модулярными кодами. Целью изобретения является расширение функциональных возможностей за счет вычисления позиционной характеристики модулярного кода. Поставь ленная цель достигается тем, что арифметическое устройство, содержащее мультиплексоры 1, 2, блок 3 коммутации, блок 4 умножения, сумматор-вы- читатель 5, регистр 7, имеет новую организацию связей. 1 з.п. ф-лы, 2 ил.

0 Я7

Фиг. 1

Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации, представленной в модулярном коде

Целью изобретения является расширение функциональных возможностей за счет вычисления позиционной харак теристики модулярного кода.

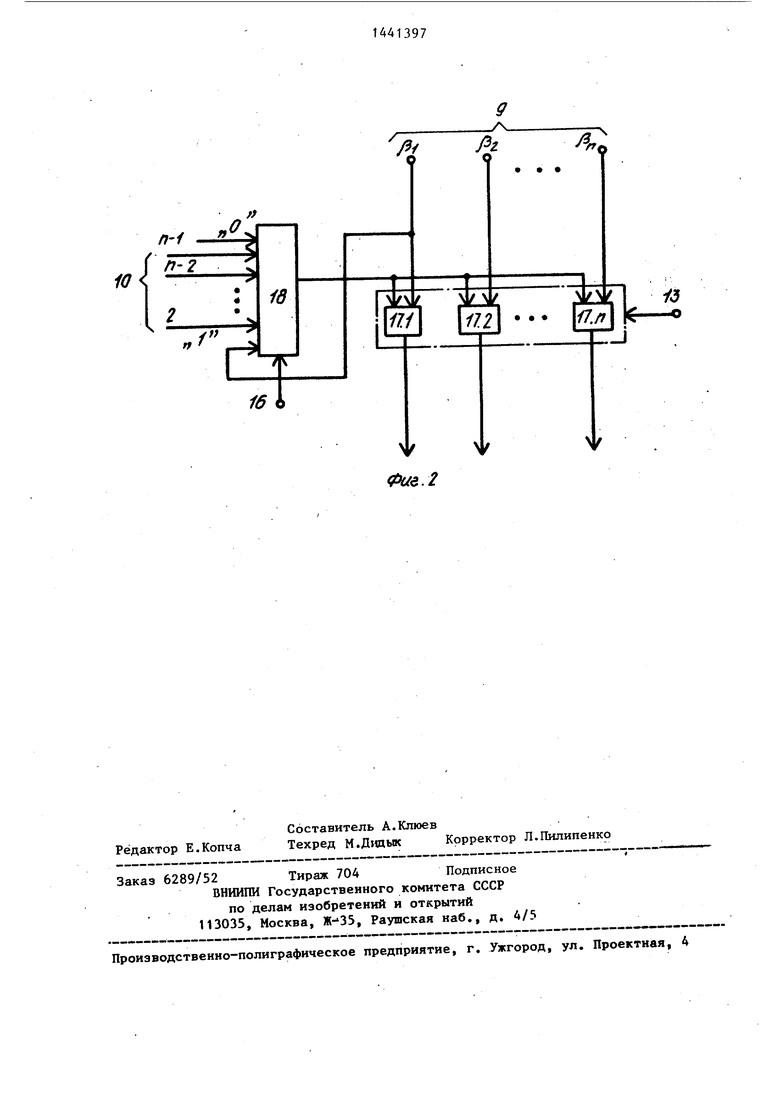

На фиг.1 представлена схема ариф- метического устройства на фиг.2 - схема одного из вариантов блока коммутации.

Арифметическое устройство (фиг.1) содержит мультиплексоры 1 и 2, блок 3 коммутации, блок 4 умножения, сум- матор-вычитатель 5, первый установоч ньй вход 6 устройства, регистр 7, вход 8 первого операнда устройства, вход 9 второго операнда устройства, выход 10 устройства, тактовые входы 11-15 устройства, второй установочны вход 16 устройства.

Блок 3 коммутации (фиг.2) содержи мультиплексоры 17 и 18.

В работе устройство (фиг.1) использует следующее.,

В модулярном коде число X представлено остатками от деления (наименьшими положительными вычетами)

числа на основания Р.

Р кода.

ч «

которые должны удовлетворять условию взаимной попарной простоты.

Для определения будем считать, что система оснований упорядочена, т.е Р, - ... Р„.

Арифметические операции над рандами А - (в,, ..., („) и В - (ft., ...,/3) выполняются параллельно и независимо над соответствующими па- 40 рами остатков od; и (5; , т.е.

с; /oii -f3i/p; , i Un,

где С г (С,,..., С„) - результат операции; : - операции сложения, вычитания

или умножения.

Для обеспечения возможности определить, в какой части диапазона

4-

( /Р„,гдеР .П Р- ,находится число 50 |-

X, будем вычислять позиционную характеристику вида

5

t()

(1) 55

Д РГ.И, ;ПР;( --.1 -i) целая часть.

Позиционную характеристику вычислим последовательно:

.(fxl4)

(1хГр ) -rVilMlpn)

i4X| Р,) - -р---J .

1Г

(2)

и-г1у| Р - .(1хГр„) V гМХ| .

Известно, что число X в позиЦион- ной системе счисления может быть представлено как п

Z гР

и

(3)

и; - базисные числа, для каждого из которых справедливо

KfeodP,-)Г(4)

г - некоторое число, такое, что

хе|-Гр„.

0

Р;

Р:

це™iPnР,Р;

t - 1

PI также целое число, а также то, что

Учитывая, что ft;

2,п, /3,

лее число при i

О.гс 1Г. () ftt

f

и что

имеет взаимопростые делители , процедура получения . « , (|х|р ) может быть распараллелена, т.е. представлена в виде независимых процедур получения остатков Т, , ...jIT, : ,

и ( Z:x;(i;|J, (j ). (5)

Учтем, что Jrt.lp; 15114- J. I f

p.

а так как I рГ

что Р| делится нацело

f

р- - О вследствие на любое

Р: , то

. J.

1

рг

(6)

Аналогично имеем

ipiC

1

рг

р,

(7)

,р.- О (j,i 2,п, i J). (8) С учетом (6)-(8) выражение (5)

примет вид

irj |(x-j -х.)

(9)

Д/П 1

11(1 )vnii применяя (9) eiiie г - 1 раз, получаем ofUiOKyiiiiocTii из п - г

.-ч -tl. t

остатков и р , .,., и но основаниям Р , . . ., У , KOTopF ie и определяют 5 характеристику n pCjxIp в непозиционном коде.

Мультиплексоры 1 и 2 аналогичны друг другу, каждый из них разрядносптью m J. При подаче высо10

кого логического уровня на входы 14 и 12 на выходах мультиплексоров .1 и 2 появляются кода.1, присутствующие на входах 8 и 9 соответственно. При подаче низкого логического потенциал на входы 1А и 12 на выходах мультиплексоров 1 и 2 появляются коды, присутствующие на выходе регистра 7 и входе 6 соответственно.

Мультиплексор 18 имеет п входов, каждый из которых разрядностью 3log Р„. Код на выходе мультиплек- сора 18 соответствует коду на одном из его входов. Подключение к выходу заданного входа определяется кодом на входе 16. Мультиплексор 17 аналогичен мультиплексорам 1 и 2.

Блок 4 умножения представляет собой rpyntiy из п умножителей по модулям Р. соответственно.

Сумматор-вычитатель 5 выполнен в виде п комбинационных сумматоров-вы- читателей по модулю Р,-. На его выхо- дах образуется либо сумма чисел, код которых сформирован на .выходах мультиплексора 1 и блока 3 коммутации, либо разность между числом, код которого сформирован на выходах мультиплексора 1 и числом, код которого сформирован на выходах блока 3 коммутации .

Регистр 7 представляет собой параллельный т-разрядный регистр, со держимое которого изменяется в момен смены потенциала на входе 11.

Устройство (фиг.1) работает следующим образом.

Режим сложения.

На входы 14 и 13 подан высокий логический потенциал, под действием которого на выходах мультиплексора 1 и блока 3 коммутации появляются коды остатков ot; и i; операндов А и В соответственно. На вход 15 подан высокий логический потенциал, под действием которого блок 5 вычисляет .сумму

,-

/П 1

5 10

15

20

30

а 25

gg

40

45

50

q/

одноименных остятков по модулю PJ . На 12 подается уровень логической единицы, поэтому на вход блока 4 умножения поступает код числа 1 с входа 6 устройства. Результат сложения из сумматора-вычитателя 5 умножается на единицу в блоке 4 умножения, и по окончании переходных процессов в указанных блоках на вход 11 подается короткий импульс, который защелкивает результат суммирования в регистре 7, после чего результат операции может быть снят с выхода 10.

Режим вычитания.

Режим вычитания отличается от режима сложения только тем, что на вход 15 перед подачей операндов А и В на . входы 8 и 9 соответственно подается уровень логического нуля, вследствие которого сумматор-вычитатель. 5 выполняет операцию вычитания.

Режим умноже ния.

При выполнении этой операции на входы 14, 15 и 12 подается высокий логический уровень, на вход 13 - низкий логический уровень, а на вход 16- код, по которому на выходе мультиплексора 18 формируется код числа 0. Таким образом, на выходе мультиплексора 1 появляется код числа А, присутствующего на входе 8, на выходе блока 3 коммутации - О, на выходе мультиплексора 2 - код числа В, присутствующего на входе 9. На выходе сумматора-вычитателя 5 по окончании переходных процессов появляется код числа А, а по окончании переходных процессов в блоке 4 результат произведения остатков ot; и rtj по модулю PJ в момент подачи импульса по входу 11 защелкивается в регистре 7.

Сложение, вычитание и умножение являются однотактными операциями, при вьшолнении которых сигналы на входах 6, 11-16 не изменяются.

При вычислении позиционной характеристики г на входы 13 и 15 поданы низкие логические уровни, под действием которых код на выходе блока 3 определяется кодом на выходе мультиплексора 18, сумматор-вычитатель 5 работает в режиме вычитания, а на выходе мультиплексора 2 присутствуют коды с входа; 6 ус-тройства.

На входы 8 и 9 подается код числа X, позиционная характеристика которого вычисляется.

На первом шаге на вход 16 подан код, под действием которого на выходе Гхпока 3 формируется код остатка х

f

На вход 14 подан высокий логический уровень, и на выходе мультиплексора 1 присутствуют коды остатков

0.

Таким образом, по окончании переходных процессов в блоках 1, 3 и 5 на выходе сумматора-вычитателя 5 будет сформировано значение

; - )1г

/(х; - х,)||. , i 2,п.

По окончании переходных процессов в блоке 4 на ег о выходе будут сформированы значения

1Г

|(х; - X,)-- 1

Pi

в момент поступления защелкиваются

Значение

импульса на вход 11 в регистре 7. После этого на вход 14 подается нулевой логический уровень, и он не изменится до окончания работы устройства.

На втором шаге на вход 16 подается код, под действием которого на вы- зо которого соединен с вторыми информационными входами первого, мультиплексора и блока коммутации, второй уп- На

ходе блока 3 формируется код числа

1Г

числа О, О,

вход 6 устройства (подаются 1

-1 1Рз |Рг1Р/ Таким образом, на выходе сумматора-вычитателя 5 будут сформированы

35

равЛяющий вход которого роединен с вторым установочным входом устройства, выход сумматора-вычитателя соединен с входом второго сомножителя блока умножения, пятый тактовый вход устройства соединен с управляющим входом сумматора-вычитателя.

в регистре 7.

Аналогично работа устройства продолжается до тех пор, пока не будет получено значение (,(.tx(p ) в модулярном коде,

Формула изобре те н и я

теля, выход второго мультиплексора

соединен с входом первого сомножителя блока умножения, вход первого операнда устройства соединен с первым

информационным входом первого мультиплексора, тактовые входы с второго по четвертый устройства соединены соответственно с управляющим входом второго мультиплексора, с перьым управляющим входом блока коммутации и с управляющим входом первого мультиплексора, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисЛенин позиционной характеристики модулярного кода, вход второго операнда устройства соединен с первым информационным входом блока коммутации и с первым информационным входом второго мультиплексора, второй информационный вход которого соединен с первым установочным входом устройства, выход блока умножения соединен с информационным входом регистра, выход

о которого соединен с вторыми информационными входами первого, мультиплексора и блока коммутации, второй уп-

5

0

5

0

g

равЛяющий вход которого роединен с вторым установочным входом устройства, выход сумматора-вычитателя соединен с входом второго сомножителя блока умножения, пятый тактовый вход устройства соединен с управляющим входом сумматора-вычитателя.

Фие.2

| Арифметическое устройство | 1975 |

|

SU601689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство в системе остаточных классов | 1985 |

|

SU1290315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-30—Публикация

1987-06-29—Подача