(54) ПРЕОБРАЗОВАТЕЛЬ даОИЧНОГО КОДА В ДЮИЧНО- ДЕСЯТИЧНЫЙ (ДВОИЮЮ-ДЕСЯГИЧНО-ШЕСГИДЕСЯГИРИЧНЫЙ) КОД

ющего сумматора, с первыми управляющими входами регистра, селектора-мультиплексора, регистра сдвига соответственно, а также через генератор тактовых импульсов с вторыми утфав ляющими входами соответственно накапливающего сумматора, регистра и регистра сдвига, группа инффмацирнных входов которого является первым информационным входом преобразователя, а выход младшего двоичного разряда

регистра сдвига соединен с третьим управляющим входом накапливающего сумматора, информационные входы которого, первая и вторая группы информационных входов комбинационного сумматора соединены с инффмационньши выходами регистра, входы которого подключены к выходам селектора мультиплексора, первая группа входов которого соединена с выходами комбинационного сумматора, а вторая группа входов является вторым информашкжньпм входом преобразователя, второй управЛЯЮ1ЦИЙ вход которого соединен с четвертым, управляющим входом накапдншающего сумматора и )гарав.ляющим входом комбинационного сумматора, выходы котсрьк являются выходами преобразователя.

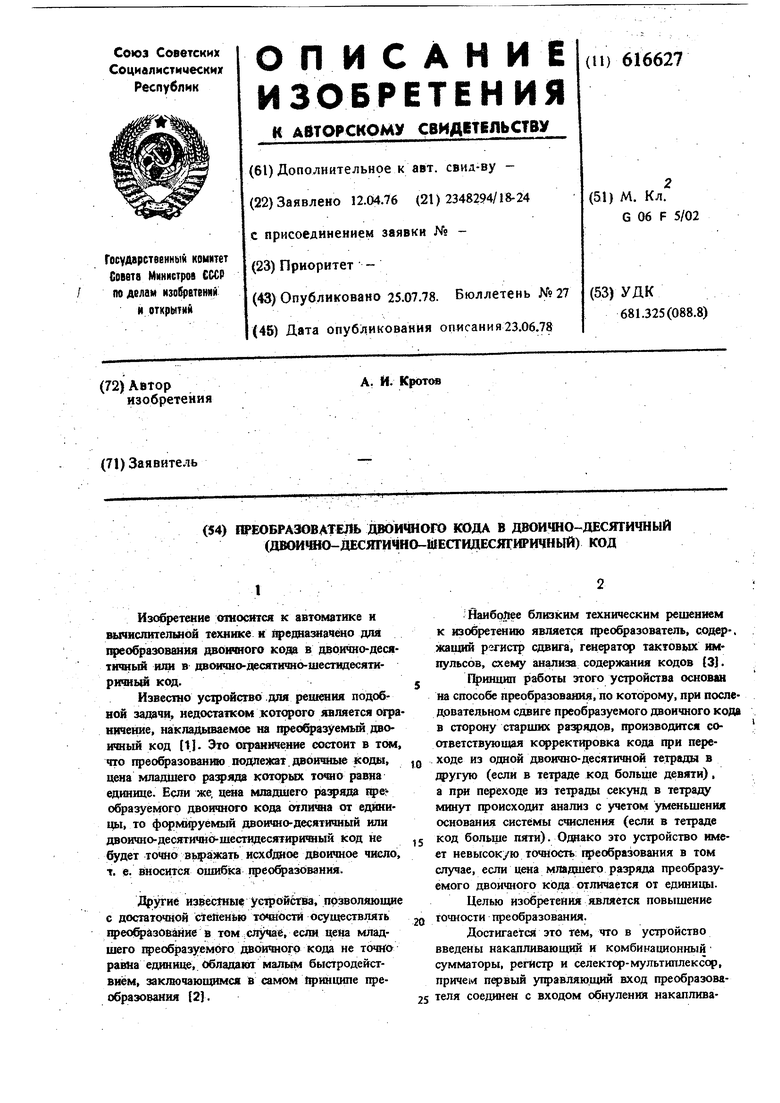

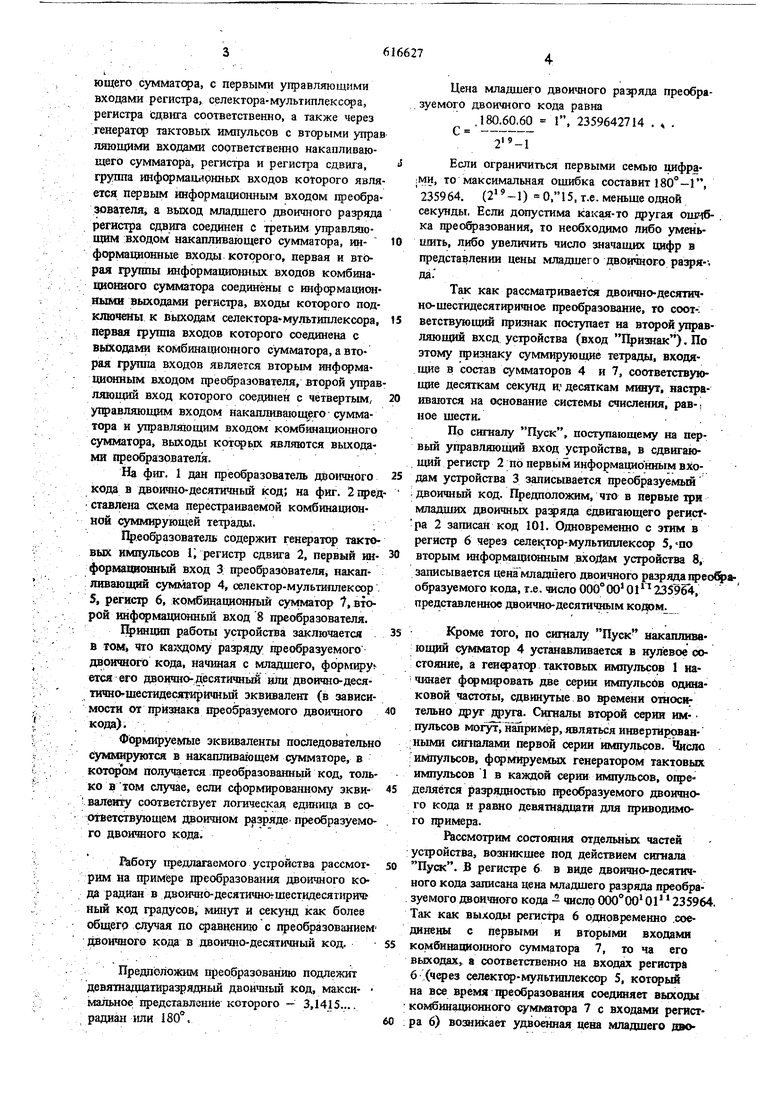

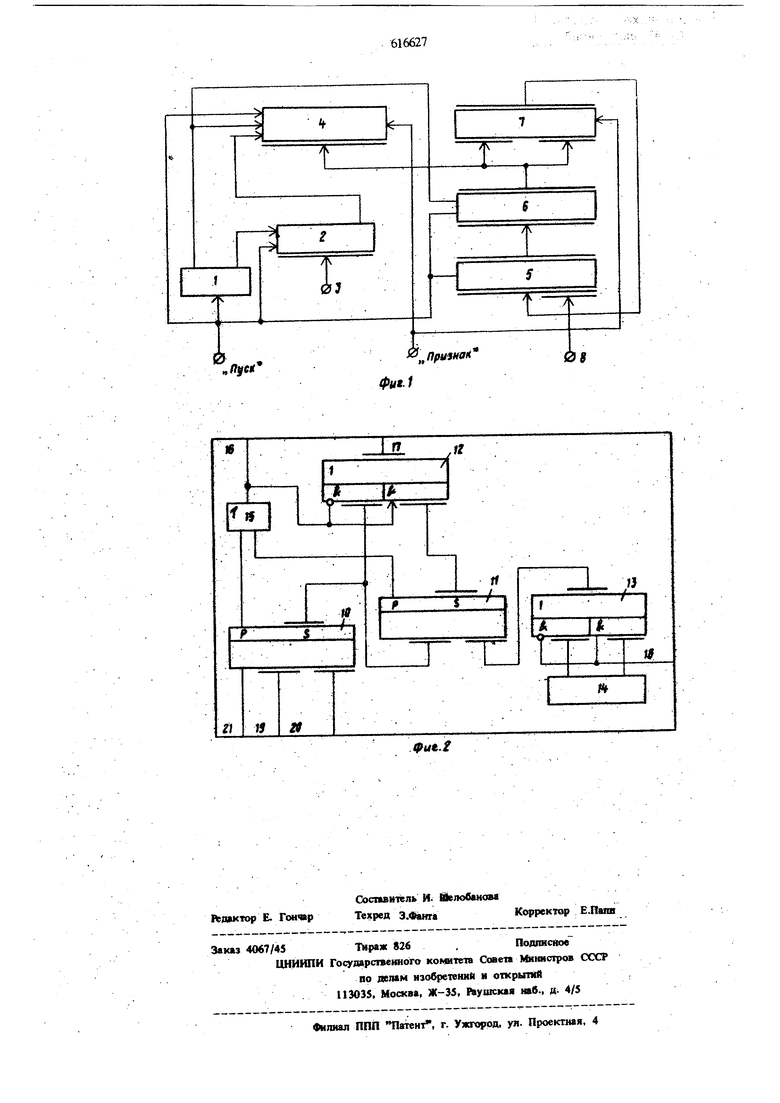

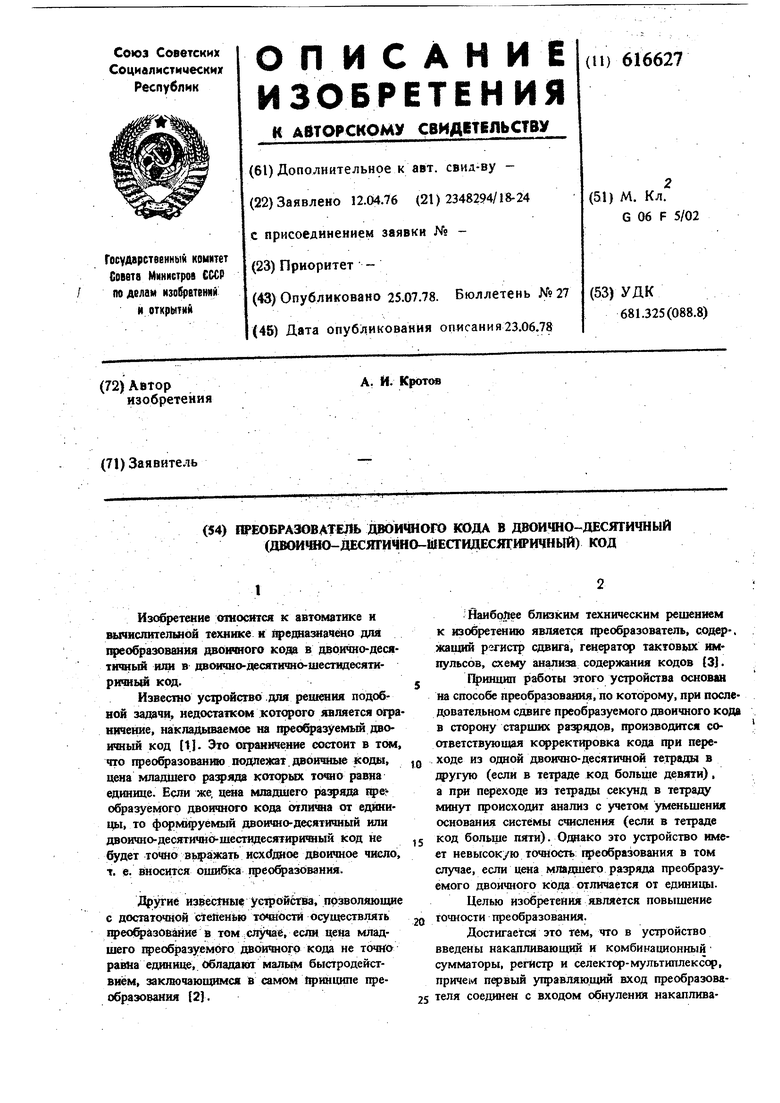

На фиг. 1 дан преобразователь двоичного кода в двоично-десятичный код; на фиг. 2 гфед: ставлена схема перестраиваемой комбинационной суммирующей тетрады.

П.еобразователь содержит генерак) тактовых импульсов ii регистр сдвига 2, первый шформа цяонный вход 3 преобразователя, накапливающий сумматор 4, селектор-мультиплексор 5, регистр 6, комбинационный сулшатор 7, второй инфс;)мацишный вход 8 преобразователя.

Принцип работы устройства заключается в TOMi что каждому разряду 1феобразуемого двоичного кода, начиная с младщего, формирую ется его двоично-десятичный или двоично-десятичн(миестщ(есятиричный эквивалент (в зависимости от прйзшака преобразуемого двоичного кода).

Формируемые эквиваленты последовательно суммируются в накапливающем о мматоре, в котором получается преобразованный код, только в том случае, если сформированному экви. валенгу соответствует логическая единица в соответствующем двричном разряде преобразуемого двоичного кода.

Каботу предлагаемого устройства рассмотрим на примере цреобразования двоичного кода радиан в двоичн6-десятичногшествдесятирич ный код градусов, минут и секунд как более общего случая по сравнению с преобразованием дйоичного кода в двоично-десятичный код.

ПредпЬломсим преобразованию подлежит девятнадцатиразрядный двоичньп код, макси- мальное представление которого - 3,1415.... радиан или 180°,

Цена младшего двоичного ра:фяда преобразуемого двоичного кода равна

180.60,60 1, 2359642714 . ч .

Р я: --,

Если ограничиться первыми семью цифра;ми, то максимальная ошибка сост1авит 180°-1, 235964, () 0,15,т.е.меньщеодной секунды, Если допустима какая-то другая ояибка 1фе образования, то необходимо либо уменьшить, либо увеличить число значащих цифр в представлении цены мдидшего двоичного разря--. да.

Так как рассматривается двоично-десятично-шестидесятиричное преобразование, то соот-; ветсгвующш признак поступает на второй управляющий вход устройства (вход Признак). По этому гфизнаку суммирующие тетрады, входящие в состав сумматоров 4 и 7, соответствующие десяткам секунд и, десяткам минут, настраиваются на основание системы счисления, рав-; ное щести..

По сигналу Пуск, поступающему на первый управляющий вход устройства, в сдвигающий регистр 2 по первьш информационнь1м вХодам устройства 3 записьшается преобразуемый i двоичный код. Предположим, что в первые три младших двоичных сдвигающего perncfра 2 записан код 101. Одновременно с этим в регистр 6 через селектор-мультиплекс 4) 5, «по вторым информационньпл входам устройства 8, записывается ценамладшего двоичного разряда 1феобразуемого кода, т.е. вдело 000° 00 01 235964, представленное двоично-десятич ць1м кодом

Кроме того, по сигналу Пуск накашшва ющий омматор 4 устанавливается в нулевое состояние, а генератор тактовых импульсов 1 начинает ф(м1фовать две серии кмпульсОв одинаковой частоты, сдвинутые во времени относ тельно друг друга. Сигналы втфой серии им- : пульсов могуГ, например, являться инвертирован:ными сигналами 1Юрвой серии импульсов. %ссло ; импульсов, формируемых генератором тактовых импульсов 1 в каждой серии импульсов, деляётся разр)1диостью преобразуемого двоичного кода и равно девятнадцати для приводимого гфимера.

Рассмотрим состояния отдельньк частей устройства, возникшее под действием сигаала Пу(ж. В регистре 6 в виде двоично-десятичного кода записана цена младшего разряда преобразуемого двоичного кода - число 000°00 01 23596 Так как выходы регистра 6 одновременно .соединены с первыми и вторыми входами комбинационного сумматора 7, то ча его выходах а соответственно на входах регистр 6 (через селектор-мультиплексор 5, который на все время преобразования соединяет выходы ; комбинационного суммат(фа 7 с входами регнст: ра 6) возникает удвоенная цена младщего двоOTHOro разряда - число 000°0002471928, т.е цена, соответствующая второму двоичному разряду преобразуемого KOjw. Выходы регистра 6 также соединены со входами накапливающего 1:умматора 4, т. е. цена младшего двоичного разряда гфисутствует на входах накапливающего сумматора 4. Так как в младшем разряде сдвигающего регистра 2 записана логичесжая единица, то на входе запрета накапливающего суммат( 4 присутствует сигнал разрешения сложения сумматс ом 4. По пфвому сигналу, поступающему с витого выхода генератсфа тактовых импульсов 1, накапливающий сумматор 4 щ)оизводит сложшие цены младшего двоичного с нулем, а в регистр 6 записывается удвоенная цена младшего двоичного . Следует atметить, что регистры 2 и 6 вьшолняются на такт||фуемых триггфах с внутршней задержкой : (срабатывание триггеров происходит после окая чания действия тактового сигнала). После ок Я1чаяия действия первого сигнала, с выхо да гжератора тактовых импульсов 1 поступает сигнал, по которому содержимое регистра 2 сдви 1гается на один в стораяу младших разрядов, т. е. во втсфом разряде станет логическая ещшица, а в первом - лшический иуль. Лоппеский нуль в младшем сдвигающего регистра 2 поступает на вход за1фета сложения накапливающего сумматора 4 и запрещает его работу. Таким образом, в результате действйя второго сигнала со выхода генератора 1 в накапливающем сумматоре 4 остается цена младшего двоичного разряда преобразу1гмого кода, а в регистр 6 запишется с выхо да комбинационного сумматора 7 учктв&реивгм ofsaa младшего двоичного разряда - число 000° со 04 943856, т.е. цена,. сЬответсгвующая третьему двоивдому разряду ; преобразуемого .кода. Затем, иод действием сигнала с первого выхода генфатора 1, содфжимое регистра 2 сдвигается на один разряд в сторону младших, т. е. в младшем разряде станет логическая единиш и т. д. Таким образом, младашй двоичный разряд сдвигающего регистра 2, в KotqOM записан пре образуемый код, рафешает (при иаличии в нем лсчгнческой единицы) накапливающему .сумматору 4 складывать последовательно формируемые (с помощью регистра 6 и комб1гааци(яшого сум матсфа 7) цены двоичных раундов преобразуемого кода. Как видно из работы устройства, процесс црео азования занимает девятнадцать (в соот.ветствии с разрядностью преобразуемого двоичного кода) периодов тактовой частоты, задаваемой генератором тактовых импульсов 1. В результате работы предлагаемснх) устройства в накапливающем сумматоре 4 фсфк1щ уется дво кчно-десятично-шестидесятиричный код, т. е. код градусов, углов и минут. Как видно из описания предлагаемого устройства, можно получить любую требуемую точность преобразования. На фиг. 2 приведен пример возможной реализации перестраиваемых комбинационных суммирующих тетрад, входящих в состав сумматс ов 4 и 7, поскольку накапливающий сумматор 4 может бьггь построен на основе комбинационного сумматора и регистров памяти. Перестраиваемая суммирующая тетрада 9 состоит из двух комбинационных сумматоров 10 я 11 на четьфе двоичных разряда, двух сепекторов-муга тш1лексоров 12 и 13, источника логических констант единицы и нуля 14 и злементг ИЛИ 15. Выходы сумматсфа 10 соединены с первой группой входов сумматора 11, а также с первой группой входов селектора-мульТ1шлекс( 12. Вторая группа входов селект замуш типлексора 12 соединша с выходами сумматс а И, вторая qpynna входов соедашена с выходили селектора-мультиплексора 13, первые и вторые гругаш входов которого соединены с источником логических констант единшо 1 и HyJM 14. Выход сигнала переноса сумматора 10, а так аналогичный выход сумматора 1 через злемеит ИЛИ 15 поступают на выход 16, являшпошся выходом сигнала переноса рассматриваемой суммирующей тетрады 9. Кроме того, вьЕХод злемигга ИЛИ 15 соединен c шгрерсным и входами селектора-мультиплексора 12, у|фавл ш)щими соответственно подкшочением выходов сумматора 10 или выходов сумматора М, через селектор-мультиплекс 4 12, на выход 17 рассматриваемой суммирующей тетрады 9. Вход 18, управляющий изM ieHiteM основания системы счисления рассматрнваемш суммирующей тетрады 9, соедини с и прямым входами селектора-мультишюксора 13, управл ощими соответственно подключением первых шга вторых rpymi входов селектс -мультщшексора 13 на его выхощл. Пфвая.19, вторая 20 группы входов, а также вход 21 сшнала нероюса суммат(фа 10 являются входами рассматриваемой суммирующей тетрады 9.. Назначение отдельных схем, входящих в соста:в ; пересматриваемой: сумм1фующей тетрады 9 следующее: сумматор 10 производит сложение кодов чисел, поступающих по входам 19 и 20; сумматор 11 корректирует двоичный код с выхода сумматора 10, если на выходе cjfMMaтора 10 сформировался двоичный код больше девяти или больше пяти, в зависимости от того, настроена суммирующая тетрада 9 по входу 18 на основание системы счислйшя десять или шесть; селектор-мультиплекссф 13, в зависимости от при:жака, подк1аочает на вход сумматора 11 или двоичный код ОНО - число 6 для десятичной системы счисления, или код коррекции 1010 - число 10 для шестиричной системы счисления; коды коррекции формируются от источника логических констант единицы и нуля 14, в качестве которого может выступать источник питания и соответственно его верхний и нижний уровни напряжения; селектор-мультиплексор 12 подключает на выходы 17 суммирующей тетрады 9 выходы сумматора 10, а на время действия сигнала переполнения, поступающего с выхода элемента ИЛИ 15, - выходы сумматора 11. Для большей наглядности рассмотрим конкретный числовой пример. Пусть рассматриваемая суммирующая тетрада 9 входит в состав комбинационного сумматора 7, подключенного к выходам регистра 6. Допустим, что суммирующая тетрада 9 формирует код десятков секунд (минут) при двоично-десятично-щестидесятйричном преобразовании, о чем свидетельствует соот ветствующий признак на входе 18, поступающий с второго управляющего входа устройства (вход Признак на фиг. 1). Пусть в процессе предыдущей работы в четырех двоичных разрядах ста тического регистра 6, соответствующих десяткам секунд (минут) сформировался код 0100 - чиело 4. Этот код поступает на одноименные первые 19 и вторые 20 группы входов сумматора 10. Пусть также на вход сигнала переноса 21 суммат фа 10 поступает сигнал переноса с предыдущей младшей суммирующей тетрады, входящей в состав комбинационного сумматора 7, соответствующей единицам секунд (лотнут). Тогда сумматор 10 формирует на выходе двоичный код 1001 - число 9. Сумматор 11 суммирует код 1001 с кодом коррекции 1010 - чиело 10, т. к. мы рассматриваем суммирующую тетраду 9, формирующую коды десятков секунд (минут) и поэтому настроенную по входу 18 на основание системы счисления щесть. Посколь ку результат сложения сумматора И, равный 19, превышает число 15 - максимальное десятичное число, которре может быть выражено четырьмя двоичными разрядами сумматора П, то последний формирует на выходе код ООП - число 3, а также сигнал переполнения, по которому се лектор-мультиплексор 12 подключает выходы сумматора 11 на выходы 17. Кроме того, сигналпереполнения сумматора 11 через элемент ИЛИ 15 поступает на выход 16, фор мирующий сигаал переноса для следующей сум М1фующей тетрады, являющейся тетрадой единиц минут (единиц градусов). Таким образом, на выходе рассматриваемой суммирующей тетрады 9 формируется код ООП - соответствующий трем десяткам секунд (минут) и сигнал переполнения, соответствующий одной минуте (градусу). Формула изобретения Преобразователь двоичного кода в двоично десятичный (двоично-десятично-щестидесятиричный}код, содержащий регистр сдвига, генератор тактовых им10льсов, о т л и ч а ю щ и йс я тем, что, с целью повьпцения точности преобразования, в него введшы накашшваюцдай и ком6ш(ационный сумматоры, регистр и селектор-мультиплексор, npmetA первый управляощий вход преобразователя соединен со входом обнуления накаплнва(ощего суммгаоря, с первы-ми управляющими входами регистра, селектсфамультиплексора, регистра сдвига, соотвётстведио, а также через генератор тактовых икотульсов с у1фаВляю1Ш Ми входами соответственно накапливающето сумматора, регистра и регистра сдвига, группа шформ ацисншых вх(ь дов которого является Инффмащкншым входом преобразователя, а выход младшего: двоичного разряда регистра сдвига срединён с ipeтьим у1фавляющим входом накапливэдащего сумматсра, инфс мациоииые входы )pro, первая и вторал группы {фдрмацкониых входов комбинациошого сумматсфа соединены с информационньши выходами регистра, ЕОСОДЫ которого подключены к выходам селекторамультиплексора, первая группа входов котсфого соединена с выходами комбшадионмого сумматора, а вторая группа входов является втб-, рым информационным входом прес разователя, второй управляющий вход которого соединен с четвертым управляющим входом накапливающего сумматора и управляющим входом комбинационного сумматора, вь1хрды которых являются выходами преобразователя. Источники информащи, принятые во; анимание при экспертизе: / 1.Авторское свидетельство СССР If 152126, М.КЛ G 06 F 5/02, 1962. 2.Авторское свидетельство СССР N 190054, М.кл G-06 F 5/02, 1966. 3.AjBTq ;кое свидетельство СССР N 144642, М.кл G 06 F 5/02, 1960.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

Авторы

Даты

1978-07-25—Публикация

1976-04-12—Подача