блоков коррекции, управляющие вЬсоды которых соединены с прямьм выходом I S-триггера, выходы тактирования сумматора и тактирования распределителя импульсов соединены соответственно с тактовыми входами сумматора и распределителя импульсов, пятый и .шестой входы шифратора блока управ1200428

ления соединены соответственно с прямыми выходами первого и второго ЗК-триггеров, 3 -входы которых соединены с первым и вторым- вьпсодами шифратора блока управления, пятый и шестой выходы которого соединены соответственно с R-входами первого и второго ЗК-триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1149243A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ .кодов в . ДВОИЧНО-ДЕСЯТИЧНЫЕ, содержащий элементы И-НЕ по числу разрядов двоичного кода, шифратор, распределитель импульсов, накапливающий сумматор, блоки коррекции, причем информационные входы преобразователя соединены с первыми входами соответствующих элементов И-НЕ, входы которых соединены с входами первой группы входов шифратора соответственно., вторые входы элементов И-НЕ, соответствующих тем разрядам двоичного кода числа, двоично-десятичные эквиваленты которых не имеют единиц в .своих одноименных разрядах, соединены между собой и подключены к соответствующему разряду группы выходов распределителя импульсов, выходы 1-й группы выходов шифратора () где N - количество десятичных разрядов числа, соединены с информационными входами 1 -и тетрады накапливающего сумматора, выходы которой соответственно соединены с информационными входами 1 -го блока коррекции и выходами i-и группы выходов преобразователя,выход каждого блока коррекции соединен с соответствующим входом BTOpoij группы входов шифратора, отличающийся тем, что, с целью расширения области устойчивой работы, он содержит RS-триггер, элемент И-НЕ и блок управления, состоящий из шифратора и двух ЗК-триггеров, причем тактовый вход преобразователя соединен с синхровходами первого и второго ЗК-триггеров и первьм входом шифратора блока управления, второй вход которого является входом пуска блока управления и соединен с управляющим входом преобразователя, выходы с первого по пятый шифратора блока управления являются соответственно сл выходом начальной установки, выходом разрешения сложения, выходом разрешения коррекции, выходом тактирования сумматора и выходом тактирования, распределителя импульсов блока управления, выход начальной ycTanoBKjH , блока управления соединен с входа- ми начальной установки распредеf лителя импульсов и накапливающего D |а сумматора, выходы разрешения суммирования и разрешения коррекции блока управления соединены соответственно Е. с R и 5-входами RS-триггера, инверсХ) ный выход которого соединен с управляющим входом распределителя импульсов, выход которого соединен с третьим входом шифратора блока управления и является входом окончания опроса блока управления, вход необходимости коррекции которого, являющийся четвертым входом шифратора блока управления, соединен с выходом элемента И-НЕ, входы которого соединены с выходами соответствующих

Изобретение относится к области автоматики и вычислительной -техники и может быть использовано при построении устройств обработки числовой информации.

Целью изобретения является расширение области устойчивой работы.

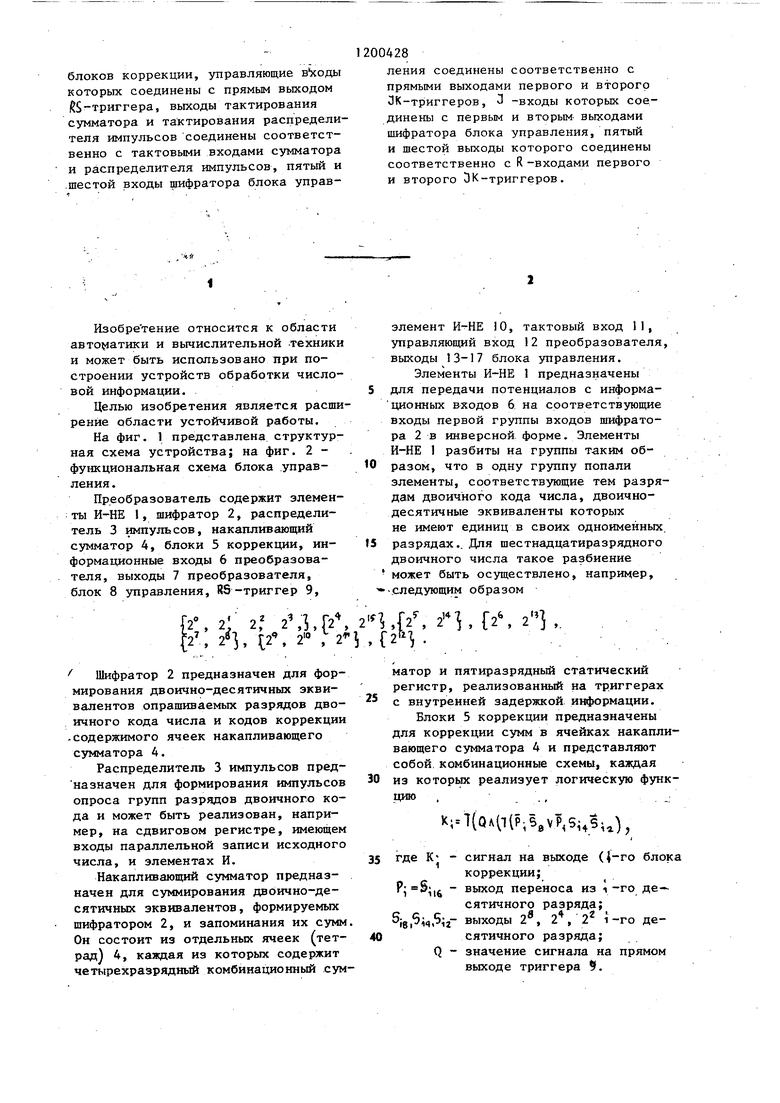

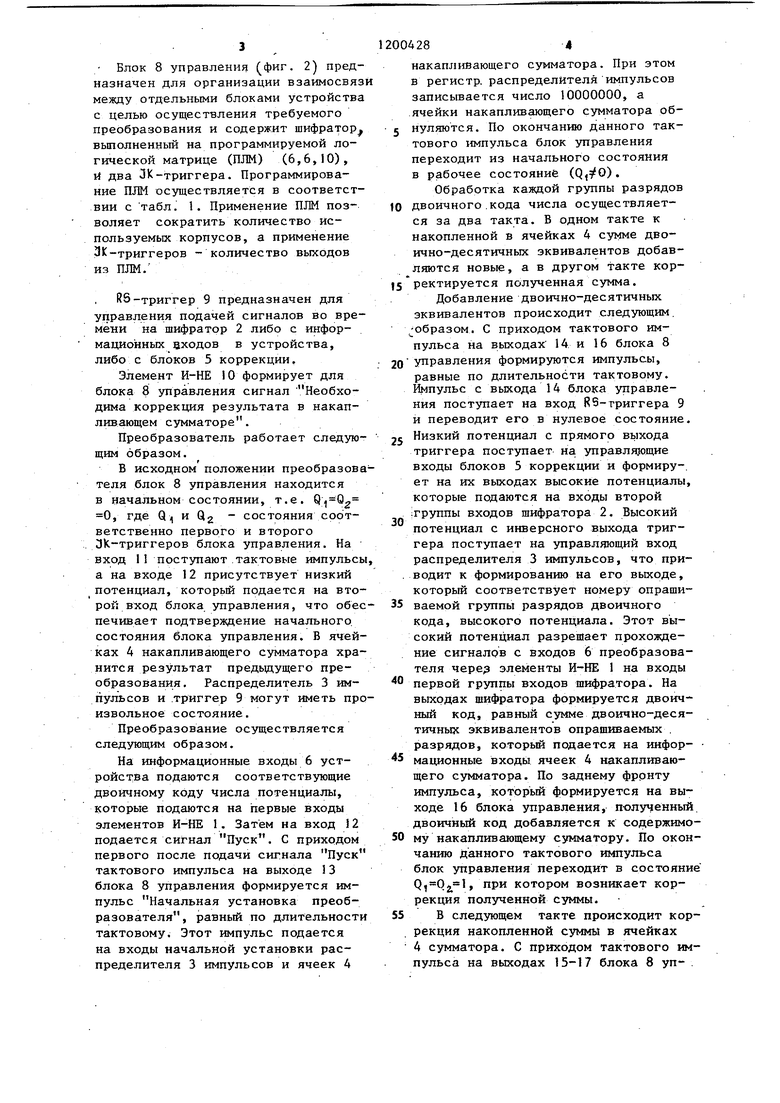

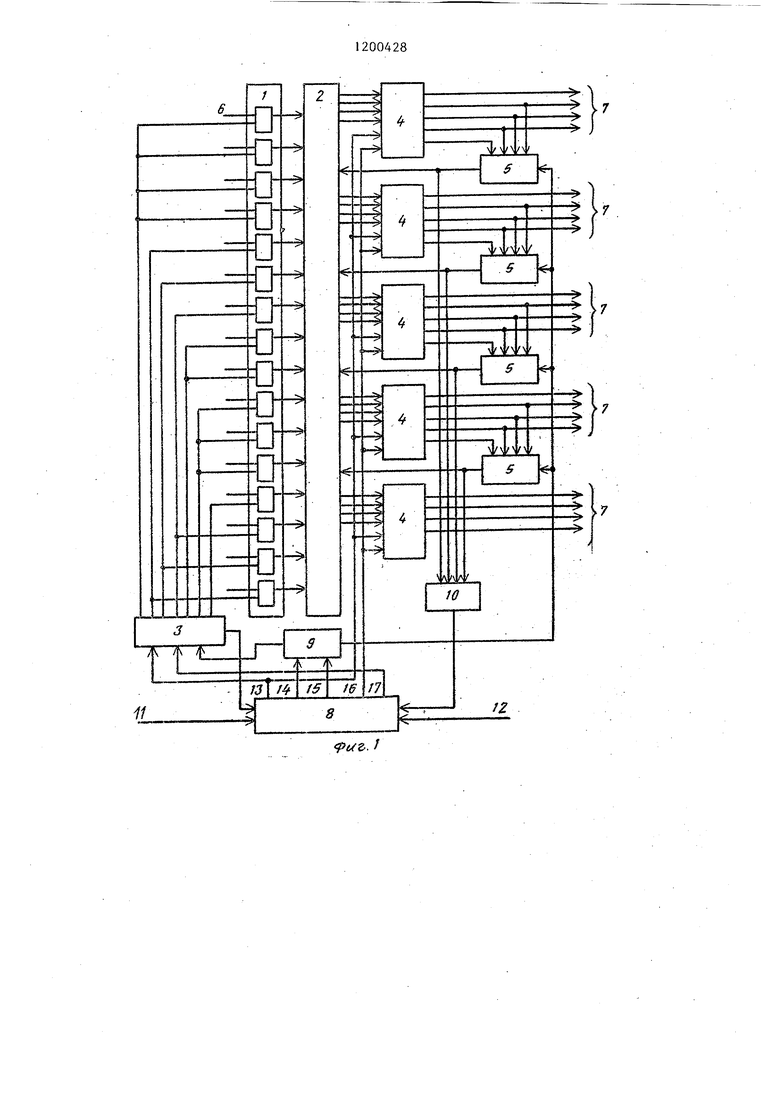

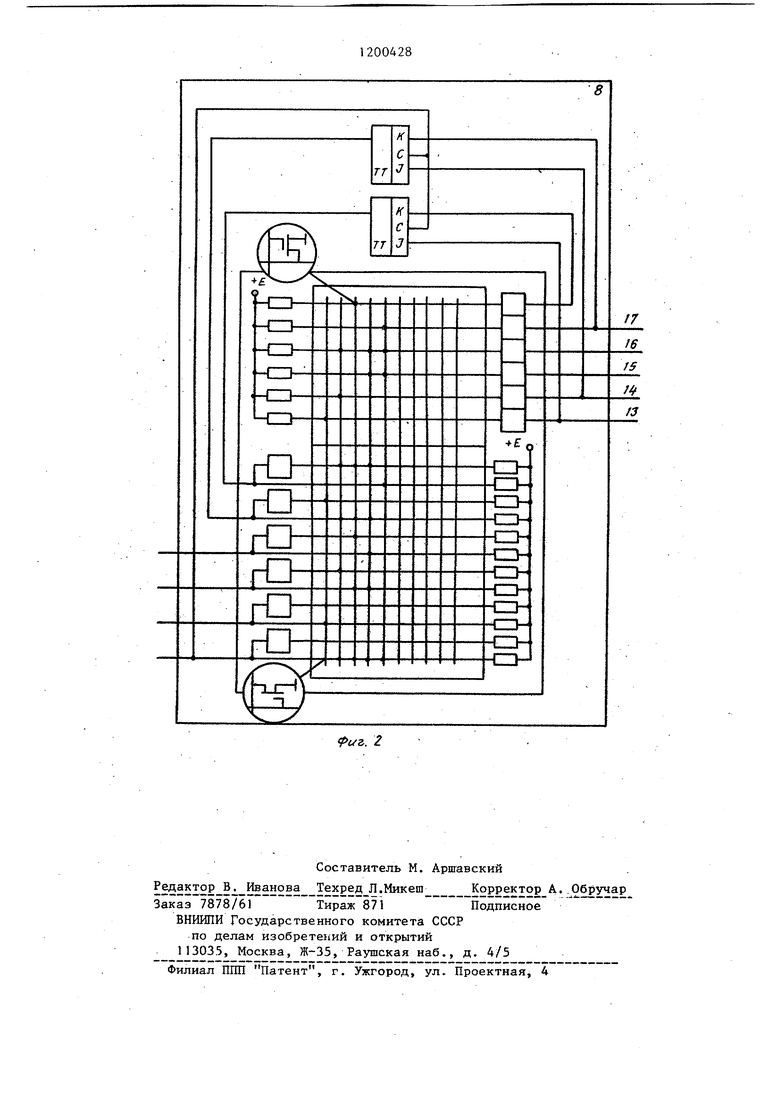

На фиг. 1 представлена структурная схема устройства; на фиг. 2 функциональная схема блока управления .

Преобразователь содержит элементы И-НЕ 1, шифратор 2, распределитель 3 импульсов, накапливающий сумматор 4, блоки 5 коррекции, информационные входы 6 преобразователя, выходы 7 преобразователя, блок 8 управления, 85 -триггер 9,

,2 2Г2М,2 2-Ч,2/, ,Г2 2 ,, , 2, 12 2 , ,1:2 .

Шифратор 2 предназначен для формирования двоично-десятичных эквивалентов опрашиваемых разрядов двоичного кода числа и кодов коррекции

-содержимого ячеек накапливающего сумматора 4.

Распределитель 3 импульсов предназначен для формирования импульсов опроса групп разрядов двоичного кода и может быть реализован, например, на сдвиговом регистре, имеющем входы параллельной записи исходного числа, и элементах И.

Накапливающий сумматор предназначен для суммирования двоично-десятичных эквивалентов, формируемых шифратором 2, и запоминания их сумм Он состоит из отдельных ячеек (тетрад) 4, каждая из которых содержит четырехразрядный комбинационный сумэлемент И-НЕ 10, тактовый вход II, управляющий вход 12 преобразователя, выходы 13-17 блока управления.

Элементы И-НЕ 1 предназначены для передачи потенциалов с информационных входов 6 на соответствующие входы первой группы входов шифратора 2 в инверсной форме. Элементы И-НЕ 1 разбиты на группы таким образом, что в одну группу попали элементы, соответствующие тем разрядам двоичного кода числа, двоичнодесятичные эквиваленты которых не имеют единиц в своих одноименных, разрядах.. Для шестнадцатиразрядного двоичного числа такое разбиение может быть осуществлено, например, -.следующим образом

матор и пятиразрядный статический регистр, реализованный на триггерах с внутренней задержкой информации. Блоки 5 коррекции предназначены для коррекции сумм в ячейках накапливающего сумматора 4 и представляют собой комбинационные схемы, каждая из которьлх реализует логическую функцию ,,.

(1ГР.5,УР,),

iffle К - сигнал на выходе (|-го блока

коррекции;

, - выход переноса из 1-го десятичного разряда;

Sjg,, выходы 2, 2, 2 i-ro десятичного разряда;

Q - значение сигнала на прямом выходе триггера 9.

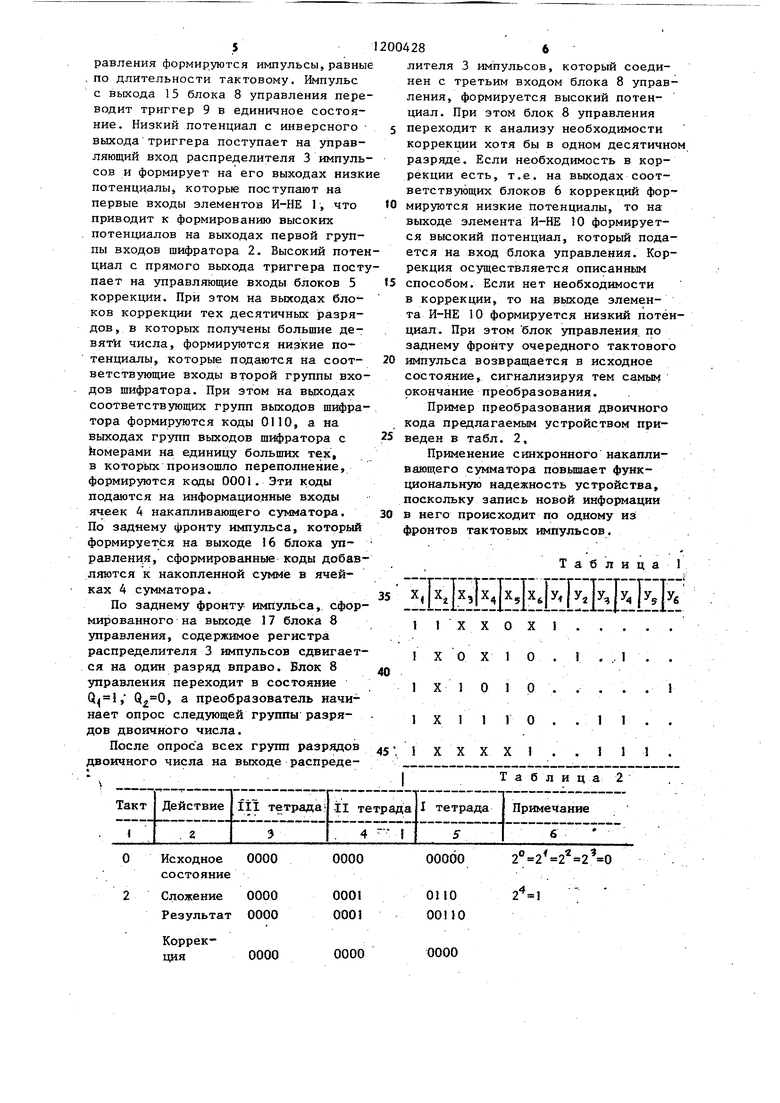

Блок 8 управления фиг. 2) предназначен для организации взаимосвяз между отдельными блоками устройства с целью осуществления требуемого преобразования и содержит шифратор выполненный на программируемой логической матрице (ПЛМ) (6,6,10), и два ЗК-триггера. Программирование ПЛМ осуществляется в соответствии с табл. 1. Применение ПЛМ позволяет сократить количество используемых корпусов, а применение ЗК-триггеров - количество выходов из ПЛМ.

R5-триггер 9 предназначен для

управления подачей сигналов во времени на шифратор 2 либо с информационных входов в устройства, либо с блоков 5 коррекции.

Элемент И-НЕ 10 формирует для блока 8 управления сигнал Необходима коррекция результата в накапливающем сумматоре.

Преобразователь работает следующим образом.

В исходном положении преобразователя блок 8 управления находится в начальном состоянии, т.е. -Qf, 0, где Q, и Qg состояния соответственно первого и второго ЗК-триггеров блока управления. На вход 11 поступают .тактовые импульсы а на входе 12 присутствует низкий потенциал, которьй подается на второй вход блока управления, что обеспечивает подтверждение начального, состояния блока управления. В ячейках 4 накапливающего сумматора хранится результат предьщущего преобразования. Распределитель 3 импульсов и .триггер 9 могут иметь произвольное состояние.

Преобразование осуществляется следующим образом.

На информационные входы 6 устройства подаются соответствующие двоичному коду числа потенциалы, которые подаются на первые входы элементов И-НЕ 1. Затем на вход 12 подается сигнал Пуск. С приходом первого после подачи сигнала Пуск тактового импульса на выходе 13 блока 8 управления формируется импульс Начальная установка преобразователя, равный по длительности тактовому. Этот импульс подается на входы начальной установки распределителя 3 импульсов и ячеек 4

2004284

накапл1шающего сумматора. При этом в регистр, распределителя импульсов записывается число 10000000, а ячейки накапливающего сумматора обнуляются. По окончанию данного тактового импульса блок управления переходит из начального состояния в рабочее состояние (р,).

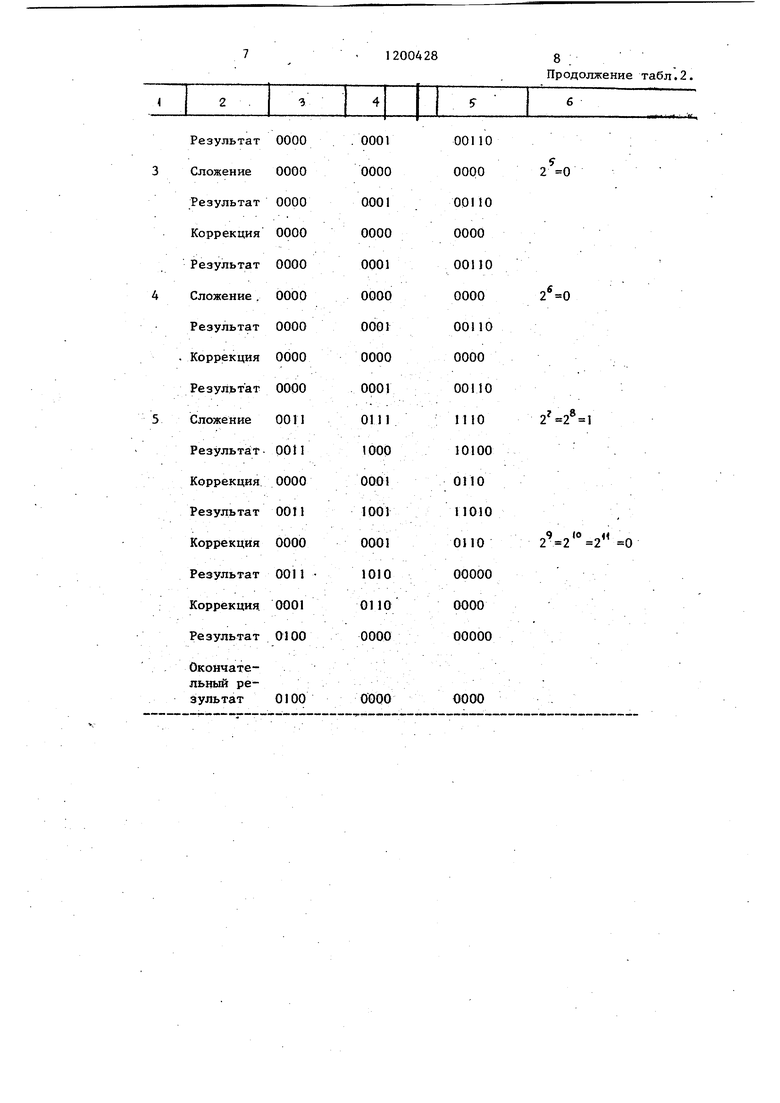

Обработка каждой группы разрядов

0 двоичного.кода числа осуществляется за два такта. В одном такте к накопленной в ячейках 4 сумме двоично-десятичных эквивалентов добавляются новые, а в другом такте кор15 ректируется полученная сумма.

Добавление двоично-десятичных эквивалентов происходит следующим. образом. С приходом тактового импульса на выходах 14 и 16 блока В

20 управления формируются импульсы, равные по длительности тактовому, импульс с выхода 14 блока управления поступает на вход RS-триггера 9 и переводит его в нулевое состояние.

25 Низкий потенциал с прямого выхода триггера поступает на управля ощие входы блоков 5 коррекции и формиру-. ет на их выходах высокие потенциалы, которые подаются на входы второй :группы входов шифратора 2. Высокий потенциал с инверсного выхода триггера поступает на управляющий вход распределителя 3 импульсов, что при. водит к формированию на его выходе, который соответствует номеру опрашиваемой группы разрядов двоичного кода, высокого потенциала. Этот высокий потенциал разрешает прохождение сигналов с входов 6 преобразователя через элементы И-НЕ 1 на входы

первой группы входов шифратора. На выходах шифратора формируется двоичный код, равный сумме двоично-десятичных эквивалентов опрашиваемых . разрядов, который подается на инфор-

мационные входы ячеек 4 накапливающего сумматора. По заднему фронту импульса, который формируется на выходе 16 блока управления, полученный двоичный код добавляется к содержимому накапливающему сумматору. По окончанию данного тактового импульса блок управления переходит в состояние Q,, при котором возникает коррекция полученной суммы.

55 В следующем такте происходит коррекция накопленной суммы в ячейках 4 сумматора. С приходом тактового импульса на выходах 15-17 блока 8 управления формируются импульсы,равны , по длительности тактовому. Импульс с выхода 15 блока 8 управления пере водит триггер 9 в единичное состояние. Низкий потенциал с инверсного выхода триггера поступает на управляющий вход распределителя 3 импуль сов и формирует на его выходах низк потенциалы, которые поступают на первые входы элементов И-НЕ 1, что приводит к формированию высоких потенциалов на выходах первой группы входов шифратора 2. Высокий поте циал с прямого выхода триггера пост пает на управляющие входы блоков 5 коррекции. При этом на выходах блоков коррекции тех десятичных разрядов, в которых получены большие девяти числа, формируются низкие потенциалы, которые подаются на соотвётствующие входы второй группы вхо дов шифратора. При этом на вЕлходах соответствующих групп выходов шифра тора формируются коды ОНО, а на выходах групп выходов шифратора с Номерами на единицу больших тех, в которых произошло переполнение, формируются коды 0001. Эти коды подаются на информационные входы ячеек 4 накапливающего сумматора. По заднему фронту импульса, который формируется на выходе 16 блока управления, сформированные коды добав ляются к накопленной сумме в ячейках 4 сумматора. По заднему фронту импульса, сфор мированного на выходе 17 блока 8 управления, содержимое регистра распределителя 3 импульсов сдвигает ся на один разряд вправо. Блок 8 управления переходит в состояние Q , , а преобразователь начинает опрос следующей группы разрядов двоичного числа. После опроса всех групп разрядов двоичного числа на выходе распреде0000

Исходное0000 состояние

0001

Сложение0000 0001

Результат0000

Коррек0000

0000 ция

лителя 3 импульсов, который соединен с третьим входом блока 8 управления, формируется высокий потенциал. При этом блок 8 управления переходит к анализу необходимости коррекции хотя бы в одном десятичном разряде. Если необходимость в коррекции есть, т.е. на выходах соответствующих блоков 6 коррекций формируются низкие потенциалы, то на выходе элемента И-НЕ 10 формируется высокий потенциал, который подается на вход блока управления. Коррекция осуществляется описанным способом. Если нет необходимости в коррекции, то на выходе элемента И-НЕ 10 формируется низкий потенциал. При этом блок управления по заднему фронту очередного тактового импульса возвращается в исходное состояние, сигнализируя тем самый окончание преобразования. Пример преобразования двоичного кода предлагаемым устройством приведен в табл. 2, Применение синхронного накапливающего сумматора повышает функциональную надежность устройства, поскольку запись новой информации в него происходит по одному из фронтов тактовых импульсов. Т а б л и ц а 1 х, x,|x,f X Jy, У215. 1 I X X о X 1 i X о X 1 о . 1 . .. 1 . . 1 XI о 1 о . . . . . 1 1X1 1 10. .1 1 . 1 X X X X 1 . . 1 11 Iт а б л и ц а 2

Результат

Сложение

Результат

Коррекция

Результат

Сложение .

Результат

Коррекция

Резул&тат

Сложение

Результат Коррекция

Результат

Коррекция

Результат

Коррекция.

Результат

Окончательный результат

00110

2 0

0000

00110

0000

00110

0000

00110

0000

00110

11 10

10100

оно

11010

оно

00000

0000

00000

0000

иг. /

. Z

| Преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU637808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1984-04-26—Подача