Изобретение относится к радиотехнике и может быть использовано в приемопередающей и измерительной аппаратуре.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности внешнего управления сдвигом фазы.

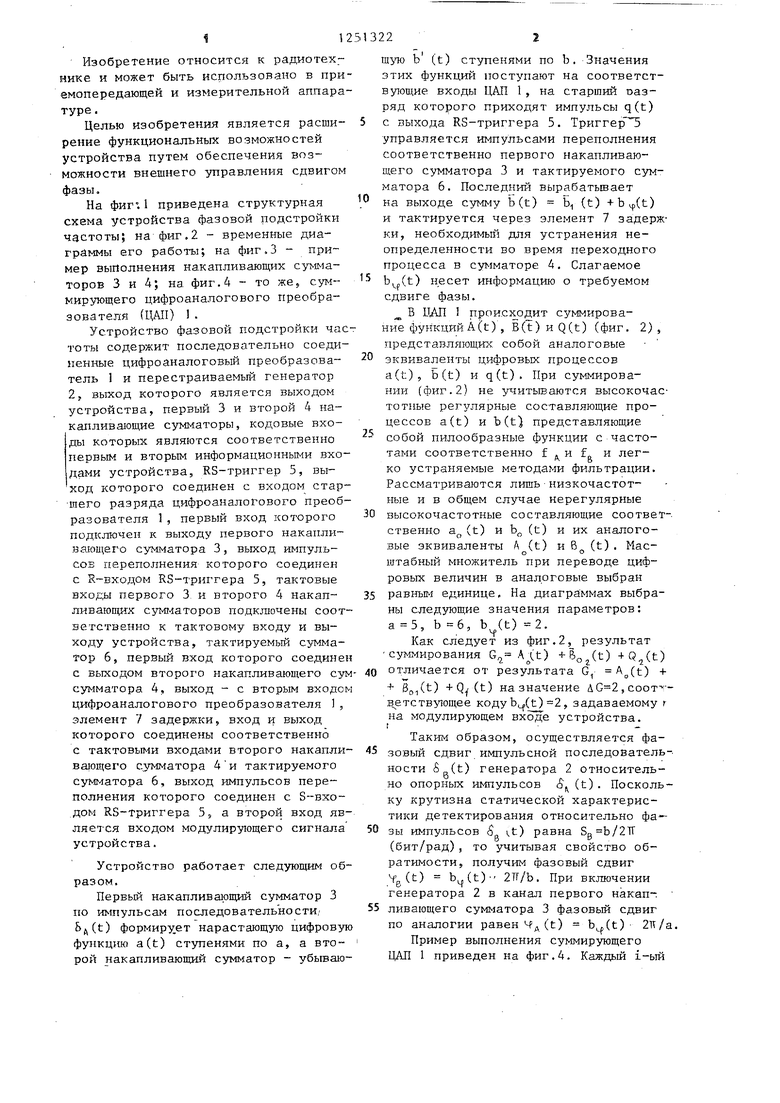

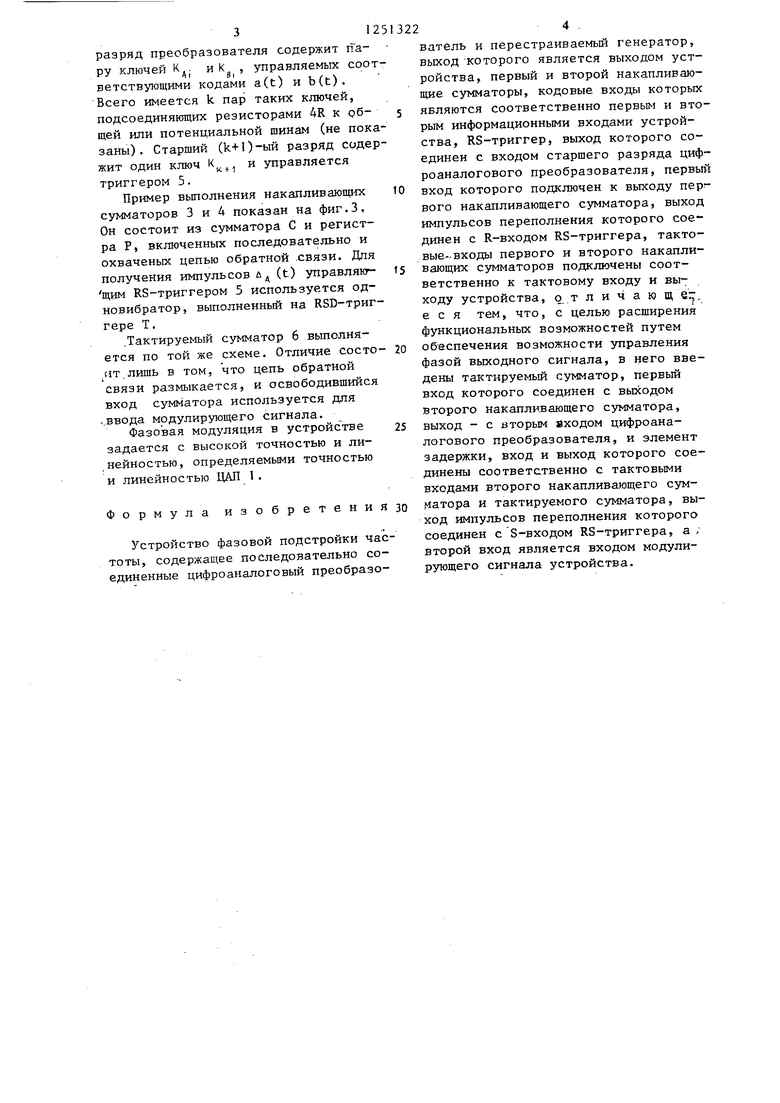

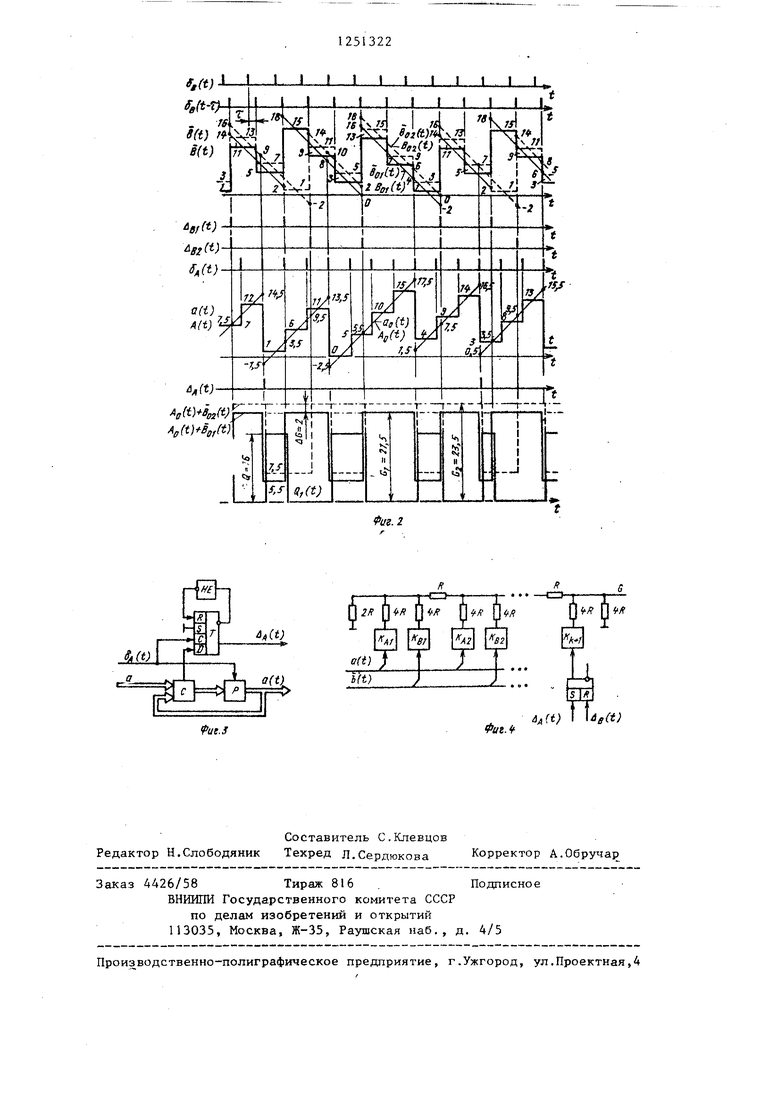

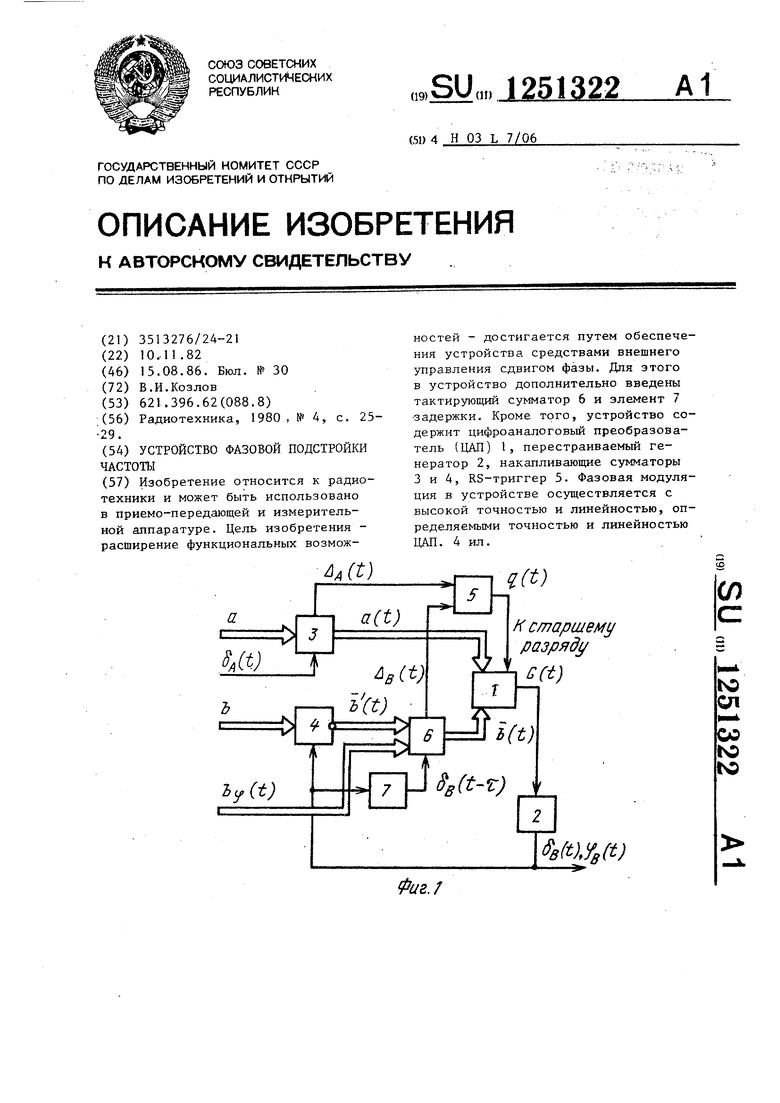

На фиг-. 1 приведена структурная схема устройства фазовой подстройки частоты; на фиг.2 - временные диаграммы его работы; на фиг.З - пример выполнения накапливающих сумматоров 3 и 4; на фиг.4 - то же, суммирующего цифроаналогового преобразователя (L1AII) .

Устройство фазовой подстройки частоты содержит последовательно соединенные цифроаналоговьй преобразователь 1 и перестраиваемый генератор 2. выход которого является выходом устройства, первый 3 и второй 4 на- каплива1ощие сумматоры, кодовые входы которых являются соответственно первым и вторым информационными входами устройства, RS-триггер 5, выход которого соединен с входом старшего разряда цифроаналогового преобразователя 1, первый вход которого подключен к выходу первого накапли- валощего сумматора 3, выход импульсов переполнения которого соединен с R-входом RS-триггера 5, тактовые входы первого 3. и второго 4 накапливающих су1«1маторов подключены соответственно к тактовому входу и выходу устройства, тактируемый сумматор 6, первый вход которого соединен с выходом второго накапливающего сум сумматора 4, выход - с вторым входом цифроаналогового преобразователя 1, элемент 7 задержки, вход и выход которого соединены соответственно с тактовыми входами второго накапли- ва1ощего с.,умматора 4 и тактируемого сумг-iaTopa 6, выход импульсов переполнения которого соединен с S-вхо- .дом RS-триггера 5, а второй вход является входом модулирующего сигнала устройства.

Устройство работает следующим образом,

Первый накапливающий сумматор 3 по импульсам последовательности/ b(t) формирует нарастающую цифровую функции a(t) стзшенями по а, а второй накапливающий сумматор - убываю

5

0

5

0

5

тую Ъ (t) ступенями по Ь, Значения этих функций поступают на соответствующие входы ЦАП 1, на старший оаз- ряд которого приходят импульсы q(t) с выхода RS-триггера 5. Триггер 5 управляется импульсами переполнения соответственно первого накапливающего сумматора 3 и тактируемого сумматора 6. Последний вырабатьшает на выходе сумму b(t) Б (t) +bif(t) и тактируется через элемент 7 задержки, необходимый для устранения неопределенности во время переходного процесса в сумматоре 4. Слагаемое Ь (t) несет информацию о требуемом сдвиге фазы.

Б ЦАП I происходит суммирование функций А (t), В(1)ид(ь) (фиг. 2), представляющих собой аналоговые эквиваленты цифровых процессов a(t), Б (t) и q(t). При суммировании (фиг.2) не учитьгоаются высокочастотные регулярные составляющие процессов a(t) и b(t) представляющие собой пилообразные функции с частотами соответственно f . и f и лег о

ко устраняемые методами фильтрации. Рассматриваются лишь низкочастотные и в общем случае нерегулярные высокочастотные составляющие соответственно а (t) и Ь„ (t) и их аналоговые эквиваленты А (t) и В (t). Масоо

штабный множитель при переводе цифровых величин в аналоговые выбран равньп-j единице, На диагра:ммах выбраны следующие значения параметров: а 5, b 6, b(t) -2.

Как следует из фиг.2, результат суммирования 0,, A(t) +Bo,,(t) +Q(t) 40 отличается от результата G, A(t) + -ь ) +Qy(t) назначение ,соот- - в етствутощее коду ) 2, задаваемому г на модулирующем вхс1де устройства.

Таким образом, осуществляется фазовый сдвиг импульсной последовательности Sg(t) генератора 2 относительно опорных импульсов Sf (t) . Поскольку крутизна статической характеристики детектирования относительно фа-

59 зы импульсов S, i.t) равна Sg b/2Tr (бит/рад), то учитывая свойство обратимости, получим фазовый сдвиг Vg (t) b(t)- 2TT/b. При включении генератора 2 в канал первого накап-

55 ливающего сумматора 3 фазовый сдвиг по аналогии равен Чд (t) b,(t) 2тт/а.

Пример выполнения суммирующего иДП 1 приведен на фиг.4. Каждый i-ый

45

разряд преобразователя содержит пару ключей К. и К , управляемых соответствующими кодами a(t) и b(t). Всего имеется k пар таких ключей, подсоединяющих резисторами 4R к об- щей или потенциальной щинам (не показаны) . Старший (k+l)-bm разряд содержит один ключ К и управляется триггером 5.

Пример выполнения накапливающих сумматоров 3 и 4 показан на фиг.З, Он состоит из сумматора С и регистра Р включенных последовательно и охваченьк цепью обратной .связи. Для получения импульсов Лд (t) управлякг- щим RS-триггером 5 используется од- новибратор, выполненный на RSD-триг- гере Т,

.Тактируемый сумматор 6 выполняется по той же схеме. Отличие состо- ит лишь в том, что цепь обратной связи размыкается, и освободивщийся вход сумматора используется для ..ввода модулирующего сигнала.

Фазовая модуляция в устройстве задается с высокой точностью и линейностью, определяемыми точностью и линейностью ЦАП 1.

Формула изобретения

Устройство фазовой подстройки частоты, содержащее последовательно соединенные цифроаналоговый преобразователь и перестраиваемый генератор, выход -которого является выходом устройства, первый и второй накапливающие суг маторы, кодовые входы которых являются соответственно первым и вторым информационными входами устройства, RS-триггер, выход которого соединен с входом старшего разряда циф роаналогового преобразователя, первьп вход которого подключен к выходу пер вого накапливающего сумматора, выход импульсов переполнения которого соединен с R-входом RS-триггера, тактовые- входы первого и второго накапливающих сумматоров подключены соответственно к тактовому входу и выходу устройства, о..т л и ч а ю щ е:, е с я тем, что, с целью расщирения функциональных возможностей путем обеспечения возможности управления фазой выходного сигнала, в него введены тактируемый сумматор, первый вход которого соединен с выходом Второго накапливающего сумматора, выход - с вторым йходом цифроана- логового преобразователя, и элемент задержки, вход и выход которого соединены соответственно с тактовыми входами второго накапливающего сум- Катора и тактируемого сзгмматора, выход импульсов переполнения которого соединен с S-входом RS-триггера а ; второй вход является входом модулирующего сигнала устройства.

ff(t) J-IL J1J1 .1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| МНОГОЧАСТОТНЫЙ ФАЗОЦИФРОВОЙ ДЕТЕКТОР | 1988 |

|

RU2040851C1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Синтезатор частот | 1985 |

|

SU1262685A1 |

| Синтезатор частот | 1985 |

|

SU1254576A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Синтезатор частот | 1987 |

|

SU1431034A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

Изобретение относится к радиотехники и может быть использовано в приемо-передающей и измерительной аппаратуре. Цель изобретения - расширение функциональных возможа ш Ъ(t) ностей - достигается путем обеспечения устройства средствами внешнего управления сдвигом фазы. Для этого в устройство дополнительно введены тактирующий сумматор 6 и элемент 7 задержки. Кроме того, устройство содержит цифроаналоговый преобразователь (ЦАП) 1, перестраиваемый генератор 2, накашливающие сумматоры 3 и 4, RS-триггер 5. Фазовая модуляция в устройстве осуществляется с высокой точностью и линейностью, определяемыми точностью и линейностью ЦАП. 4 ил. (t) старшему разряду (Л c(t} s(t-T) B() Фиг. 7

fuf.s

§ 5К5гЗгЗ дГ

f/t

Фиг.

п;

uf,{i) jiff(t}

Составитель С.Клевцов Редактор Н.Слободяник Техред Л.Сердюкова Корректор А.Обручар

Заказ 4426/58Тираж 816 .Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Радиотехника, 1980 29. |

Авторы

Даты

1986-08-15—Публикация

1982-11-10—Подача