(54) ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1990 |

|

SU1755360A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Устройство фазовой подстройки частоты | 1982 |

|

SU1251322A1 |

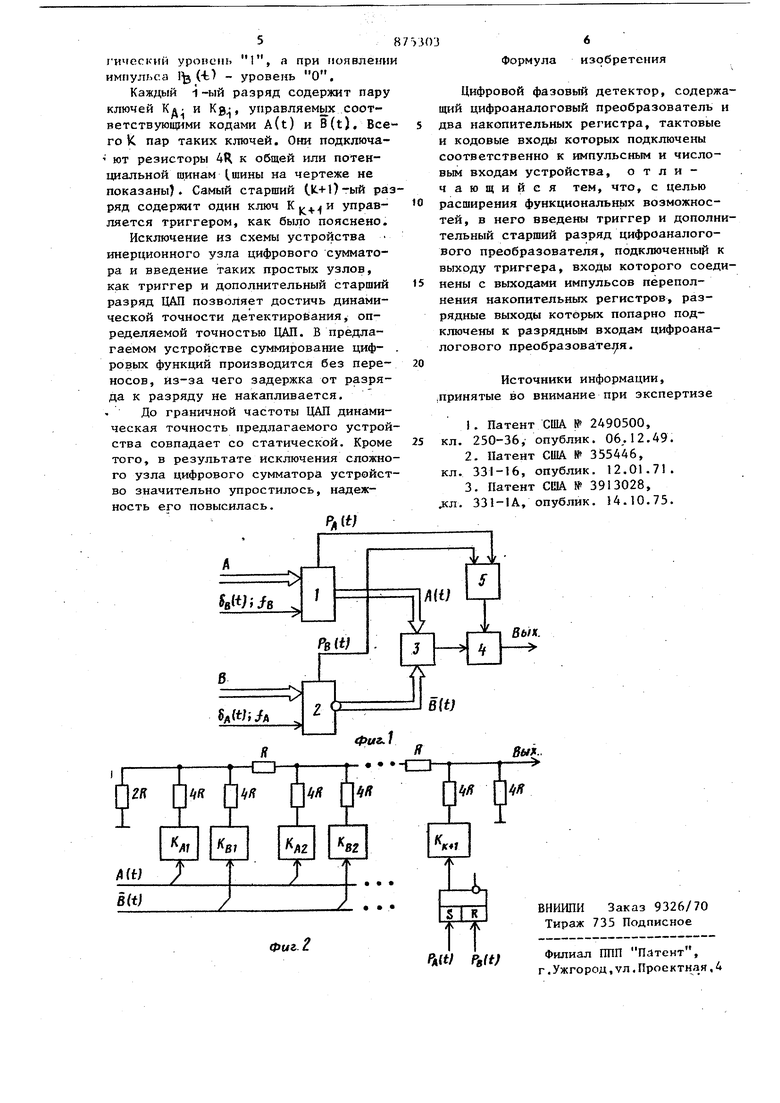

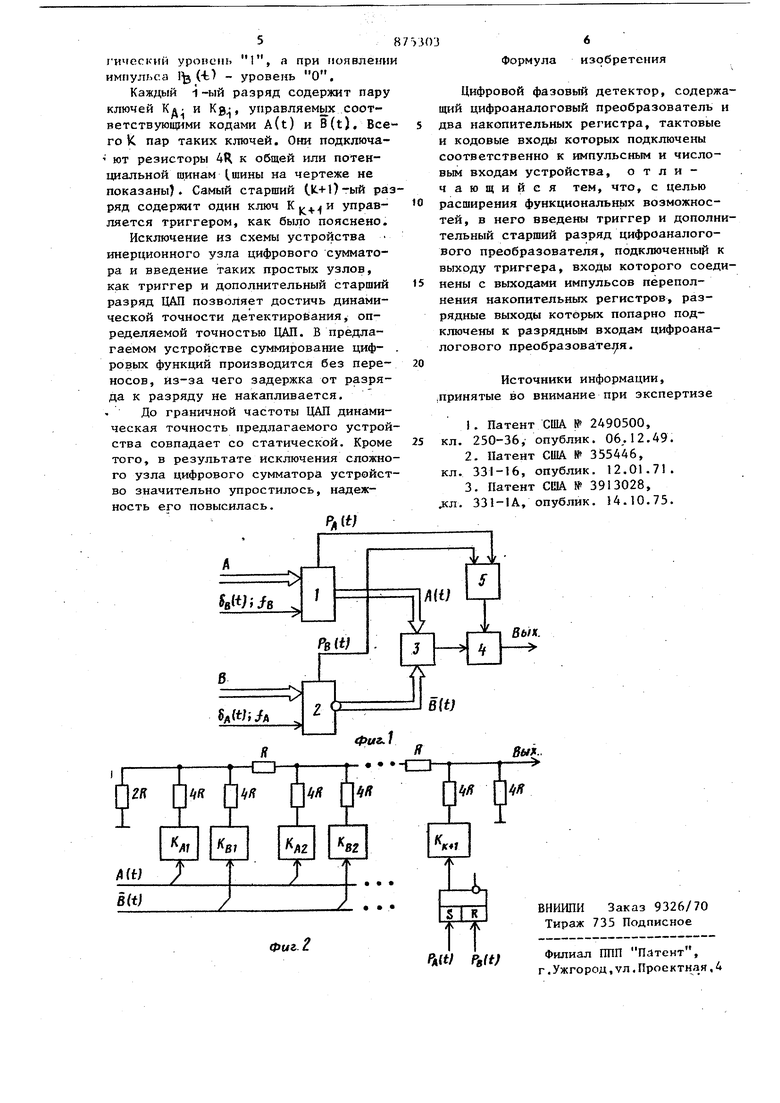

I . Изобретение относится к радиотехнике и может быть использовано для детектирования радиосигналов с угловой модуляцией, для получения сигналов рассогласования в системах автоматической подстройки частоты (АПЧ). а также для формирования сетки стабильных частот в приемопередающей и измерительвой аппаратуре. Известно устройство цифрового фjaзового детектирования на неравных частотах, основанное на приведении частот к равенству путем их деления целое число раз цифровыми метоД31МИ4 Устройство предназначается для целей частотного синтеза и именно здесь нашло в свое время широкое применение 1 . Однако из-за инерционности, вноси мой делителями частоты в Случае, kor да частоты некратны и имеют малый общий множитель, устройства такого типа не удовлетворяют возросшим требованиям к динамической точности цетектирования и применение их в настоящее время весьма ограничено. Известно также устройство цифрофазового синтеза, которое в значительной степени устраняет этот недостаток. Устройство основано на применении делителя частоты с дробным переменным козффициентом деления и цепи компенсации помех Дробности, в которой аналоговый сигнал фазового детектора суммируется с функцией накопления дробной части коэффициента деления, также преобразованной в аналоговую форму J. Однако точность детектирования в этом случае определяется остаточным (нескомпенсированным) уровнем помех дробности, который зависит от точности аналогового суммирования и стабильности во времени и в температуре статических характеристик фазового детектора, цифроаналогового преобразователя (ЦАП) и суммирующего устройства. Из-за этого не удается достичь устойчивой компенсации помех дробности до уровня ниже 40 дБ, что чаще всего оказывается нед остатрчным. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее два накопител ных регистра, цифровой сумматор и ПАП. Под действием тактовых импульсов (f(t) с частотой f содержимое A{t) первого регистра возрастает с каждым тактом на величину А, заставаемую этим числом на кодовом входе регистра. Аналогичным образом действует второй накопительный регистр, формируя функцию B(t), возрастающую на величину В всякий раз при поступЛенин на его тактовый вход импульсов последовательности сГд (t) с часто- . той f . На цифровом сумматоре,суммируются переменные коды A(t) и B(t) снимаемые соответственно с инверсных выходов первого и второго регист ра, чем обеспечивается вычитание фун ций A(t)H B(t) на выходе сумматора. С помощью ЦАП разность кодов C(t) преобразовывается в аналоговую велич ну и поступает на выход устройства. При условии, что f. А значение постоянной составляющей на выходе не зависит от времени и определяется эквивалентной разностью фаз импульсных последовательностей (f(t) и (Гв()« Статическая (при f. , ) погрешность детектирования определяется лишь точностью ЦАП, так как погрешность, подаваемая цифровым сумматором в этом случае, рав. на нулю. Высокая статическая точност детектирования (десятиразрядный ЦАП, например, имеет погрешность 1О) яв ляется важным достоинством этого уст ройства по сравнению с известньми LS Однако возможности устройства по быстродействию ограничены задержками операций поразрядного суммирования и переносов результатов суммирования из разряда в разряд в цифровом сумматоре. Задержки оказьшаются значительными, так как на практике А и В многоразрядные двоичные числа (до 12 и более разрядов). Из-за задержек результирующий процесс c(t) на выходе сумматора воспроизводится с погрешностью, заключающейся как в поразрядных искажениях логических уровней О и 1, так и в более крупных ошибках, выражающихся в вьтадании ступеней величиной А и 4 В из результата суммирования. Динамическая точность детектирования оказывается удовлетворительной (приближающейся к статической) при входных частотах по крайней мере на порядок меньших предельной рабочей частоты цифрового сумматора, из-за чего использование этого устройства на практике весьма неэффективно. Цель изобретения - расширение функциональных возможностей. Указанная цель достигается тем,, что в устройство, содержащее цифроаналоговый преобразователь и два накопительных регистра, тактовые и кодовые входы которых подключены соответственно к импульсным и числовым входам устройства, введены триггер и дополнительный старший разряд цифроаналогового преобразователя, подключенный к выходу триггера, входы которого соединены с выходами импульсов переполнения накопительных регистров, разрядные выходы которых попарно подключены к разрядным входам цифроаналогового преобразователя. На фиг. 1 показана схема предла гаемого устройства; на фиг. 2 - пример выполнения суммирующего ЦАП. Устройство содержит накопительные регистры 1 и 2, цифроаналоговый преобразователь (ЦАП) 3, дополнительный старший разряд ЦАП 4, триггер 5. Схема работает следующим образом. Переменные коды A(t) и B(t) с выходов накопительных регистров 1 и 2 поступают на входы цифроаналогового преобразователя 3, в котором осуществляется поразрядное (без переносов) суммирование и преобразование кодов, Для устранения скачкообразных приращений выходного аналогового процесса в моменты переполнений регистров, в ЦАП введен дополнительньй старший разряд, подключенный к выходу триггера 5, Триггер управляется импульсами переполнения P(t)HP(t) соответствующих регистров 1 и 2, В момент переполнения накопительного регистра I код A(t) уменьшается на величину Q равную емкости регистров, а при переполнении регистра 2 код 5(-Ь) увеличивается на ту же самую величину. Так как вес введенного старшего разряда ЦАП соответствует величине Q, для устранения упомянутых скачков достаточно лишь выбрать полярность включения триггера такой, чтобы при появлего1и импульса Рд(Ь) он передавал на ЦАП ло1ическин уронсмь , а при ноявлетш импульса % (-t) - уровень О.

Каждый i-ый разряд содержит пару ключей Кд- и Kg-, управляемых соответствующими кодами A{t) и В (t). Всего К пар таких ключей. Они подключают резисторы 4Я к общей или потенодальной шинам шины на чертеже не показаны). Самый старший (.К.+ 1)-ый разряд содержит один ключ управляется триггером, как было пояснено.

Исключение из схемы устройства инерционного узла цифрового сумматора и введение таких простых узлов, как триггер и дополнительный старший разряд ЦДЛ позволяет достичь динамической точности детектирования, определяемой точностью ЦАП. В предлагаемом устройстве суммирование цифpoBibix функций производится без переносов, из-за чего задержка от разряда к разряду не накапливается.

До граничной частоты ЦАП динамическая точность предлагаемого устройства совпадает со статической. Кроме того, в результате исключения сложного узла цифрового сумматора устройство значительно упростилось, надежность его повысилась.

P(t)

Формула изобретения

Цифровой фазовый детектор, содержащий цифроаналоговый преобразователь и два накопительных регистра, тактовые и кодовые входы которых подключены соответственно к импульсным и числовым входам устройства, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены триггер и дополнительный старший разряд цифроаналогового преобразователя, подключенный к выходу триггера, входы которого соединены с выходами импульсов переполнения накопительных регистров, разрядные выходы которых попарно подключены к разрядным входам цифроаналогового преобразователя.

Источники информации, .принятые во внимание при экспертизе

кл. 250-36, опублик. 06,. 12.49.

кл. 331-16, опублик. 12.01.71.

Авторы

Даты

1981-10-23—Публикация

1980-02-12—Подача