Изобретение относится к радиотехнике, а именно к технике цифрового фазового детектирования на неравных частотах и может быть использовано для детектирования радиосигналов с угловой модуляцией, для получения сигналов рассогласования в системах АПЧ, для формирования сетки стабильных частот в приемопередающей и измерительной аппаратуре и в ряде других случаев.

Известен цифровой фазовый детектор, в котором фа,эы исходных импульных последовательностей преобразовываются с помощью накопительных регистров в цифровые ступенчатые функции времени, суммируемые в цифровом сумматоре, и результат суммирования подвергается цифроаналоговому преобразованию С1.1 .

Статическая погрешность детектирования определяется лишь точностью цифроаналогового преобразователя ,СЦАП) , так как погрешность, даваемая сумматоре, равна нулю. Однако возможности устройства по быстродействию ограничены;задержками операций поразрядного суммирования и переносов результатов суммирования из разряда в разряд в цифровом сумматоре. Поскольку времена, требующиеся для суммирования различных чисел, существенно различгиотся, задержки изменяются в динамике в значительных пределах, и исключить их влияние путем тактирования операций суммирования не представляется возможным, так как тактовые частоты суммируемых числовых процессов в общем случае неравны и некратны. Динамическая точность устройства оказывается удовлетворитель ной (приближающейся к статической) при входных частотах по крайней мере на порядок меньших предельной рабочей частоты цифрового сумматора, из-за чего использование устройства на практике неэффективно.

Наиболее близким к изобретению по технической сущности и достигаемому результату является цифровой фазовый детектор, содержащий первый и второй накопительные регистры, суммирующий цифроаналоговый преоб,разователь и us-триггер. Каждый из накопительных регистров состоит из цифрового сумматора, запоминающего регистра и триггера памяти. Цифровы входы устройства соединень с цифровыми входами первого, числа сумматоров накопительных регистров, а тактовые входы - с тактовыми входами запоминающих, регистров. Цифровые входы второго числа cyi aTOpoa соединены с выходами запоминающих регистров, входы-которых соединены с выходами сумматоров.

Разрядные входы суммирующего цифроаналогового преобразователя, кроме старшего разряда, попарно соединены с разрядными выходами запоминающих регистров , а выход - с 5 выходной клеммой устройства. Информационные входы триггеров памяти соединены с выходами переполнения соответствующих цифровых сумматоров, а тактовые входы - с тактовы0 ми входами запоминающих регистров, выходы этих триггеров соединены с входами й-триггера, выход которого соединен со старшим разрядом суммирующего цифроаналогового преобразо5 вателя t2l .

Известное устройство работает .следующим образом.

Иод действием тактовых импульсов последовательности ((t) с частотой tj. Q содержимое oft первого регистра возрастает с каждым тактом на величину 01. , задаваемую этим числом на кодовом входе регистра. Аналогичным образом действует второй,накопительс ный регистр, формируя функцию 6, возрастающую на величину 6 всякий раз при поступлении на его тактовый вход импульсов последовательности Se(t) с частотой ij, . С одного из накопительных регистров снимается инверсный код, например .

Переменные кодыо.(А: и Sfe) поступают на входы суммирую1чего ЦйП, в котором осуществляется- поразрядное без переносов) суммирование и преоб5 разованне кодов. Старший разряд ЦАП подключен к выходу R$-триггера, ко- торый управляется импульсами переполнения tt и P(,(t) соответствующих регистров.

0 В момент переполнения первого , накопительного регистра число cx(t) скачком уменьшается на величину О;, равную емкости регистров, а при переполнении .второго регистра Число 5 (t) увеличивается на ту же самую величину. Так как вес старшего разряда ЦАП с.оответствует величине С , для каипенсации этих скачков,т.е. для обеспечения режима детектироваQ ния,необходимо выбирать полярность включения Й5-триггера такой,чтобы при появлении импульса Р((Л он передавал на ЦАП уровень логической 1, а при появлении импульса ) - уроне нь О.

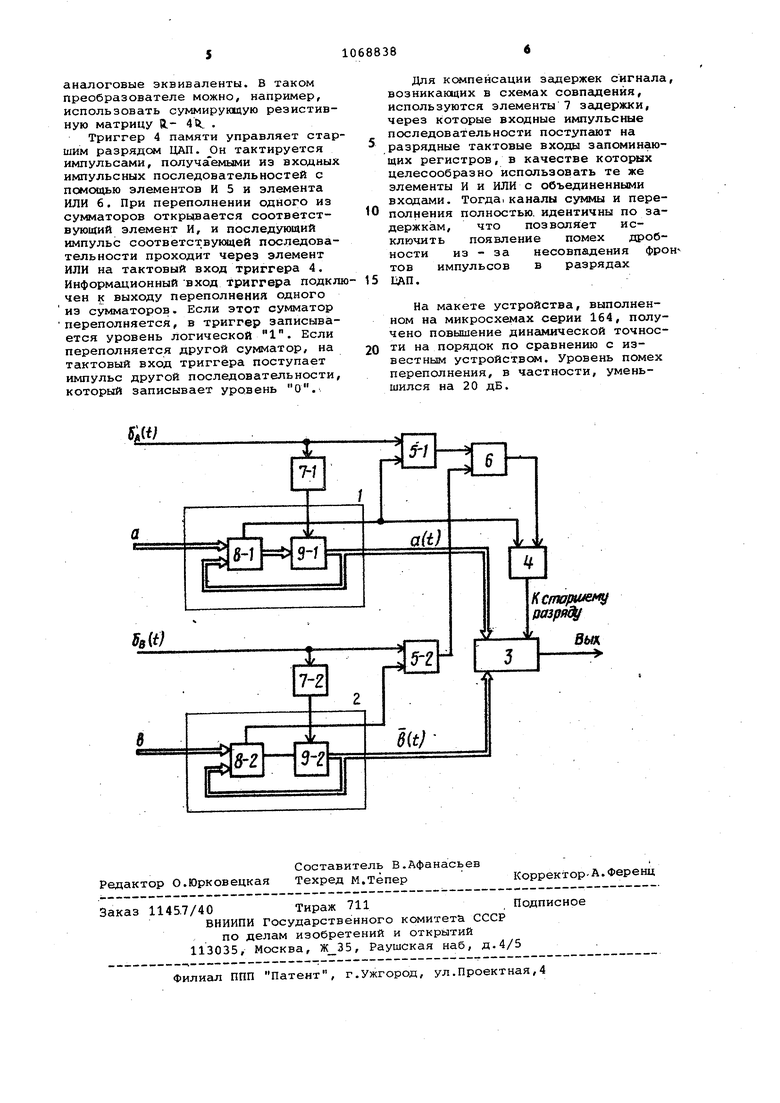

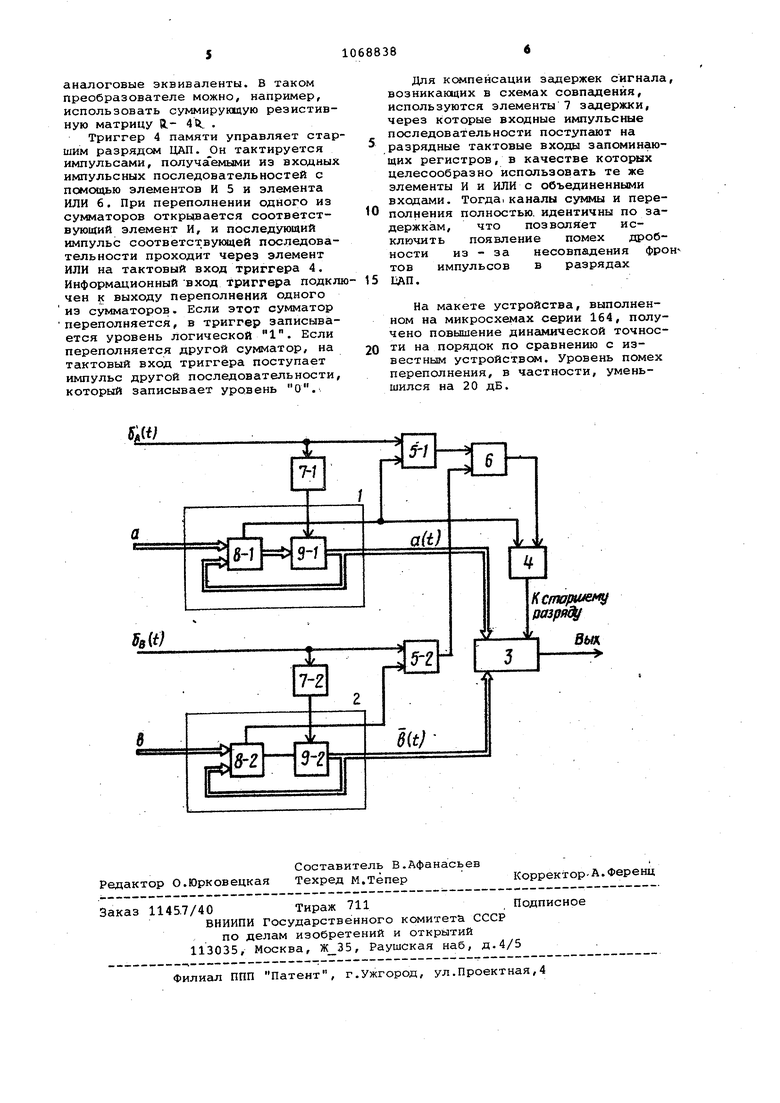

5 в известном устройстве запомина.ощии регистр совместно с суммато-jDOM должен обладать тем свойством, что новое значение су1ммы на его входе должно появляться лишь после 0 окончания приема в него для записи предыдущего значения. Выполнение этого очевидного условия необходимо для предотвращения сбоев устройства. Обычно необходимый режим работы 5 устройства обеспечивается естественными задержками.сигнала в элемен тах схеьлы. Следствием отмеченных обстоятельств является задержка, сигнала на выходе запоминающего регистра на один такт относительно сигнала на выходе сумматора. Поэтому для .фазирования сигнала перепол-нения с выходным сигналом регистра первый получают с помощью триггера памяти, который может рассматривать ся как продолжение запоминающего регистра. На информационный вход CD вхад) триггера поступает импульс переполнения сугф атора, а на тактовый () - импульсы последовательности iJ dk-li или 5(4) . , Поскольку суммирование цифровых функций аЬ) и 6LJ производится без пе .реносов, и задержка от разряда к разряду не накапливается, динамическая точность детектирования приближается к динамической точности суммирующего ЦАП, Однако псэлностью эта точность не реализуется из-за запаздывания сигнала на входе старшего разряда ЦАП относительно осг тальных разрядов. Эта задержка опре деляется временем переключения ВД-триггера. Небольшая по величине она, тем не менее, существенно влияет на динамическую точность детектирования, поскЪльку снижает точность компенсации помех дробности тем больше, чем выше частота псмехи Наибольшее влияние задержки оказыва ется на частоте сигналов переполнения, где потеря в ослаблении этих помех относительно динамической точ ности ЦАП может составить 20 Б и более. Целью изобретения является повышение динамической точности цифрово го фазового детектирования. Поставленная цель достигается тем, что в устройство, содержащее суммирующий цифроаналоговый преобра зователь, первый и второй накопительные регистры, каждый из которы содер.жит запоминающий регистр- и циф ровой сумматор, причем цифровой вх первого числа каждого сумматора со динен с цифровым входом устройства а цифровой вход второго числа кажд го сумматора - с выходами соответс вующего Запоминающего регистра, вы ход каждого .сумматора соединен с входом запоминающего регистра,млад шие разрядные входы суммирующего цифроаналогового, преобразователя попарно соединены с разрядными выходами запоминающих регистров, вве дены два элемента И, элемент ИЛИ, два элемента задержки и D-триггер, причем тактовые входы устройства соединены с первыми входами элемен тов И и входами элементов задержки а выходы последних соединены с так товыми входами запоминающих регист ров, выходы элементов и соединены . с входами элемента ИЛИ, выход которого соединен с тактовым входом -триггера, информационный вход последнего соединен с выходом переполнения цифрового сумматора первого накопительного регистра, выход Т) -триггера соединен с входом старшего, разряда суммирующего цифроаналогового преобразователя, вторые входы элементов И соединены с выходами переполнения цифровых сумматоров накопительных регистров. На чертеже показана схема предлагаемого устройства. Устройство содержит накопительные регистры 1 и 2, цифроаналоговый преобразователь 3,Ь-триггер 4, элемент и 5-1 и 5-2, элемент ИЛИ 6, элементы 7-1 и 7-2 задержки, цифровые сумматоры 8-1 и 8-2, запоминающие регистры 9-1 и 9-2. Входы первого числа цифровых сумматоров 8 соединены с цифровыми входами устройства, а цифровые входы второго числа соединены с выходами запоминак|Щих регистров 9, выходы сумматоров 8 соединены с информационными входами запоминакицих регистров , прямой выход запоминающего регистра 9-1 первого канала и инверсный выход запоминающего регистра 9-2 второго канала соединены с одноименными разрядными входами ЦАП 3. Тактовые входы устройства соединены с входами элементов 7 задержки и первыми входами элементов И 5, вторые входы последних соединены с выходами переполнения цифровых сумматоров 8, выходы элементов И 5 соединены с входом элемента ИЛИ 6, выход которого соединен с тактовым входом В-триггера. Информационный вход D-триггера соединен с выходом переполнений цифрового сумматора 8-1, а выход D-триггера соединен со старшим разрядом цифроаналогового преобразователя 3. Накопительные регистры 1 и 2 формируют переменные коды аи) и Ct) , представляющие собой ступенчатые функции, - соответственно возрастающую и убывающую под действием импульсных последовательностей ) и W импульсных входах устройства. Дискретные приращения а. и в этих функций равны соответственно числам, поступающим в накопитель- ные регистры с числовых входов устройства. Режим фазового детектирования ооеспечивается выполнением условия cx-ffc где {«ь и 1в - частоты следования импульсов 5дС) и 5б (tV Коды aCf и e(t) поступают на входы ЦАП 3, в котором осуществляется поразрядное Сбез переносов.суммирование и преобразование кодов р

аналоговые эквиваленты. В таком Преобразователе можно, например, использовать суммирующую резистивную матрицу а.- 411. .

Триггер 4 памяти управляет старшим разрядом ЦАП. Он тактируется импульсами, получа емыми из входных импульсных последовательностей с помсхцью элементов И 5 и элемента ИЛИ 6. При переполнении одного из сумматоров открьдаается соответствующий элемент И, и последующий импульс соответствукнцей последовательности проходит через элемент ИЛИ на тактовый вход триггера 4. Информёщионный ВХОД триггера подклчен к выходу переполнения одного иэ сумматоров. Если этот сумматор переполняется, в триггер записывается уровень логической 1. Если переполняется другой сумматор, на тактовый вход триггера поступает импульс другой последовательности, который записывает уровень О.

Для компенсации задержек сигнала возникающих в схемах совпгшевйя, используются элементы7 задержки, через которые входные импульсные последовательности поступают на разрядные тактовые входы запоминающих регистров, в качестве которых целесообразно использовать те же элементы И и ИЛИ с объединенными входами. Тогда, каналы суммы и переполнения полностью, идентичны по задержкам, что позволяет исключить появление помех дробности из - за несовпадения фро тов импульсов в разрядах ЬАП.

На макете устройства, выполненном на микросхемах серии 164, получено повышение дингалической точности на порядок по сравнению с известньлм устройством. Уровень помех переполнения, в частности, уменьшился на 20 дБ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Синтезатор частот | 1982 |

|

SU1067603A1 |

| Устройство фазовой подстройки частоты | 1982 |

|

SU1251322A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1990 |

|

SU1755360A1 |

| УСТРОЙСТВО ДЛЯ ГЕНЕРИРОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ С ИСПОЛЬЗОВАНИЕМ ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ, ПРЕЖДЕ ВСЕГО ДЛЯ ПРЯМОГО ЦИФРОВОГО СИНТЕЗА | 1998 |

|

RU2212757C2 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1987 |

|

SU1741260A1 |

ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР, содержащий cy Ф4Иpyюn ий цифроаналоговый преобразователь, первый и второй накопительные регистры, каждый из которых содержит запоминающий регистр и цифровой сумматор, причем цифровой вход первого числа каждого сумматора соединен с цифровым входом устройства, а- цифровой вход второго числа каждого сумматора г с выходами соответствующего запоминающего регистра, выход каждого сумматора соединен с входом запоминающего регистра, младшие разрядные входы суммирующего цифроаналогового преобразователя попарно соединены с разрядными выходами запоминающих регистров , О1 личающийся тем, что, с целью повышения динамической точности цифрового фазового детектирования, в него введены два элемента И, элемент ИЛИ, два элемента задержки и D -триггер, причем тактовые входы устройства соединены с первыми входами элементов И и входами элементов задержки, а выходы последних соединены с тактовыми входами запоминающих регистров, выходы -элементов И соединены с входами элемента ИЛИ, выход которого соеС динен с тактовым входом D-триггера, информационный вход последнего соединен с выходом переполнения цифрового сумматора первого накопительного регистра, выход 1)-триггера соединен с входом старшего разряда суммирующего цифроаналогового преобразователя, вторые входы элементов И соединены с выходами переполнения цифровых сумматоров накопительных регистров. О5 00 сх со СХ)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ цифрового фазового детектирования | |||

| - Радиотехника, т | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1984-01-23—Публикация

1982-03-12—Подача