1

Изобретение относится к автоматике и вычислительной технике и может найти применение в качестве устройства управления системами в реальном масштабе времени.

Цель изобретения - снижение аппа- ратурньГх затрат на устройство для программного управления системами, функционирующими по жесткой временной циклограмме.

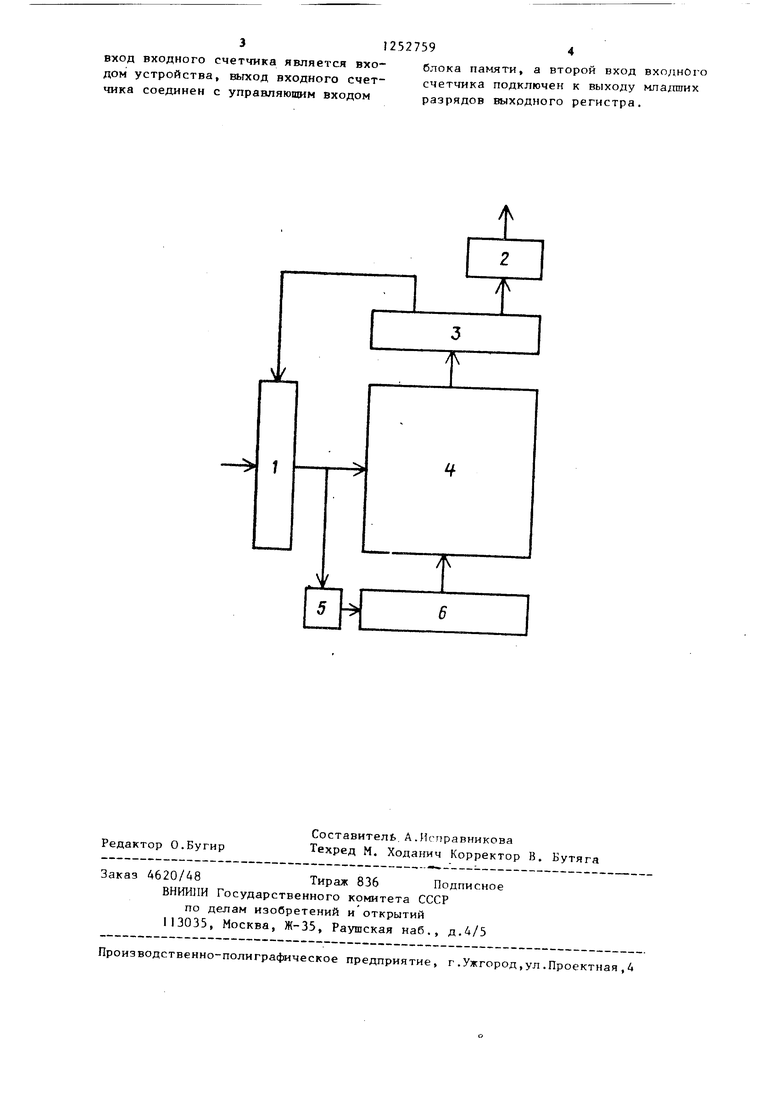

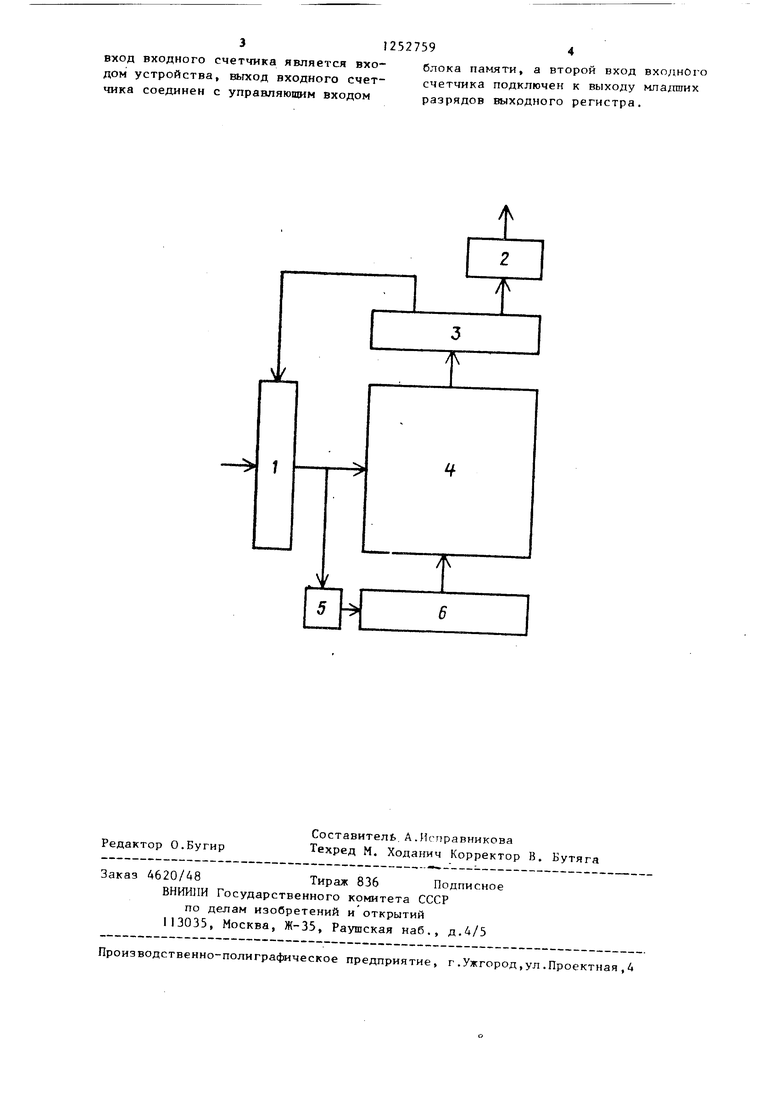

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит входной счетчик 1, дешифратор 2, выходной регистр 3, блок 4 памяти, элемент 5 задержки, счетчик 6 адреса.

Каждая ячейка памяти блока 4 содержит код операции и код временного интервала, через который должна быть выполнена следующая команда.

Начальная запись в блок 4 памяти может быть осуществлена путем введения дополнительного адресного входа и входа строба записи (цепи начальной записи на чертеже не показаны).

В исходном состоянии во все разряды входного счетчика 1 записаны единицы, счетчик 6 адреса обнулен, что соответствует адресу первой ячейки блока 4 памяти. Сигнал входной частоты, поступивший на вход устройства, вызывает появление сигнала переполнения счетчика 1, который, поступив на управляющий вход (считывания) блока 4 памяти, производит считывание содержимого первой ячейки памяти в выходной регистр 3 . Код операции с т- тарших разрядов регистра 3 поступает на вход дешифратора 2, и на выходе устройства появляется сигнал управления . С выхода uIaдшиx разрядов регистра 3 кг)д н)земенного интервала через ко-горый необходимо выполнить следующую команду, записывается во входной счетчик 1. Задержанный элементом 5 задержки сигнал увеличивает содержимое счетчика 6 адреса на единицу.

Сигналами входной частоты отсчитывается заданный временной интервал между командами. Сигнал переполнения счетчика 1 вызывает считывание содержимого второй ячейки памяти блока 4 и т.д. В дальнейшем работа устройства повторяется.

Управление системами в реальном масштабе времени предполагает выполнение определенной последовательнос527592

ти действий, отстоящих друг от друга

,во времени на различных интервалах.

I

,Например, необходимо вьодать сигнал

на реле для коммутации некоторой це5 пи, а спустя время t включить преобразователь аналог-код и т.п. В известном устройстве выполнение такой последовательности действий можно осушествить применением сигналов

О обратной связи от управляемой системы, введением в блок памяти холостых команд или использованием внетнего таймера. Организация обратных связей от управляемой системы довольна слож 5 на, а Б ряде случаев просто невозможна. Количество вводимых холостых команд N, позволяющих организовать задержку выдачи управляющих команд, определяется временем выборки коман20 ды из блока памяти t и величиной отсчитываемого временного интервала из соотношения . Например, при суммарной задержке в процессе управления мс и времени выборки ко манды 1 МКС, в блок памяти необходимо ввести 1000 холостых команд. Использование внещнего таймера предполагает хранение в некоторой дополнительной памяти кодов отсчиты30 ваемых временшлх интервалов, а также команд их записи в таймер. Кроме того, требуется синхронизировать работу внещнего таймера и блока памяти команд. Во всех перечисленных слу35 чаях в устройстве управления необ- ходим1м существенные аппаратурные затраты .

В предлагаемом устройстве объем памяти уменьшен и за счет исключения.

40 поля памяти, содержащего адрес следующей команды, что также уменьшает аппаратурные затраты.

Формула изобретения,

Устройство для программного уп- ранления, содержащее последовательно соединенные блок памяти, выходной рег истр и дешифратор, выход которого

является выходом устройства, отличающее с я тем, что, с целью снижения аппаратурных затрат при управлении системами по жесткой вре- м€-нной циклограмме, в него введены

последовательно соединенные входной счетчик, элемент задержки и счетчик адреса, выход которого подключен к адресному входу блока памяти, первый

вход входного счетчика является входом устройства, выход входного счетчика соединен с управляющим входом

12527594

блока памяти, а второй вход входного счетчика подключен к выходу младших разрядов выходного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1987 |

|

SU1439533A2 |

| Устройство для программного управления | 1988 |

|

SU1569804A1 |

| Устройство для программного управления | 1989 |

|

SU1728849A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2007760C1 |

| Электронные часы | 1980 |

|

SU928169A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

Изобретение относится к автоматике и вычислительной технике, может найти применение при управлении сие темами в реальном масштабе времени и позволяет снизить аппаратурные затраты. Устройство содержит последовательно соединенные входной счетчик, элемент задержки, счетчик адреса, блок памяти, выходной регистр и дешифратор, выход которого является выходом устройства. Выход младших разрядов выходного регистра соединен с вторым входом входного счетчика, первый вход которого является входом устройства. Выход входного счетчика подключен к управляющему входу блока памяти. В устройство введены входной счетчик, счетчик адреса и элемент задержки, обеспечивающие выборку команд управления с различной частотой что позволяет сократить объем блока Iпамяти. I ил. i сл

Редактор О.Бугир

Составитель. А.Исг равникова

Техред М. Ходанич Корректор В, Бутяга

Заказ 4620/48Тираж 836 Подписное

ВНИИ11И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород,ул.Проектная,4

| Малые ЭВМ и их применение./Под ред | |||

| Б.М.Наумова | |||

| - М.: Статистика, I980, с.105 | |||

| Каган Б.М | |||

| Электронные вычисли- тельные машины и системы | |||

| - М.;Энергия, 1979, с.247, рис.7.2. |

Авторы

Даты

1986-08-23—Публикация

1985-02-12—Подача