Изобретение относится к вычислительной технике и. может быть использовано в специализированных вычислителях при аппаратной реализации функции .

Целью изобретения является повьппе ние быстродействия за счет замены структуры последовательного действия на сдвиговых регистрах структурой параллельного действия на комбинационных элементах.

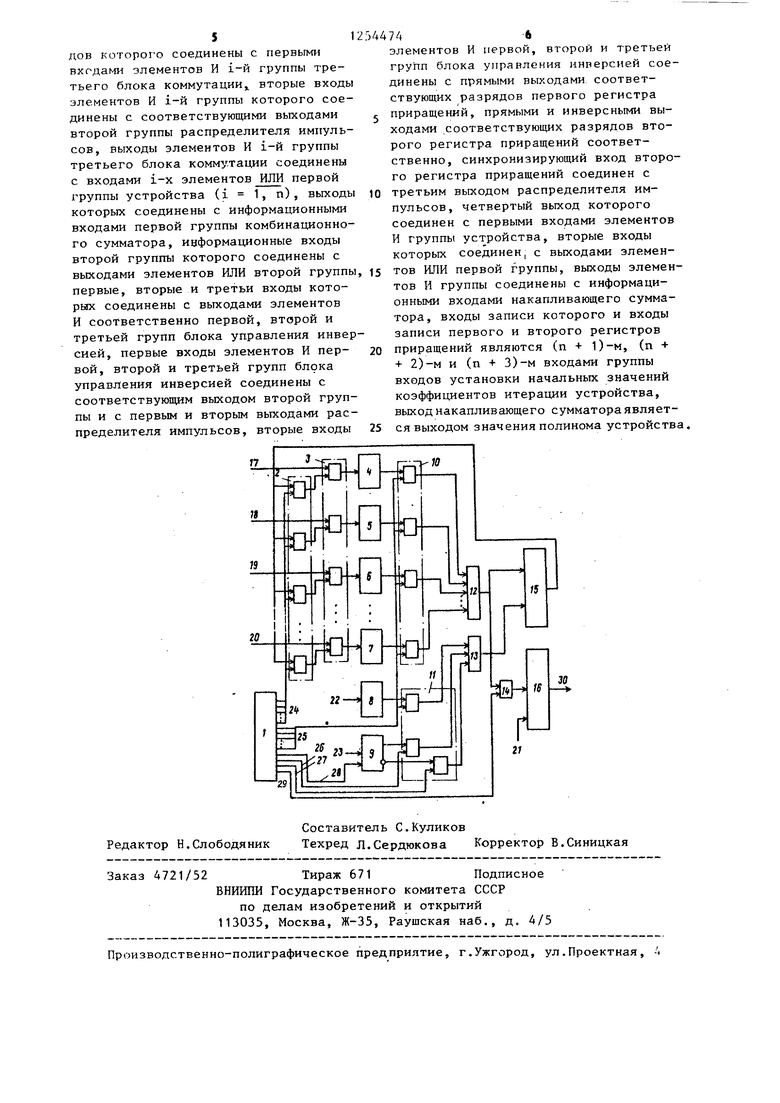

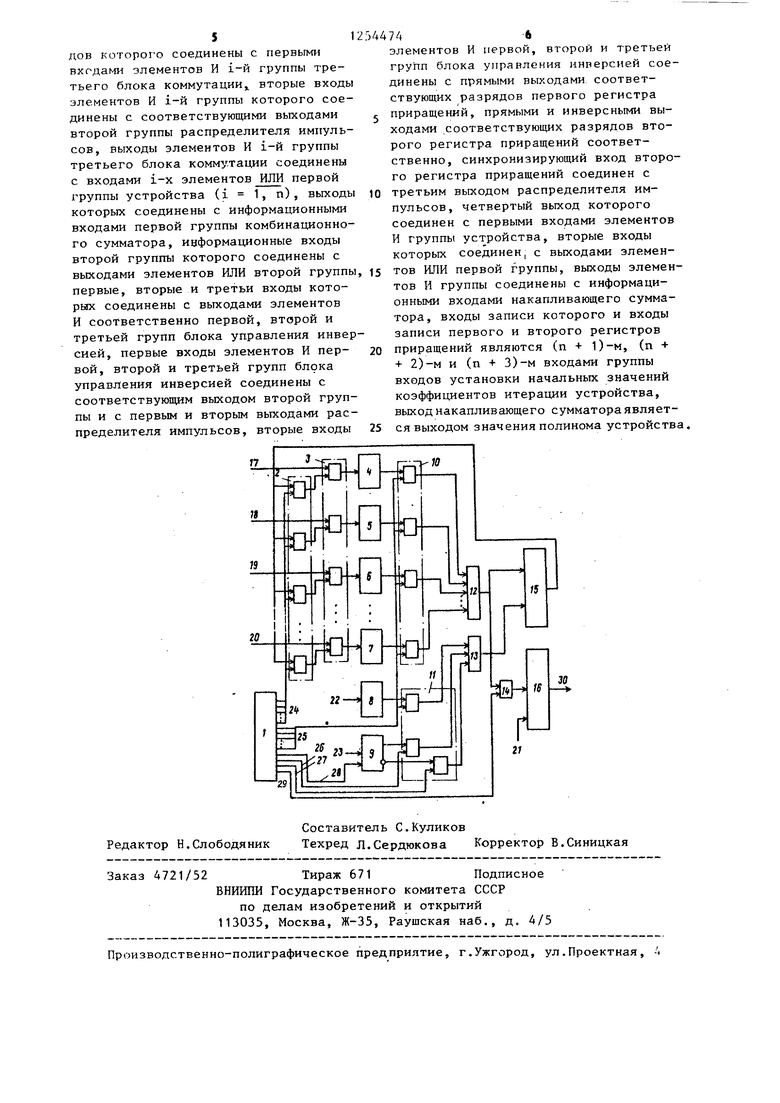

На чертеже представлена функциональная блок-схема устройства.

Устройство содержит распределитель 1 импульсов, первый блок 2 коммутации, второй блок 3 коммутации, регистры 4-7 значений полиномов, первый 8 и второй 9 регистры приращений третий блок 10 коммутации, блок 11 управления инверсией,- первую группу элементов ИЛИ 12, вторую группу элементов ИЛИ 13, группу элементов И 14 комбинационный сумматор 15, накапливающий сумматор 16, группу входов (17-23 установки начальных значений устройства, первый - шестой тактирующие выходы 24-29 распределителя импульсов, выход 30 значения полинома устройства.

Общее выражение реализуемого полинома имеет вид

f(х) ах + Ьх + с ,

где а,Ь,с - коэффициенты полинома.

Устройство работает следующим образом.

Перед началом работы комбинационный сумматор 15 находится в нулевом состоянии. На накапливающий сумматор 16 через вход 21 заносится величина

а --. b 2

+ с.

регистр 4 величина

через вход 17 заноk4N

(2 - 1),

N

разрядность представления х; число разбиений по аргументу X.

На входы 18-20 подаются величины а 2

2р 1,2,..., п - порядковые номера входов 18-20, через которые, начиная с 18-го входа, заносятся указанные величины соответственно на регистры 5-7. На вход 22

ёподается величина д

а +

2N

вход 23 подается величина

s

Вычисление значений полинома осуществляется последовательно для всех значений х. При этом содержимое регистров А-7, полученное на предыдущем цикле, используется для получения последующих значений полинома. В связи с этим цикличность работы регистров 4-7 различна и кх содержимое изменяется с различной периодичностью. Причем содержимое регистра 4 при каждом изменении суммируется с прямым кодом содержимого первого

0

5

0

5

0

5

0

регистра 8 приращения, а содержимое регистров 5-7 при каждом изменении суммируется с прямым или обратным кодом содержимого второго регистра 9 приращения в зависимости от появления тактирующих импульсов соответственно на выходах 25 и 27 или 28. распределителя 1 импульсов. Количество циклов работы устройства равно N. В конце каждого цикла происходит установка в исходное состояние накапливающего сумматора 16.

Тактирующие импульсы с выхода 25 распределителя 1 импульсов выдаются в каждом цикле для передачи содержимого регистра 4 и первого регистра И приращения на вход комбинационно- ,го сумматора 15. Кроме того, этими же импульсами передается содержимое регистра 4 на вход группы элементов И 14 для занесения на накапливающий сумматор 16 тактирующими импульсами с выхода 29 распределителя 1 импульсов.

Выход 24 генератора 1 импульсов служит для занесения с выхода комбинационного сумматора 15 на входы регистров 4-7 величин, полученных на нечетных тактах очередного цикла работы устройства и используемых в последующих циклах.

Вычисление значения функции в точке разбиения по аргументу происходит з-а один цикл, состоящий из 2п тактов. В первом такте величина К

(2 - 1), находящаяся в

4N

регистре 4, через группу элементов и третьего блока 10 коммутации по тактирующему импульсу с выхода 25 распределителя 1 импульсов и через группу элементов ИЛИ 12 поступает на

входы комбинационного сумматора 15, на другие входы которого по же тактирующему импульсу с выхода 25 распределителя 1 импульсов через группу элементов И блока 11 управле- НИИ инверсией и группу элементов ИЛИ 13 поступает содержимое первого регистра 8 приращения. В этом же такте содержимое регистра 4 по тактирующему импульсу с выхода 29 распреде-

лителя 1 импульсов передается через группу элементов И 14 на вход накапливающего сумматора 16 и суммируется с величиной d, занесенной ранее по входу 21. Во втором такте результат алгебраического сложения на комбинационном сумматоре 15 по тактирующему импульсу с выхода 24 распределителя 1 импульсов через группу элементов И первого блока 2 коммутации и через второй блок 3 коммутации заносится в регистр 4. В третьем такте содержимое регистра 5 по тактирующему импульсу с выхода 25 распределителя 1 импульсов через группу элементои И третьего блока 10 коммутацир и через группу элементов ИЛИ 2 поступает на входы комбинационного сумматора 5, на другие входы которого по тактирующему импульсу с выхода 27 через группу элементов И блока 11 управления инверсией и через группу элементов ИЛИ 13 поступает содержимое второго регистра 9 приращения. В этом же третьем такте содержимое регистра 5 по тактирующему импульсу с выхода 29 распределителя 1 импульсов передается через группу элементов И 14 для суммирования с содержимым накапливающего сумматора 16. В четвертом такте результат алгебраического сложения на комбинационном сумматоре 15

1 по тактирующему импульсу с выхода 24

распределителя 1 импульсов через группу элементов И первого блока 2 коммутации и второй блок 3 коммутации заносится в регистр 5. В этом же четвертом такте производится сдвиг содержимого второго регистра 9 приращения на один старЕ ий разряд по управляющему импульсу с выхода 26 распределителя 1 импульсов. Последующие такты работы для каждого из регистров 6-7 аналогичны третьему и четвертому тактам,

После суммирования содержимого последнего п-го регистра 7 на накапливающем суг-дааторе 16 заканчивается

первый цикл работы устройства и на выходе 30 устройства получим первое значение функции для х 0.

Аналогично производится вычисления полинома для значений аргумента х

1,2,3,,Nc новыми значениями содержимьгх регистров 4-7, полученными в предыдущих циклах работы устройства. Значение приращения на первом регистре 8 приращения остается постоянным для полинома. Значение содержимого второго регистра 9 приращения удваивается .

Формула изобретения

Устройство для вычисления полиномов второй степени, содержащее распределитель импульсов, п-регистров значений полиномов (п, - разрядность аргумента) первую группу элементов РШИ, накапливающий сумматор и блок управления инверсией, содержавд й три группы элементов И, отличающееся тем, что, с целью повышения быстродействия за счет замены структуры последовательного действия на сдвиговых регистрах структурой параллельного действия на комбинационных элементах, в него дополнительно введены первый блок коммутации, содержащий i групп элементов И, второй блок коммутации, содержащий п групп элементов ИЛИ, третий блок коммутации, содержащ 1Й п групп элементов И, вторая группа элементов 1ПМ, группа элементов И, два регистра приращения и комбинационный сумматор, причем i-й вход группы входов уста- новки начальных коэффициентов итера- 1ДИЙ устройства (i 1 ,п) соединен с первыми входами элементов ИЛИ i-й .группы второго блока коммутации, вторые входы элементов ГШИ i-й iруппы второго блока коммутации соединены с выходами элементов И i-й группы первого блока коммутации, первые входы элементов И i-й группы которого соединены с выходамз{ соответствующих разрядов комбинационного сумматора, вторые входы элементов И i-й группы (Первого блока коммутации соединены с соответствующими выходами первой группы распределителя импульсов, выходы элементов ИЛИ i-й группы второго блока коммутации соединены с информационными входами i-ro регистра значений полиномов, выходы разря51

дов которого соединены с первыми входами элементов И i-й группы третьего блока коммутации вторые входы элементов И i-й группы которого соединены с соответствующими выходами второй группы распределителя импульсов, выходы элементов И i-й группы третьего блока коммутации соединены с входами i-x элементов ИЛИ первой группы устройства (i 1, п), выходы которых соединены с информационными входами первой группы комбинационного сумматора, информационные входы второй группы которого соединены с выходами элементов ИЛИ второй группы первые, вторые и третьи входы которых соединены с выходами элементов И соответственно первой, второй и третьей групп блока управления инверсией, первые входы элементов И первой, второй и третьей групп блока управления инверсией соединены с соответствующим выходом второй группы и с первым и вторым выходами распределителя импульсов, вторые входы

74-6

элементов И первой, второй и третьей групп блока управления ннперсией соединены с прямыми выходами соответствующих разрядов первого регистра приращений, прямыми и инверсными выходами соответствующих разрядов второго регистра приращений соответственно, синхронизирующий вход второго регистра приращений соединен с

третьим выходом распределителя импульсов, четвертый выход которого соединен с первыми входами элементов И группы устройства, вторые входы которых соединен, с выходами элементов ИЛИ первой группы, выходы элементов И группы соединены с информационными входами накапливающего сумматора, входы записи которого и входы записи первого и второго регистров

приращений являются (п 1)-м, (п + + 2)-м и (п + 3)-м входами группы входов установки начальных значений коэффициентов итерации устройства, выход накапливающего сумматора являетс я выходом значения полинома устройства.

J7

Редактор Н.Слободяник

Составитель С.Куликов

Техред Л.Сердюкова Корректор В.Синицкая

Заказ 4721/52Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для вычисления значения полинома -ой степени | 1978 |

|

SU744559A2 |

| Устройство для воспроизведения функций | 1987 |

|

SU1458876A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Устройство для вычисления полиномов второй степени | 1980 |

|

SU920714A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

Изобретение относится к области вычислительной техники и позволяет с высоким быстродействием выполнять вычисление полиномов второй степени за счет введения параллельной обработки. Устройство содержит распреде - литель импульсов, первый и второй блоки коммутации, регистры значений полиномов, первый и второй регистры приращений, третий блок коммутации, блок управления инверсией, две группы элементов ИЛИ, группу элементов И, комбинационный сумматор, накапливающий сумматор. Устройство осуществляет вычисление полиномов вида f(x) ах + вх + с где а,Ь,с - коэффициенты полинома . Аргумент х представляется п-раэрядным числом, вычисления значений полинома выполняются последовательно для 2 значений аргумента X. 1 ил. с (О (Л

| Цифровое вычислительное устройство | 1975 |

|

SU561961A1 |

| Устройство для вычисления полиномов второй степени | 1980 |

|

SU920714A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1984-12-04—Подача