Изобретение относится к автомати- ке и вычислительной технике и может быть использовано для сопряжения двух раэноскоростных устройств обработки данных,

Цель изобретения - повьшение надежности рабочего устройства при вводе-выводе информации и одновременном поступлении синхросигналов записи и считывания

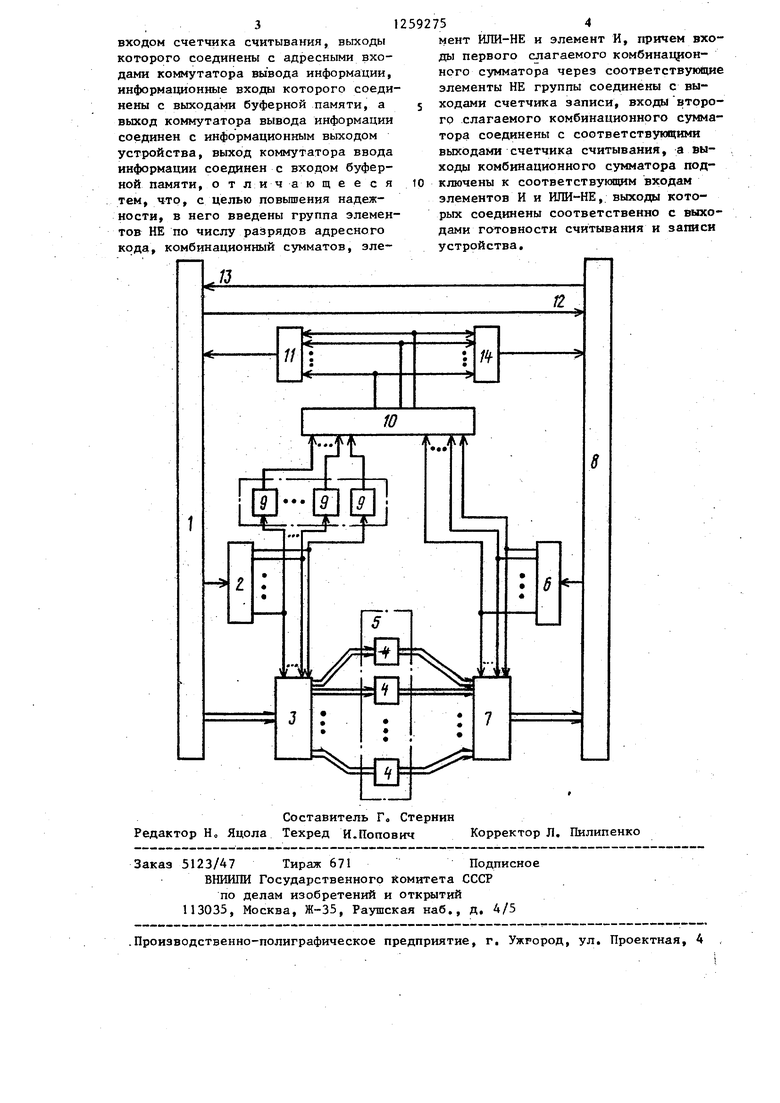

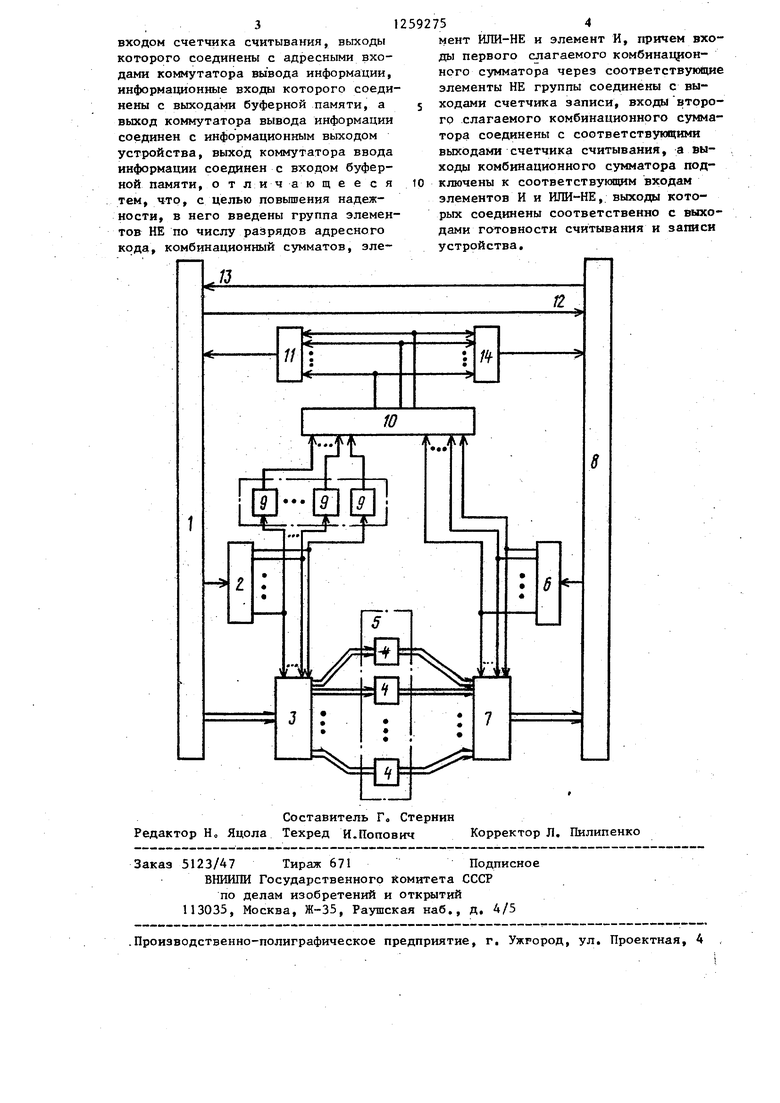

На чертеже представлена конструкция устройства.

Устройство содержит источник 1 информации, счетчик 2 записи, коммутатор 3 ввода информации, регистры 4 буферной памяти 5, счетчик 6 считывания, коммутатор 7 выводы информации, приемник 8 информации, группу элементов ЦЕ 9, комбинационный сумматор 10, элемент ИЛИ-НЕ 11, вход 12 приемника 8, вход 13 источника 1 и элемент И 14,

Устройство работает следующим образом.

Перед процессом передачи после- довательности дискретных сигналов источник 1 посьтает сигнал Запрос на прием на вход 12 приемника 8, который на данный сигнал выдает на вход 13-источника 1 сигнал Готов к приему. После этого источник 1 генерирует последовательность ко- дод, которые поступают на вход коммутатора 3, Одновременно каждый сигнал последовательности сопровождает синхроимпульс записи, кото1.1й поступает на вход счетчика 2, выдающий адреса для подключения входа коммутатора 3 к соответствующему регистру 4 буферной памяти 5,, Адресные коды с выхода счетчика 2 через группу элементов НЕ 9 поступают также на вход первого слагаемого комбинационного сумматора 10. Таким образом, с записью первого сигнала последовательности, т.е. с,появлением первого синхроимпульса записи на вьпсоде элемента И 14 формируется сигнал Готовность считывания информации, который разрешает считывание информации приемнику 8.

С появлением на тактовом входе счетчика 6 импульсов считывания он выдает адрес на коммутатор 7, кото- .рый подключает выход соответствующего регистра 4 буферной памяти 5 на вход приемника 8 синхронно с импульсами считывания. Счетчик 6 совместно с коммутатором 7 работает таким образом, что считывание сигналов происходит аналогично их порядку записи. Адресные коды с выхода скет

чика 6 поступают также на вход вто--. рого слагаемого комбинационного сумматора 10. Таким образом, в процессе записи и считывания на выходе комбинационного сумматора получается инверсия кода, равного количеству регистров 4 памяти 5, в которых хранится еще.несчитыванная информация. Так как запись и считьшание происходят с различной скоростью, то в

буферной памяти 5 может не оставаться свободного регистра для записи последующего кода. Этот момент определяется элементом ИЛИ-НЕ 11 при наличии на выходе сумматора 10 нулевого кода. С выхода элемента ИЛИ- НЕ 11 вьщается сигнал блокировки записи, который поступает на соответ- ствуняций вход источника 1 и запрещает вьщачу кодов на вход коммутатора 3 и соответствующих синхроимпульсов. После считывания информации хотя бы из одно1 о регистр 4, изменяется код на выходе сумматора 10 и снимается сигнал блокировки

записи с выхода элемента РШИ-НЕ 11. Запись будет продолжена в свободные регистры, т.е. в регистры, информация в которых была считана,

Если считывание происходит быстрее записи, то при наличии на вьтходе сумматора 10 единичного кода, что означает отсутствие несчитанной информации в регистрах 4, элемент И 14 выдает в приемник 8 сигнал блокировки чтения. Сигнал будет сохраняться до тех пор, пока информация не будет записана хотя бы в один регистр.

Формула изобретения

УсЧ-ройство для сопряжения, содеращее буферную память, счетчики записи и считывания, коммутаторы ввода и вывода информации, причем информационный вход коммутатора ввода информации соединен с информационным входом устройства, адресные входы коммутатора ввода информации соединены с выходами счетчика записи,

тактовой вход которого соединен с первым синхронизирующим входом устройства, второй синхронизирующий вход которого соединен с тактовым

входом счетчика считывания, выходы которого соединены с адресными входами коммутатора вывода информации, информационные входы которого соеди нены с выходами буферной памяти, а выход коммутатора вывода информации соединен с информационным выходом устройства, выход коммутатора ввода информации соединен с входом буферной памяти, о т личаю щ е е с я тем, что, с целью повьшения надежности, в него введены группа элемен тов НЕ по числу разрядов адресного кода, комбинационный сумматов, эле

2592754

мент ИЛИ-НЕ и элемент И, гфичем входы первого слагаемого комбинагцгон- ного сумматора через соответствующие элементы НЕ группы соединены с вы- 5 ходами счетчика записи, входы второго слагаемого комбинационного сумматора соединены с соответствующими выходами счетчика считывания, а выходы комбинационного сумматора под- 10 ключены к соответствукядим входам элементов И и ИЛИ-НЕ, выходы которых соединены соответственно с выходами готовности считывания и записи устройства.

Составитель Г, Стернин Редактор Но Яцола Техред И.Попович Корректор Л. Пилипенко

Заказ 5123/47 Тираж 671Подписное

ВНИШШ Государственного Комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

.Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1990 |

|

SU1835546A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1559351A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

Изобретение относится к области автоматики и вычислительной технике и может быть использовано для сопряжения двух разноскоростных устройств обработки данных при одновременном поступлении синхросигналов записи и считывания. Целью изобретения является повьппение надежности устройства Устройство содержит два счетчика синхроимпульсов, комму таторы ввода-вывода информации, буферную память, группу элементов НЕ, комбинационный сумматор, элементы И, ИЛИ-НЕ, 1 ил. ю ел

| Ткацкий станок для выработки тканей гарнитурового переплетения | 1948 |

|

SU75232A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-03-15—Подача