CS .

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1985 |

|

SU1259275A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1559351A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для сопряжения разно- скоростных устройств обработки и передачи данных при одновременном поступлении синхроимпульсов записи и считывания. Устройство содержит счетчики, коммутаторы, буферную память, элементы НЕ, два комбинационных сумматора, два элемента ИЛИ- НЕ. элемент И, блоки .совпадения кодов, регистр (управления буферной памятью) и элемент ИЛИ. Работа устройства состоит в организации обмена информацией между источником и приемником, при этом изменение размерности буферной памяти дает возможность управлять скоростью передани информации от источника к приемнику, когда запись информации происходит быстрее считывания. 1 ил.

Изобретение относится к области автоматики и вычислительной техники, может быть использовано для сопряжения разно- скоростных устройств обработки и передачи данных при одновременном поступлении сигналов записи и считывания.

Цель изобретения - расширение функциональных возможностей устройства за счет управления размерностью буферной памяти, используемой при обмене информацией, что позволяет влиять на скорость обмена информацией.

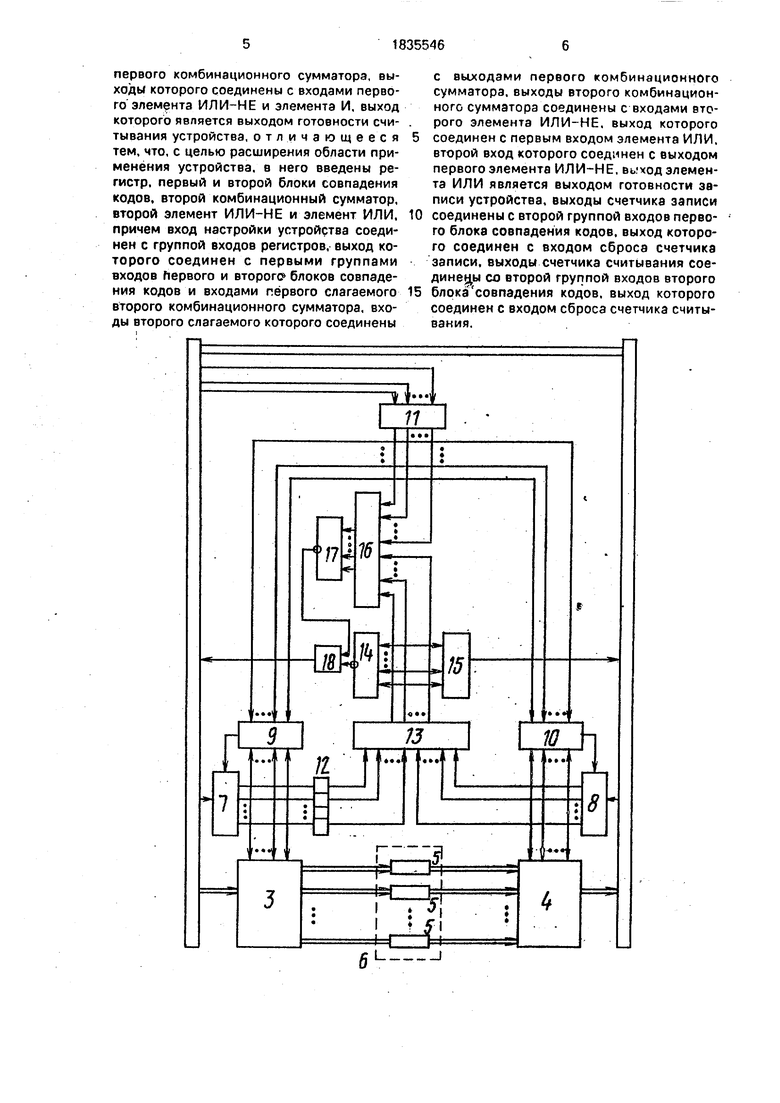

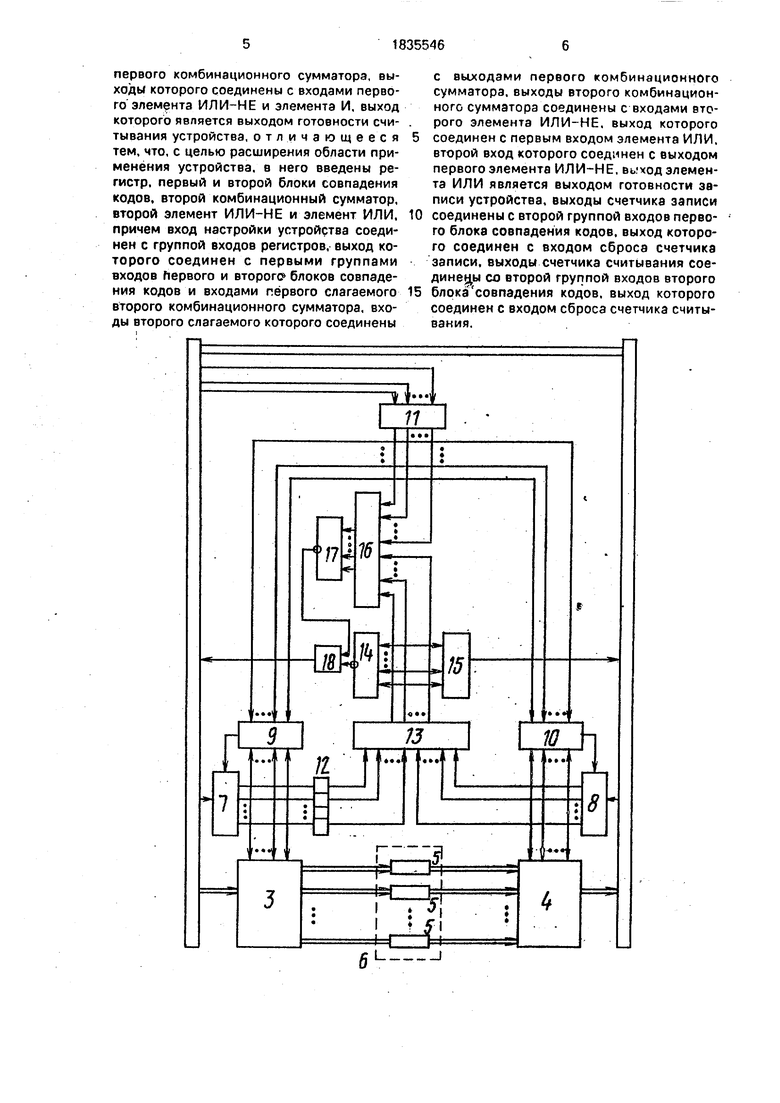

На чертеже представлена схема устройства.

Устройство содержит источник 1 и приемник 2 информации, коммутаторы ввода 3 и вывода 4 информации, регистры 5 буферной памяти 6, счетчики 7 записи и 8 считывания, блоки совпадения кодов 9 и 10.

регистр 11, группу элементов НЕ 12, комбинационные сумматоры 13 и 16, элементы ИЛИ-НЕ 14 и 17. элемент И 15, элемент ИЛИ 18. вход 19 приемника 2 и вход 20 источника 1.

Устройство работает следующим образом.

Перед процессом передачи информации источник 1 посылает сигнал Запрос на прием на вход 1.9 приемника 2. который при готовности к работе выдает на вход 20 источника 1 сигнал Готов к приему. После этого источник 1 информации, исходя из данных о требуемом при обмене информацией объеме буферной памяти, через вход настройки устройства заносит в регистр 11 код, соответствующий числу регистров 5. за- действуемых при обмене. При этом первоначально на первый синхронизирующий

00 CJ

ел ел

.N

о

вход устройства выдается синхроимпульс записи, который поступает на тактовый вход счетчика 7, В счетчике 7 записи формируется адресный код, поступающий на адресные входы коммутатора 3 ввода информации, который подключает информационный вход устройства к соответствующему регистру 5 буферной памяти 6, Источник: 1 выдает информацию в очередной регистр 5. При выдаче очередного синхроимпульса в случае совпадения кодов в счетчике 7 записи л регистре 11 срабатывает первый блок 9 совпадения кодов, сигнал с которого обнуляет счетчик 7 записи. Очередной информационный код записывается в нулевой регистр 5 буферной памяти 6, что ограничивает число используемых при обмене информацией регистров.

При наличии информации в буферной памяти 6 на второй синхронизирующий вход устройства выдается синхроимпульс считывания, который/юступает на тактовый вход счетчика 8. В счетчике 8 считывания формируется адресный код, поступающий на адресные входы коммутатора 4 вывода информации, который подключает соответствующий регистр 5 буферной памяти б к информационному выходу устройства. Приемник 2 принимает информацию из очередного регистра 5. При выдаче очередного синхроимпульса в случае совпадения кодов в счетчике 8 считывания и регистре 11 срабатывает второй блок 10 совпадения кодов, сигнал с которого обнуляет счетчик 8 считывания. Очередной информационный код считывается из нулевого регистра 5 буферной памяти 6, что ограничивает число .используемых при обмене информацией регистров.

Поскольку запись и считывание информации в буферную память происходит с различной скоростью, необходимо фиксировать моменты полного считывания информации полного заполнения буферной памяти. Для определения этих моментов адресные коды со счетчика 7 записи через инверторы 12 и со счетчика 8 считывания подаются на входы комбинационного сумматора 13. На выходах сумматора 13 формируется код, отражающий количество регистров 5 буферной памяти 6, хранящих несчитанную информацию.

В случае, когда считывание информации происходит быстрее записи, момент полного считывания информации из буферной памяти.определяётся единичным кодом на выходе сумматора 13. Этот код формирует на выходе элемента Л 15 сигнал блокировки чтения, который передается в приемник информации 2. Сигнал будет сохраняться до тех пор, пока информация не будет записана хотя бы в один регистр.

В случае, когда запись информации происходит быстрее считывания, момент полного заполнения буферной памяти определяется двумя способами. Во-первых, при этом возможна ситуация, что адресный код на счетчике 7 записи на единицу меньше адресного кода на счетчике 8 считывания.

Это состояние соответствует нулевому коду на выходе сумматора 13. Данный код формирует на выходе первого элемента ИЛИ- НЕ 14 сигнал блокировки записи, который передается через элемент ИЛИ 18 в источ5 ник информации 1. Сигнал будет сохраняться до тех пор, пока информация не будет считана еще хотя бы из одного регистра 5. Во-вторых,в связи с произвольным числом используемых в передаче регистров 5 в бу0 ферной памяти 6 возможна ситуация, когда адресный код на счетчике записи 7 соответствует максимальному номеру используемого в буферной памяти 6 регистра 5, а адресный код на счетчике считывания 8 ну5 левой. Это состояние счетчиков соответствует нулевому коду на выходе второго комбинационного сумматора 16, поскольку на его входы первого слагаемого подается инверсный адресный код счетчика 7 записи,

0 а на входы второго слагаемого код с регистра 11. Данный код формирует на выходе второго элемента ИЛИ-НЕ 17 сигнал блокировки записи, который передается через элемент ИЛИ 18 в источник 1.

5 формула изобретения

Устройство для сопряжения, содержащее буферную память, счетчики записи и считывания, коммутаторы ввода и вывода информации, группу элементов НЕ, первый

0 комбинационный сумматор, первый элемент ИЛИ-НЕ и элемент И, причем информационный вход коммутатора ввода информации является информационным входом устройства, а выходы соединены с

5 входами буферной памяти, выходы которой соединены с информационными входами коммутатора вывода информации, выход которого является информационным выходом устройства, первым синхронизирующим

0 входом которого является тактовый вход счетчика записи, а его выходы соединены с адресными входами коммутатора ввода информации и входами элементов НЕ, выходы которых соединены со входами первогосла5 гаемого первого комбинационного сумматора, вторым синхронизирующим входом устройства является тактовый вход счетчика считывания, а его выходы соединены с адресными входами коммутатора вывода информации и входами второго слагаемого

первого комбинационного сумматора, выходы которого соединены с входами первого элемента ИЛИ-НЕ и элемента И, выход которого является выходом готовности считывания устройства, отличающееся тем, что, с целью расширения области применения устройства, в него введены регистр, первый и второй блоки совпадения кодов, второй комбинационный сумматор, второй элемент ИЛИ-НЕ и элемент ИЛИ, причем вход настройки устройства соединен с группой входов регистров, выход которого соединен с первыми группами входов Первого и второго блоков совпадения кодов и входами первого слагаемого второго комбинационного сумматора, входы второго слагаемого которого соединены

с выходами первого комбинационного сумматора, выходы второго комбинационного сумматора соединены с входами второго элемента ИЛИ-НЕ. выход которого

соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ, выход элемента ИЛИ является выходом готовности записи устройства, выходы счетчика записи

соединены с второй группой входов первого блока совпадения кодов, выход которого соединен с входом сброса счетчика записи, выходы счетчика считывания сое- динен ы со второй группой входов второго

блрка совпадения кодов, выход которого соединен с входом сброса счетчика считывания.

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1985 |

|

SU1259275A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-23—Публикация

1990-07-02—Подача