Изобретение относится к вычислительной технике и предназначено для преобразования числа из системы остаточных классов (СОК) в позиционный «.од и определения знака числа.

Цель изобретения - повышение быстродействия.

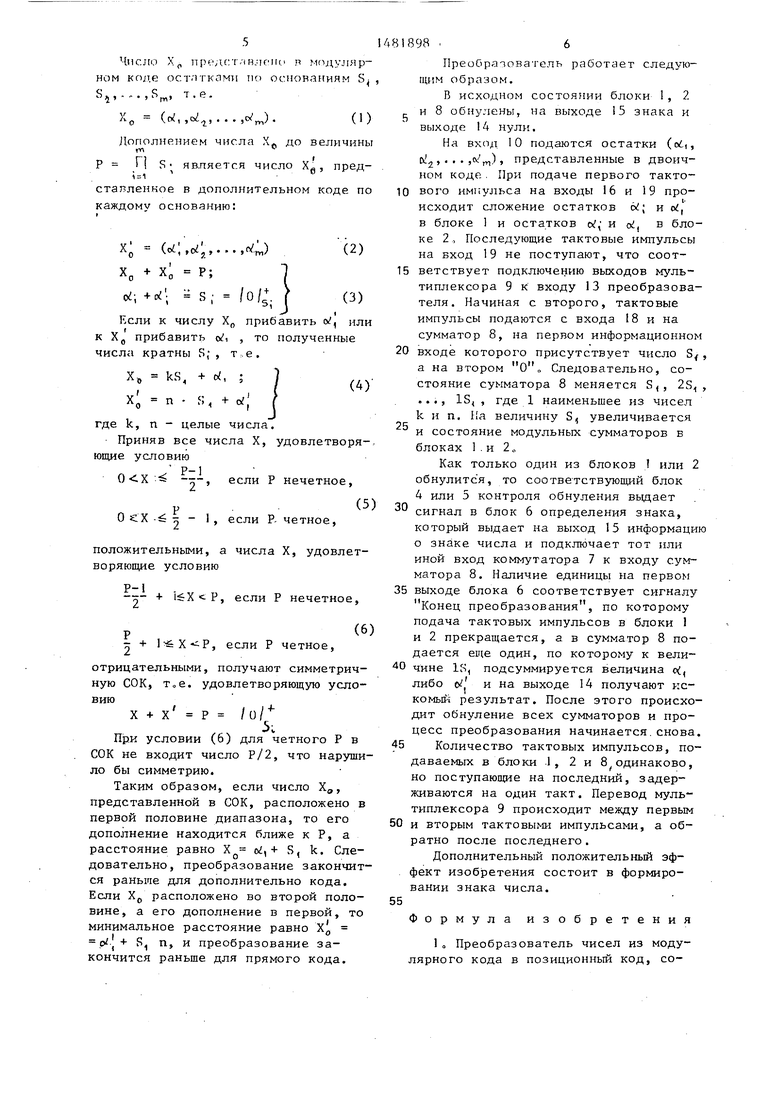

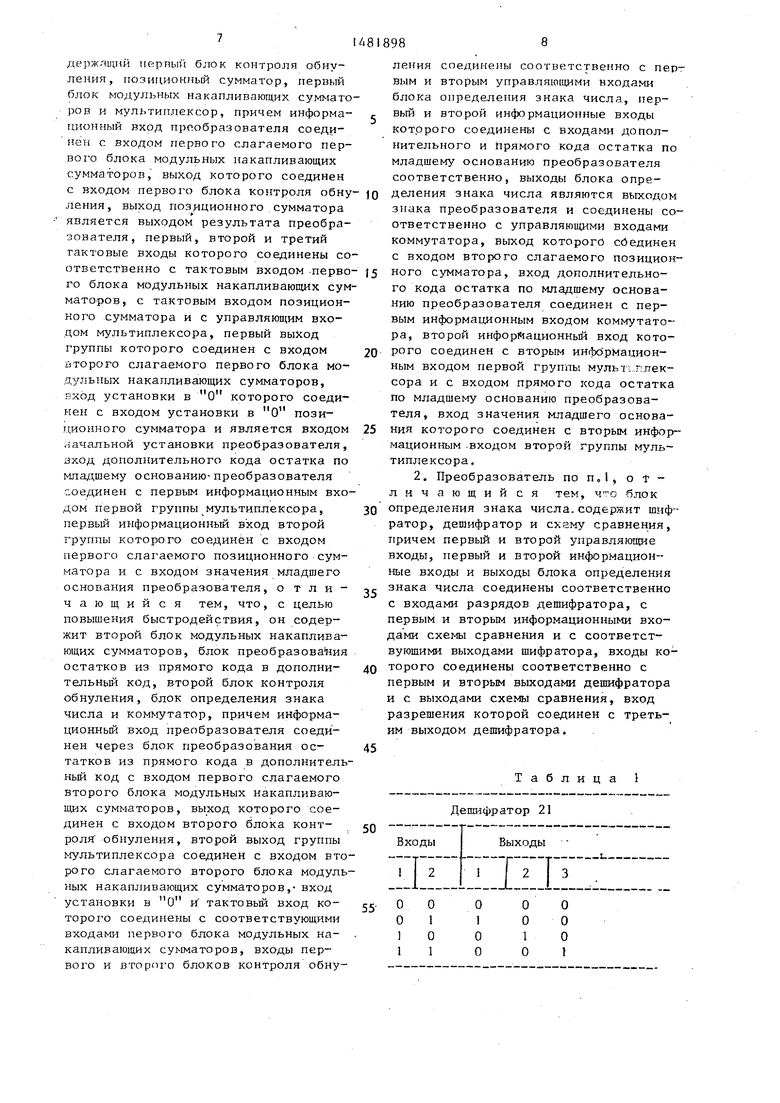

На фиг.1 представлена схема преобразователя чисел из модулярного кода в позиционный код; на фиг.2 - схема блока определения знака числа. Преобразователь (фиг.1) содержит первый блок 1 модульных накапливающих сумматоров, второй блок 2 модульных накапливающих сумматоров, блок 3 преобразования остатков из прямого кода в дополнительный код, первый 4 и второй 5 блоки контроля обнуления, блок 6 определения знака числа, коммутатор 7, позиционный сумматор 8, мультиплексор 9, информационньй вход 10 преобразователя, входы 11 и 12 дополнительного и прямого кода остатка по младшему основанию преобразователя, вход 13 значения младшего ос- нования преобразователя, выход 14 результата преобразователя, выход 13 знака преобразователя, первый тактовый вход 16 преобразователя, вход 17 начальной установки преобразователя, второй тактовый вход 18 преобразователя. Блок 6 определения знака числа (фиг.2} содержит шифратор 20, дешифратор 2.1 и схему 22 сравнения.

Блоки 4 и 5 комбинационные, на их выходах появляется сигнал логической 1, если на выходах блоков 1 и 2 нулевые значения.

Блок 6 определения знака числа

представляет собой комбинационный блок. На входы дешифратора 21 пода

5 0 О

5

0

ются сигналы с выходов блоков контроля обнуления, а на входы схемы 22 сравнения - остатки , и оЈ „ Третий выход дешифратора 21 является уп. равляющим для схемы сравнения, при появлении единицы, на котором, что соответствует появлению единицы на обоих входах дешифратора 21 ,, включается в работу схема 22 сравнения.

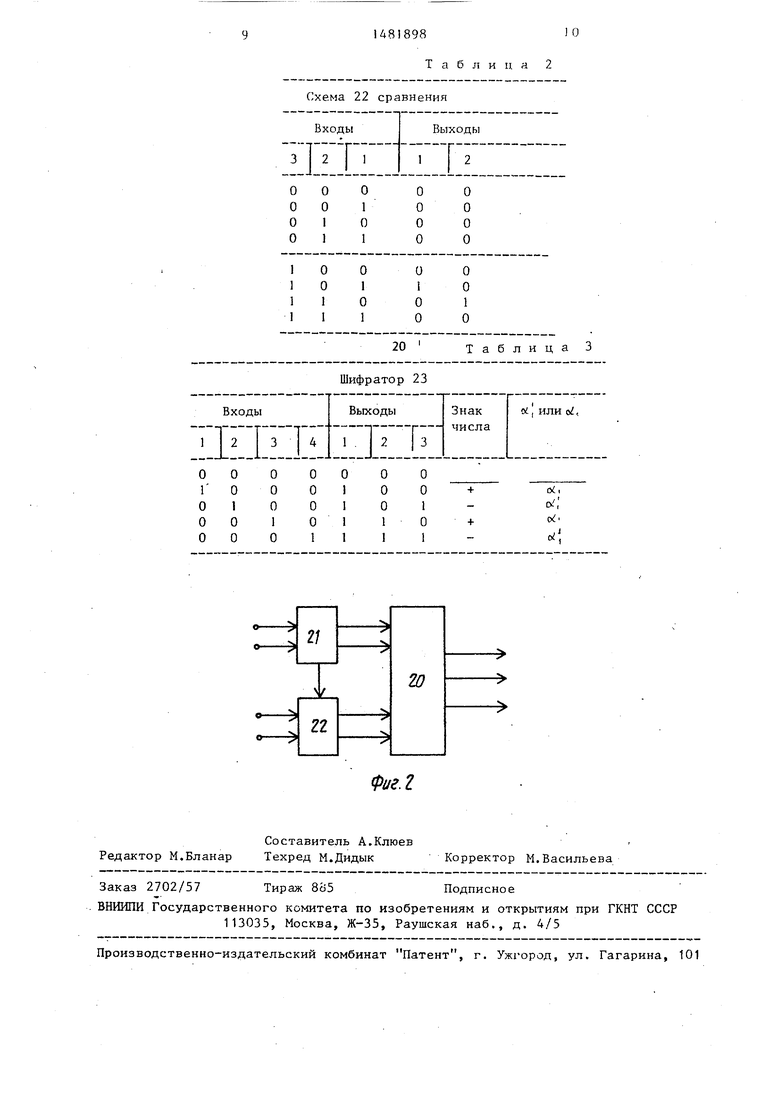

Дешифратор 21, схема 22 сравнения и шифратор 20 для одного двоичного разряда (для других - структура сохраняется) описываются соответственно табл.1-3.

При одновременном обнулении блоков 1 и 2 определение знака и последнего слагаемого о, производится путем сравнения величин oit и о, для которых выполнение условия oi, - & 1 может быть только при оЈ, оЈ ( 0. Но такая ситуация возникает только при приведении всего преобразователя в исходное состояние обнуление . Логика работы блока 6 исключает ложный сигнал при появлении такого состоя - ния„ Из табл.1 - 3 видно, что если ot, oij 0 и на входах дешифратора две единицы, соответствующие одновременно обнуленным блокам 1 и 2, то на выходах дешифратора все нули.

Коммутатор 7 выполнен любым известным способом,, вариант соответствия управляющего кода и коммутируемых входов представлен в табл.3, так как выходы шифратора являются прав- ляющими входами коммутатора.

Сумматор 8 накапливающего типа тактируемый.

В преобразователе (фиг.1) реализуется следующий алгоритм работы.

51

Число X 0 прсдс 1в:к Мо я модуляр- ном коде остлг коми по основаниям S , S4,.-.,Sm, т.е.

Х0 U,,o,...,O.(1)

Дополнением числа Х„ до величины т

Р MS- явпяется число Хе, предА 1

стаяленкое в дополнительном коде по каждому основанию:

«,,...,О + х; Р;

+ S; /0/5+.

(2)

(3)

Если к числу Х0 прибавить о, или к Х0 прибавить оЛ , то полученные числа кратны R; , те.

Х„ kS, + d, ; „i

-о s + ,

п

где k, n - целые числа.

Приняв все числа X, удовлетворяющие условию / Р-1

о если Р нечетное,

tО ЈХ - т; - I , если Р- четное,

положительными, а числа X, удовлетворяющие условию

Р-1

- + , если Р нечетное,

р

+ , если Р четное,

отрицательными, получают симметричную СОК, т.е. удовлетворяющую условию

X + X Р / 0 /

V

При условии (6) для четного Р в СОК не входит число Р/2, что нарушило бы симметрию.

Таким образом, если число Х0, представленной в СОК, расположено в первой половине диапазона, то его дополнение находится ближе к Р, а расстояние равно XQ oi, + S, k. Следовательно, преобразование закончится раньше для дополнительно кода. Если Х0 расположено во второй половине, а его дополнение в первой, то минимальное расстояние равно Х o i + R1 n, и преобразование закончится раньше для прямого кода.

1

,

25

.6

ПреоОрлтователь работает следующим образом.

В исходном состоянии блоки 1, 2 и 8 обнулены, на выходе 15 знака и выходе 14 нули.

На вход 10 подаются остатки (оЈ,, ,. . . ,о,;т), представленные в двоичном коде При подаче первого такто- 10 вого импульса на входы 16 и 19 происходит сложение остатков и oi, в блоке 1 и остатков с,1 и od, в блоке 2, Последующие тактовые импульсы на вход 19 не поступают, что соот- 15 ветствует подключению выходов мультиплексора 9 к входу 13 преобразователя. Начиная с второго, тактовые импульсы подаются с входа 18 и на сумматор 8, на первом информационном 20 входе которого присутствует число S, а на втором Следовательно, состояние сумматора 8 меняется S, 2S1, ..., 1S(, где 1 наименьшее из чисел k и п. На величину S, увеличивается и состояние модульных сумматоров в блоках 1 и 2„

Как только один из блоков или 2 обнулится, то соответствующий блок 4 или 5 контроля обнуления выдает 30 сигнал в блок 6 определения знака, который выдает на выход 15 информацию о знаке числа и подключает тот или иной вход коммутатора 7 к входу сумматора 8. Наличие единицы на первом 35 выходе блока 6 соответствует сигналу Конец преобразования, по которому подача тактовых импульсов в блоки 1 и 2 прекращается, а в сумматор 8 подается еще один, по которому к вели- 40 чине IS, подсуммируется величина с, либо у и на выходе 14 получают искомый результат. После этого происходит обнуление всех сумматоров и процесс преобразования начинается снова. 45 Количество тактовых импульсов, подаваемых в блоки 1, 2 и 8 одинаково, но поступающие на последний, задерживаются на один такт. Перевод мультиплексора 9 происходит между первым 50 и вторым тактовыми импульсами, а обратно после последнего.

Дополнительный положительный эффект изобретения состоит в формировании знака числа. 55

Формула изобретения

1 о Преобразователь чисел из модулярного кода в позиционный код, со

лерж.чщий перпый блок контроля обнуления, позиционный сумматор, первый блок модульных накапливающих сумматоров и мультиплексор, причем информа- ционный вход преобразователя соединен с входом первого слагаемого первого блока модульных накапливающих сумматоров, выход которого соединен с входом первого блока контроля обну ления, выход позиционного сумматора является выходом результата преобразователя, первый, второй и третий тактовые входы которого соединены соответственно с тактовым входом перво го блока модульных накапливающих сумматоров, с тактовым входом позиционного сумматора и с управляющим входом мультиплексора, первый выход группы которого соединен с входом второго слагаемого первого блока модульных накапливающих сумматоров, РХОД установки в О которого соединен с входом установки в О позиционного сумматора и является входом начальной установки преобразователя, зход дополнительного кода остатка по младшему основанию-преобразователя г.оединен с первым информационным входом первой группы мультиплексора, первый информационный вход второй группы которого соединен с входом первого слагаемого позиционного сумматора и с входом значения младшего основания преобразователя, отличающийся тем, что, с целью повышения быстродействия, он содержит второй блок модульных накапливающих сумматоров, блок преобразования остатков из прямого кода в дополнительный код, второй блок контроля обнуления, блок определения знака числа и коммутатор, причем информационный вход преобразователя соединен через блок преобразования остатков из прямого кода в дополнительный код с входом первого слагаемого второго блока модульных накапливающих сумматоров, выход которого соединен с входом второго блока контроля обнуления, второй выход группы мультиплексора соединен с входом второго слагаемого второго блока модульных накапливающих сумматоров,- вход установки в О и тактовый вход которого соединены с соответствующими входами первого блока модульных накапливающих сумматоров, входы первого и второго блоков контроля обну

0

5

Q 5

0

5

0

ления соединены соответственно с первым и вторым управляющими входами блока определения знака числа, первый и второй информационные входы которого соединены с входами дополнительного и прямого кода остатка по младшему основанию преобразователя соответственно, выходы блока определения знака числа являются выходом знака преобразователя и соединены соответственно с управляющими входами коммутатора, выход которого соединен с входом второго слагаемого позиционного сумматора, вход дополнительного кода остатка по младшему основанию преобразователя соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с вторым информационным входом первой группы мулы, г пек- сора и с входом прямого кода остатка по младшему основанию преобразователя, вход значения младшего основания которого соединен с вторым информационным входом второй группы мультиплексора,

2. Преобразователь по п„1, о т - л и чающий ся тем, чт блок определения знака числа.содержит шифратор, дешифратор и схему сравнения, причем первый и второй управляющие входы, первый и второй информационные входы и выходы блока определения знака числа соединены соответственно с входами разрядов дешифратора, с первым и вторым информационными входами схемы сравнения и с соответствующими выходами шифратора, входы которого соединены соответственно с первым и вторым выходами дешифратора и с выходами схемы сравнения, вход разрешения которой соединен с третьим выходом дешифратора.

Таблица 1 Дешифратор 21

Таблииа 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Устройство для определения позиционной характеристики непозиционного кода | 1985 |

|

SU1275779A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1986 |

|

SU1388996A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для преобразования кода системы остаточных классов в десятичный код | 1984 |

|

SU1167600A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Преобразователь модулярного кода в позиционный код | 1988 |

|

SU1587639A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования числа из системы остаточных классов /СОК/ в позиционный код и определения знака числа. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что преобразователь, содержащий блок 1 модульных накапливающих сумматоров, блок 4 контроля обнуления, позиционный сумматор 8 и мультиплексор 9, содержит блок 2 модульных накапливающих сумматоров, блок 3 преобразования остатков из прямого кода в дополнительный код, блок 5 контроля обнуления, блок 6 определения знака числа и коммутатор 7 с соответствующими связями. Сущность изобретения состоит в том, что преобразование в позиционный код происходит по двум каналам в прямом и дополнительном кодах одновременно. 1 з.п.ф, 2 ил.

Схема 22 сравнения

Входы

ы

ОО

ОО

О1

О1

1

о о 1 1

Шифратор 23

Выходы

о 1

о 1

о о о о

о о о о

о i

о о

о о 1 о

20

Таблица 3

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1985 |

|

SU1267625A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-23—Публикация

1987-08-03—Подача