Изобретение относится к вычислительной технике и может быть использовано для подготовки и ввода информации в системах автоматизированного проектирования (САПР), а также в системах управления технологическими процессами (СУТП).

Целью изобретения является расширение области применения путем обес- печения контроля вводимой информации .в произвольной ячейке памяти.

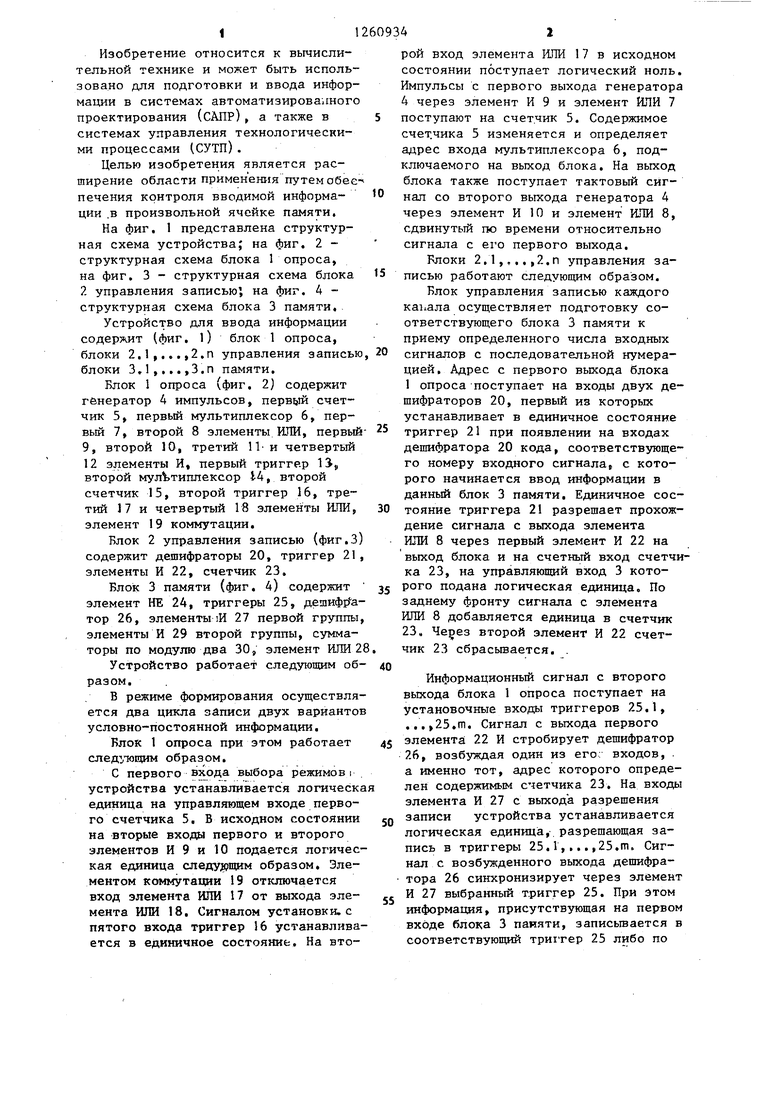

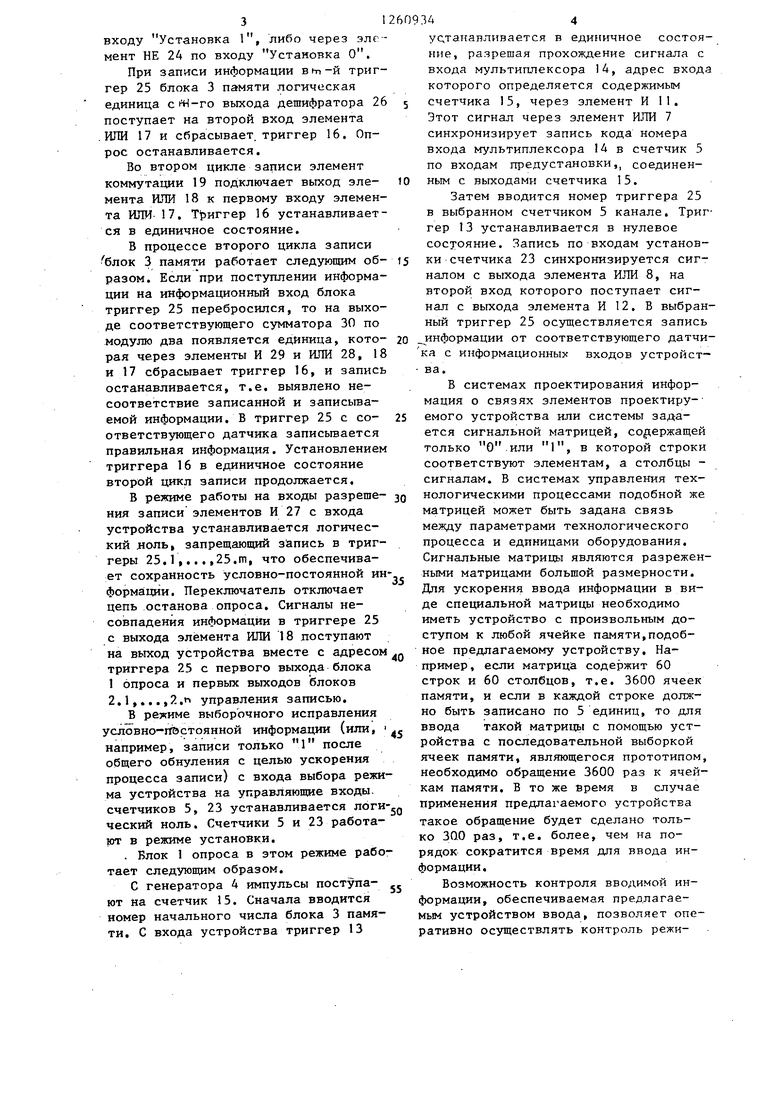

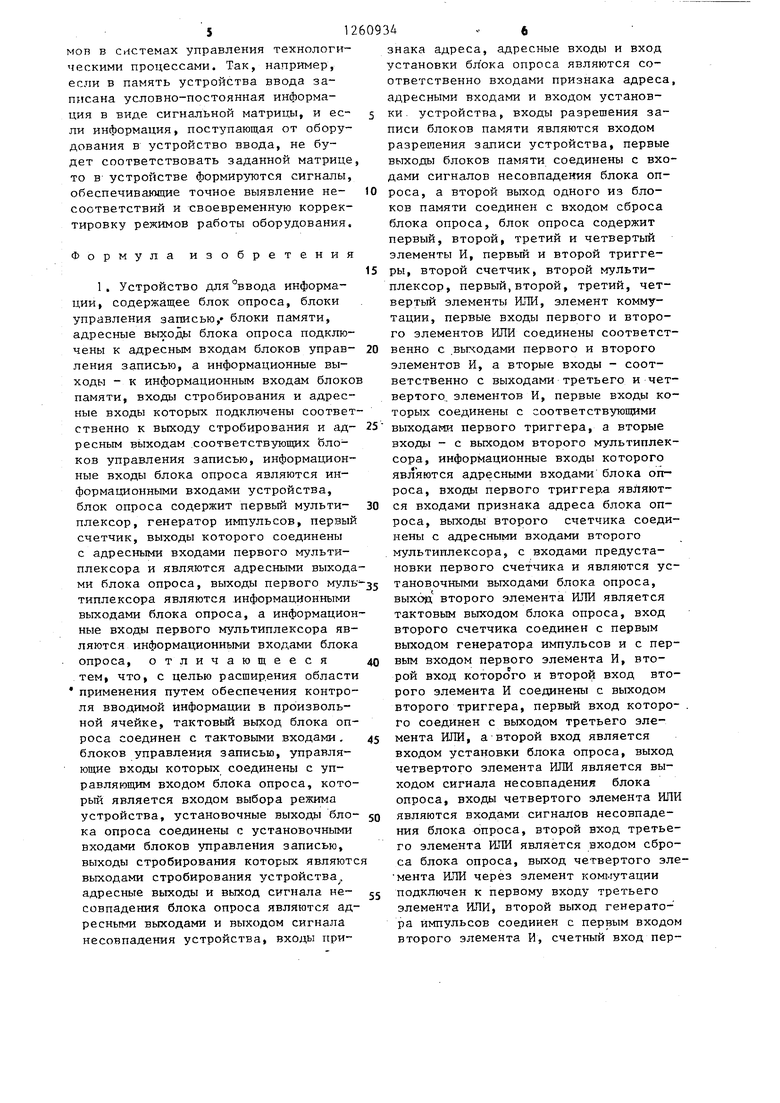

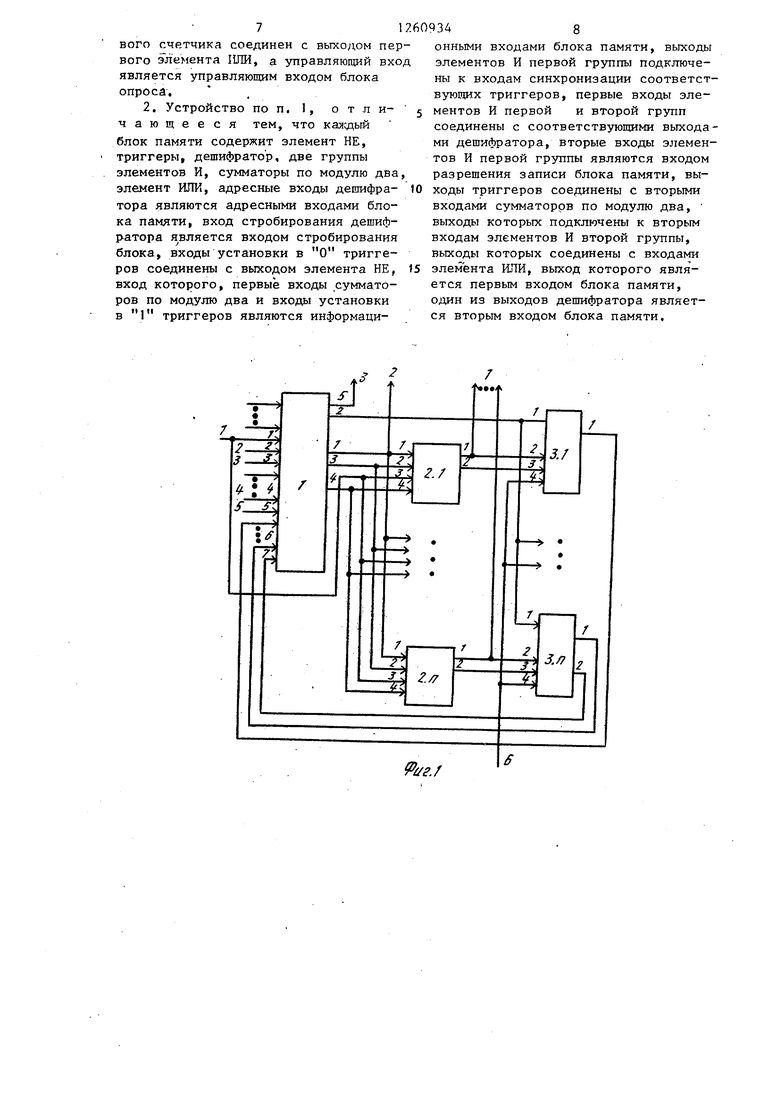

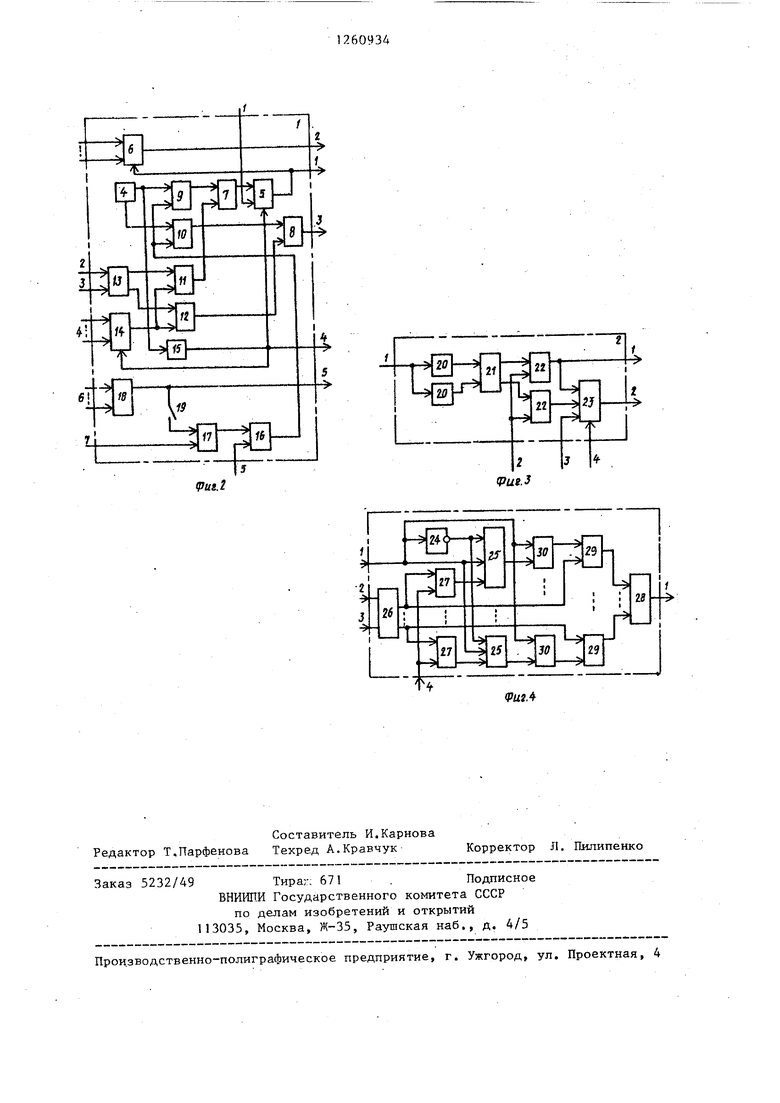

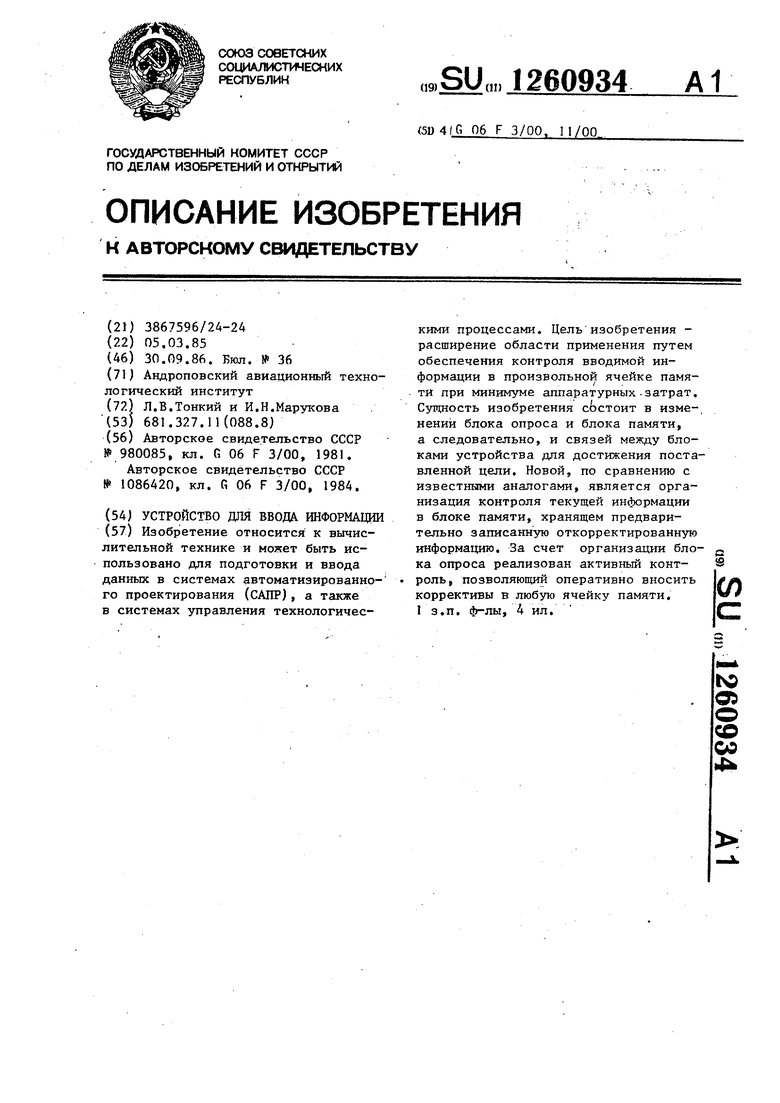

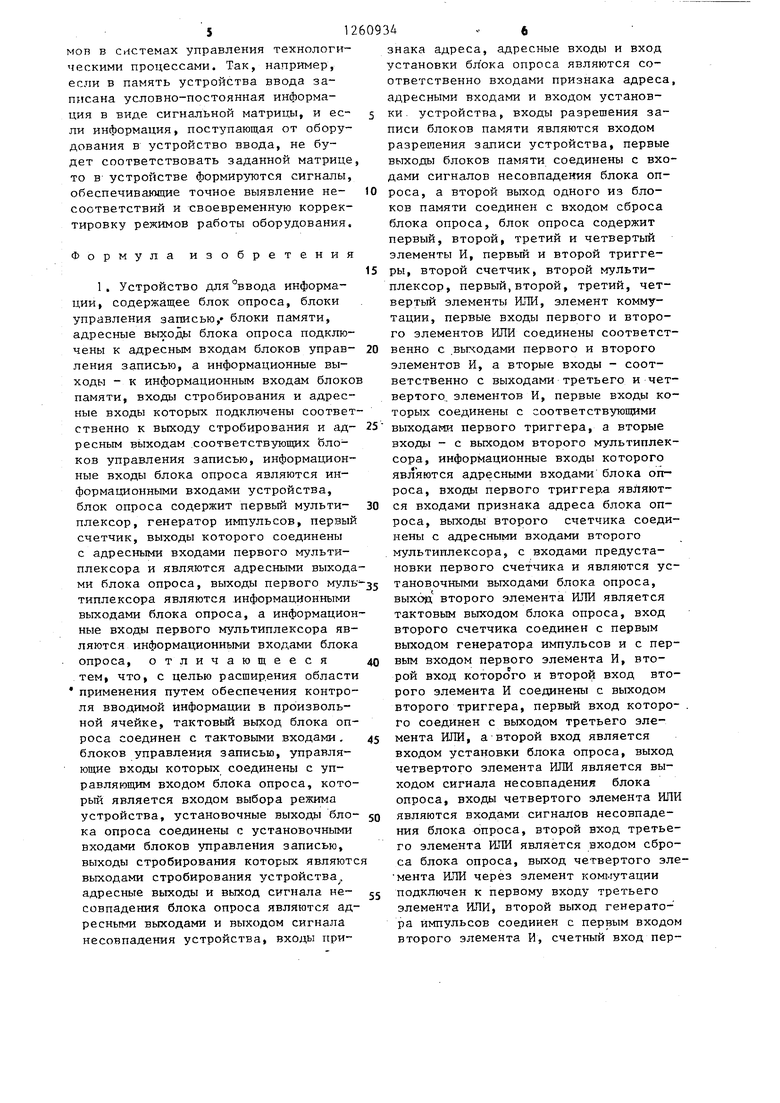

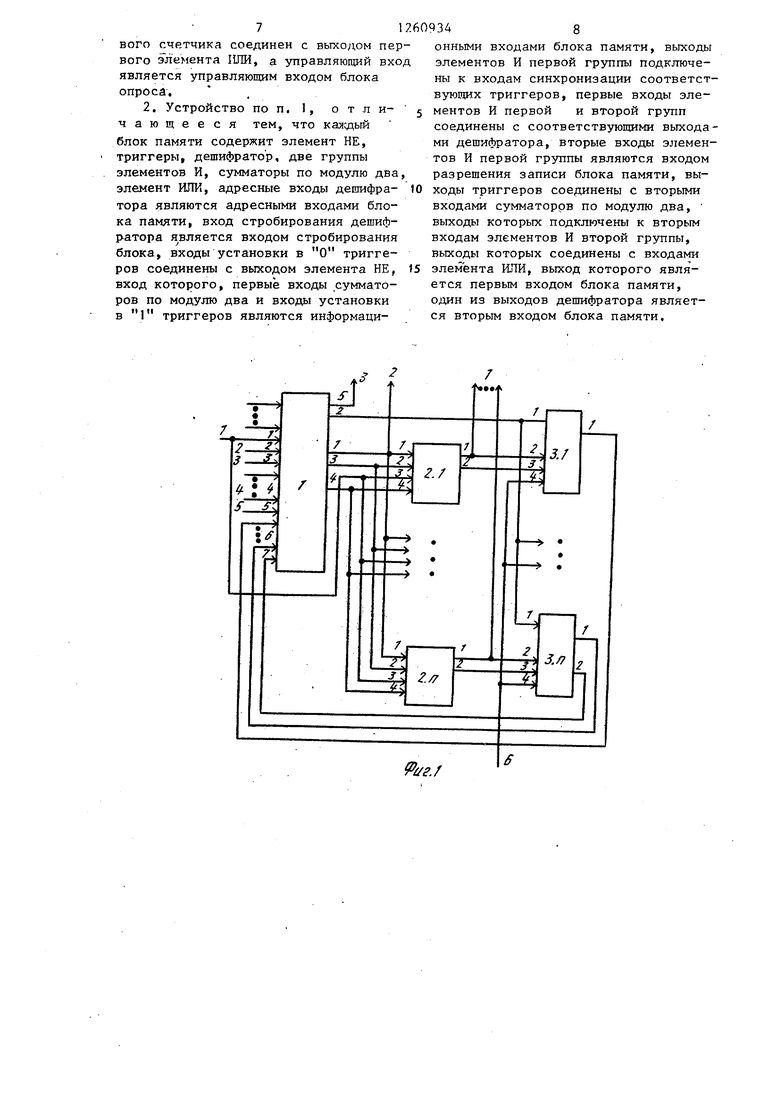

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока 1 опроса, на фиг. 3 - структурная схема блока 2 управления записью; на фиг. 4 - структурная схема блока 3 памяти.

Устройство для ввода информации содержит (фиг. l) блок 1 опроса,

блоки 2.12.П управления записью

блоки 3,1,...,З.п памяти.

Блок 1 опроса (фиг. 2) содержит генератор 4 импульсов, первый счетчик 5, первый мультиплексор 6, первый 7, второй 8 элементы ИЛИ, первый 9, второй 10, третий и четвертый

12 элементы И, первый триггер 13, второй мул типлексор 14, второй счетчик 15, второй триггер 16, третий 17 и четвертый 18 элементы ИЛИ, элемент 19 коммутации.

Блок 2 управления записью (фиг.З) содержит дешифраторы 20, триггер 21 , элементы И 22, счетчик 23.

Блок 3 памяти (фиг. 4) содержит элемент НЕ 24, триггеры 25, дешифг а- тор 26, элементы 1И 27 первой группы, элементы И 29 второй группы, сумматоры по модулю два 30, элемент И,ПИ2

Устройство работает следующим образом.

В режиме формирования осуществляется два цикла записи двух вариантов условно-постоянной информации.

Блок 1 опроса при этом работает след:,тощим образом.

С первого входа выбора режимов устройства устанавливается логическа единица на управляющем входе первого счетчика 5. В исходном состоянии на вторые входы первого и второго элементов И 9 и 10 подается логическая единица следу К1Щим образом. Элементом коммутации 19 отключается вход элемента ИЛИ 17 от выхода элемента ИЛИ 18. Сигналом установки, с пятого входа триггер 16 устанавливается в единичное состояние. На вто

0

15

25

20

30

35

40

45

50

55

рой вход элемента ИЛИ 17 в исходном состоянии поступает логический ноль. Импульсы с первого выхода генератора 4 через элемент И 9 и элемент ИЛИ 7 поступают на счетчик 5. Содержимое счет.чика 5 изменяется и определяет адрес входа мультиплексора 6, подключаемого на выход блока. На выход блока также поступает тактовый сигнал со второго выхода генератора 4 через элемент И 10 и элемент ИЛИ 8, сдвинутый по времени относительно сигнала с его первого выхода.

Блоки 2.1,,..,2.п управления записью работают следующим образом.

Блок управления записью каждого ка11ала осуществляет подготовку соответствующего блока 3 памяти к приему определенного числа входных сигналов с последовательной нумерацией. Адрес с первого выхода блока 1 опроса поступает на входы двух дешифраторов 20, первый из которых устанавливает в единичное состояние триггер 21 при появлении на входах дешифратора 20 кода, соответствующего номеру входного сигнала, с которого начинается ввод информации в данный блок 3 памяти. Единичное состояние триггера 2 разрешает прохождение сигнала с выхода элемента ИЛИ 8 через первый элемент И 22 па выход блока и на счетный вход счетчика 23, на управляющий вход 3 которого подана логическая единица. По заднему фронту сигнала с элемента ИЛИ 8 добавляется единица в счетчик 23, второй элемент И 22 счетчик 23 сбрасывается. .

Информационный сигнал с второго выхода блока I опроса поступает на установочные входы триггеров 25.1, ...,25.т. Сигнал с выхода первого элемента 22 И стробирует дешифратор 26, возбуждая один из его; входов, а именно тот, адрес которого определен содержимым счетчика 23. На входы элемента И 27 с выхода разрешення записи устройства устанавливается логическая единица, разрешающая запись в триггеры 25,1,...,25.т. Сигнал с возбулсденного выхода дешифратора 26 синхронизирует через элемент И 27 выбранный триггер 25. При этом информация, присутствующая на первом входе блока 3 паняти, записьгаается в соответствующий триггер 25 либо по

3

входу Установка 1, либо через элемент НЕ 24 по входу Установка О.

При записи информации внп-й триггер 25 блока 3 памяти логическая единица выхода дешифратора 2 поступает на второй вход элемента .ИЛИ 17 и сбрасывает, триггер 16. Опрос останавливается.

Во втором цикле записи элемент коммутации 19 подключает выход эле- мента ИЛИ 18 к первому входу элемента ИЛИ- 17. Триггер 16 устанавливается в единичное состояние.

В процессе второго цикла записи блок 3 памяти работает следующим об разом. Если при поступлении информации на информационный вход блока триггер 25 перебросился, то на выходе соответствующего сумматора 30 по модулю два появляется единица, кото рая через элементы И 29 и ИЛИ 28, 1 и 17 сбрасывает триггер 16, и запис останавливается, т.е. выявлено несоответствие записанной и записываемой информации. В триггер 25 с со- ответствующего датчика записьгаается правильная информация. Установлением триггера 16 в единичное состояние второй цикл записи продолжается.

В режиме работы на входы разреше- ния записи элементов И 27 с входа устройства устанавливается логический яоль, запрещающий запись в триггеры 25. Г,... ,25.П1, что обеспечива

ет сохранность условно-постоянной ин- ными матрицами большой размерности. Jj ,

формации. Переключатель отключает цепь останова опроса. Сигналы несовпадения информации в триггере 25 с выхода элемента ИЛИ 18 поступают на выход устройства вместе с адресом д триггера 25 с первого выхода блока 1 опроса и первых выходов блоков 2.1,... ,2.|- управления записью.

В режиме выборочного исправления условно-ггэстоянной информации (или, например, записи только 1 после общего обнуления с целью ускорения процесса записи) с входа выбора режима устройства на управляющие входы, счетчиков 5, 23 устанавливается логи- ческий ноль. Счетчики 5 и 23 работают в режиме установки.

, Блок 1 опроса в этом режиме работает следующим образом.

С генератора 4 импульсы поступа- ют на счетчик 15. Сначала вводится номер начального числа блока 3 памяти. С входа устройства триггер 13

Для ускорения ввода информации в ви де специальной матритда необходимо иметь устройство с произвольным доступом к любой ячейке памяти,подобное предлагаемому устройству. Например, если матрица содержит 60 строк и 60 столбцов, т.е. 3600 ячеек памяти, и если в каждой строке должно быть записано по 5 единиц, то для ввода такой матриць с помощью устройства с последовательной выборкой ячеек памяти, являющегося прототипом необходимо обращение 3600 раз к ячей кам памяти. В то же время в случае применения предлагаемого устройства такое обращение будет сделано только 300 раз, т.е. более, чем на порядок сократится время для ввода информации .

Возможность контроля вводимой информации, обеспечиваемая пре.длагае- мьм устройством ввода, позволяет опе ративно осуществлять контроль режиус,танапливается в единичное состояние, разрешая прохождение сигнала с входа мультиплексора 14, адрес вход которого определяется содержимым счетчика 15, через элемент И П. Этот сигнал через элемент ИЛИ 7 синхронизирует запись кода номера входа мультиплексора 14 в счетчик 5 по входам предустановки,, соединенным с выходами счетчика 15.

Затем вводится номер триггера 25 в выбранном счетчиком 5 канале. Триггер 13 устанавливается в нулевое состояние. Запись по входам установки счетчика 23 синхронизируется сигналом с выхода элемента ИЛИ 8, на второй вход которого поступает сигнал с выхода элемента И 12. В выбранный триггер 25 осуществляется запись информации от соответствующего датчика с информационных входов устройства.

В системах проектирования информация о связях элементов проектиру- емого устройства или системы задается сигнальной матрицей, содержащей только О,или 1, в которой строки соответствуют элементам, а столбцы - сигналам. В системах управления технологическими процессами подобной же матрицей может быть задана связь между параметрами технологического процесса и единицами оборудования. Сигнальные матрицы являются разреженными матрицами большой размерности. ,

Для ускорения ввода информации в виде специальной матритда необходимо иметь устройство с произвольным доступом к любой ячейке памяти,подобное предлагаемому устройству. Например, если матрица содержит 60 строк и 60 столбцов, т.е. 3600 ячеек памяти, и если в каждой строке должно быть записано по 5 единиц, то для ввода такой матриць с помощью устройства с последовательной выборкой ячеек памяти, являющегося прототипом необходимо обращение 3600 раз к ячейкам памяти. В то же время в случае применения предлагаемого устройства такое обращение будет сделано только 300 раз, т.е. более, чем на порядок сократится время для ввода информации .

Возможность контроля вводимой информации, обеспечиваемая пре.длагае- мьм устройством ввода, позволяет оперативно осуществлять контроль режи5126093А

в системах управления технологиими процессами. Так, например, в память устройства ввода зана условно-постоянная информав виде сигнальной матрицы, и ее- 5 нформация, поступающая от оборуния в устройство ввода, не бусоответствовать заданной матрице, устройстве формируются сигналы, печивающие точное выявление не- 10 ветствий и своевременную корреквку режимов работы оборудования.

зн ус от ад ки пи ра вы да ро ко бл пе эл ры пл ве та го ве эл в ве то вы вх с я с н м н в т в в м м

Формула изобретения

1. Устройство для °ввода информации, содержащее блок опроса, блоки управления записью, блоки памяти, адресные выходы блока опроса подключены к адресным входам блоков управления записью, а информационные выходы - к информационным входам блоков памяти, входы стробирования и адресные входы которых подключены соответственно к выходу стробирования и адресным выходам соответствующих блоков управления записью, информационные входы блока опроса являются ин- формахщонными входами устройства, блок опроса содержит первый мультиплексор, генератор импульсов, первый

с адресными входами первого мультиплексора и являются адресными выходами блока опроса, выходы первого мулн типлексора являются информационными выходами блока опроса, а информационные входы первого мультиплексора являются информационным и входами блока опроса, отличающееся теМ| что, с целью расширения области применения путем обеспечения контроля вводимой информации в прбизволь- ной ячейке, тактовый вьгход блока опроса соединен с тактовыми входами, блоков управления записью, управляющие входы которых соединены с управляющим входом блока опроса, который является входом выбора режима устройства, установочные выходы бло- ка опроса соединены с установочными входами блоков управления записью, выходы стробирования которых являютс выходами стробирования устройства, адресные выходы и выход сигнала не- совпадения блока опроса являются адресными выходами и выходом сигнала несовпадения устройства, входы при50

5

0

50

з о 5 o 5

знака адреса, адресные входы и вход установки бл ока опроса являются соответственно входами признака адреса, адресными входами и входом установки, устройства, входы разрешения записи блоков памяти являются входом разрешения записи устройства, первые выходы блоков памяти соединены с входами сигналов несовпадения блока опроса, а второй вьгход одного из блоков памяти соединен с входом сброса блока опроса, блок опроса содержит первый, второй, третий и четвертый элементы И, первый и второй триггеры, второй счетчик, второй мультиплексор, первый,второй, третий, четвертый элементы ИЛИ, элемент коммутации, первые входы первого и второго элементов ИЛИ соединены соответственно с .выходами первого и второго элементов И, а вторые входы - соответственно с выходами третьего и четвертого, элементов И, первые входы которых соединены с соответствующими выходами первого триггера, а вторые входы - с выходом второго мультиплексора, информационные входы которого являются адресными входами блока опроса, входы первого триггера являются входами признака адреса блока опроса, выходы второго счетчика соединены с адресными входами второго мультиплексора, с входами предустановки первого счетчика и являются установочными выходами блока опроса, выход второго элемента ИЛИ является тактовьм выходом блока опроса, вход второго счетчика соединен с первым выходом генератора импульсов и с первым входом первого элемента И, второй вход KOTOpoVo и второй вход второго элемента И соединены с выходом второго триггера, первый вход которо- . го соединен с выходом третьего элемента ИЛИ, а второй вход является входом установки блока опроса, выход четвертого элемента ИЛИ является выходом сигнала несовпадения блока опроса, входы четвертого элемента ИЛИ являются входами сигналов несовпадения блока опроса, второй вход третьего элемента ИЛИ является входом сброса блока опроса, выход четвертого эле- мента ИЛИ через элемент коммутации подключен к первому входу третьего элемента ИЛИ, второй вьгход генератора импульсов соединен с первым входом второго элемента И, счетный вход первого счетчика соединен с выходом первого элемента IfflH, а з равляющий вход является управляющим входом блока опроса, .

2. Устройство по п, 1, отличающееся тем, что каясдый блок памяти содержит элемент НЕ, триггеры, дешифратор, две группы элементов И, сумматоры по модулю два, элемент ИЛК, адресные входы дешифратора являются адресными входами блока памяти, вход стробирования дещиф- ратора я вляется входом стробирования блока, в ходы установки в О триггеров соединены с выходом элемента НЕ, вход которого, первые входы сумматоров по модулю два и входы установки в 1 триггеров являются информаци

онными входами блока памяти, выходы элементов И первой группы подключены к входам синхронизации соответствующих триггеров, первые входы элементов И первой и второй групп соединены с соответствующими выходами дешифратора, вторые входы элементов И первой группы являются входом разрешения записи блока памяти, выходы триггеров соединены с вторыми входами сумматоров по модулю два, выходы которых подключены к вторым входам элементов И второй группы, выходы которых соединены с входами элемента ИЛИ, выход которого является первым входом блока памяти, один из выходов дешифратора является вторым входом блока памяти.

Pus. 2

Рие.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества проводного монтажа | 1983 |

|

SU1108466A1 |

| Устройство для контроля электрического монтажа | 1989 |

|

SU1698843A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство для контроля матриц памяти на цилиндрических магнитных пленках с неразрушающим считыванием информации | 1986 |

|

SU1387045A1 |

| Устройство для ввода информации | 1986 |

|

SU1319017A1 |

| Устройство цикловой синхронизации | 1988 |

|

SU1721835A1 |

| Устройство для ввода информации | 1984 |

|

SU1201842A1 |

Изобретение относится к вычислительной технике и может быть использовано для подготовки и ввода данных в системах автоматизированно- го проектирования (САПР), а также в системах управления технологическими процессами. Цель изобретения - расширение области применения путем обеспечения контроля вводимой информации в произвольной ячейке памяти при минимуме аппаратурных .затрат. Сущность изобретения сЬстоит в изме-, нений блока опроса и блока памяти, а следовательно, и связей между блоками устройства для достижения поставленной цели. Новой, по сравнению с известными аналогами, является организация контроля текущей информации в блоке памяти, хранящем предварительно записанную откорректированную информацию. За счет организации бло- д ка опроса реализован активный контроль, позволяющий оперативно вносить коррективы в любую ячейку памяти. 1 з.п. ф-лы, 4 ил. (Л с 1C Од о со 00 4

| Устройство для ввода информации от датчиков | 1981 |

|

SU980085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1982 |

|

SU1086420A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-05—Подача