Пчск

4

со ю j;ih

О5 00

Изобретение относится к вьиисли- тельной технике и может быть использовано в устройствах автоматического контроля, диагностики и локализации неисправностей в радиоэлектронной аппаратуре,

Цель изобретения - повышение достоверности контроля при локализации отказов до наименьшего съемного узла

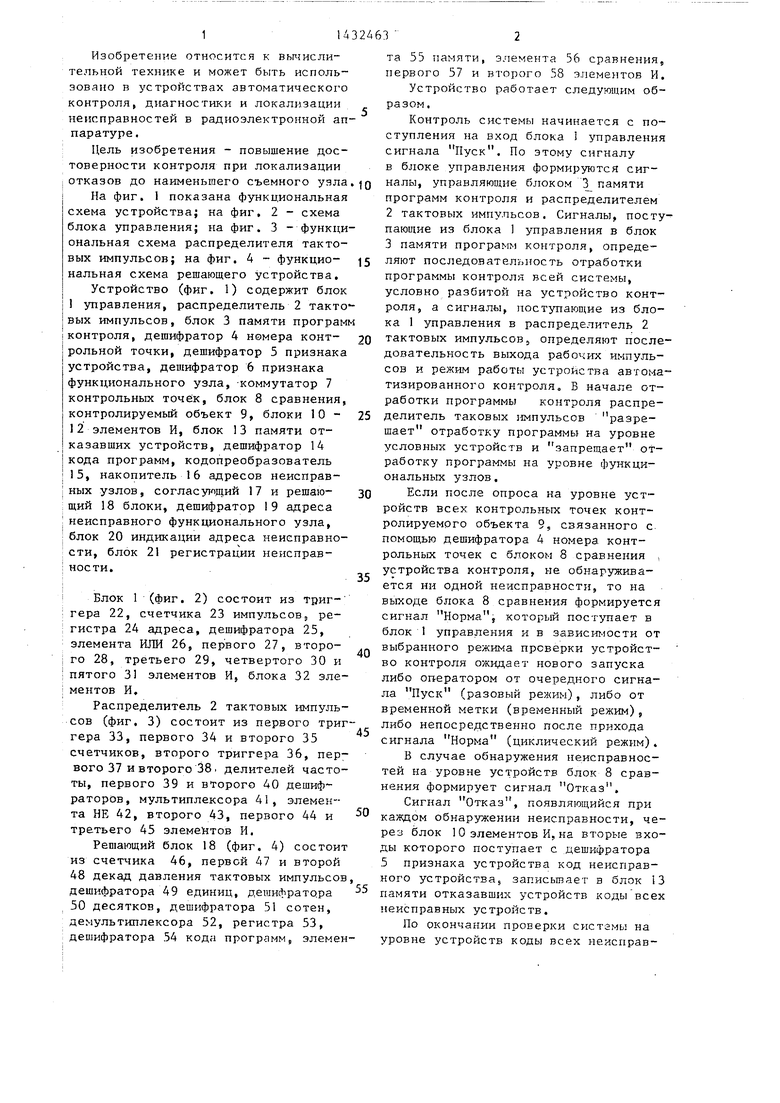

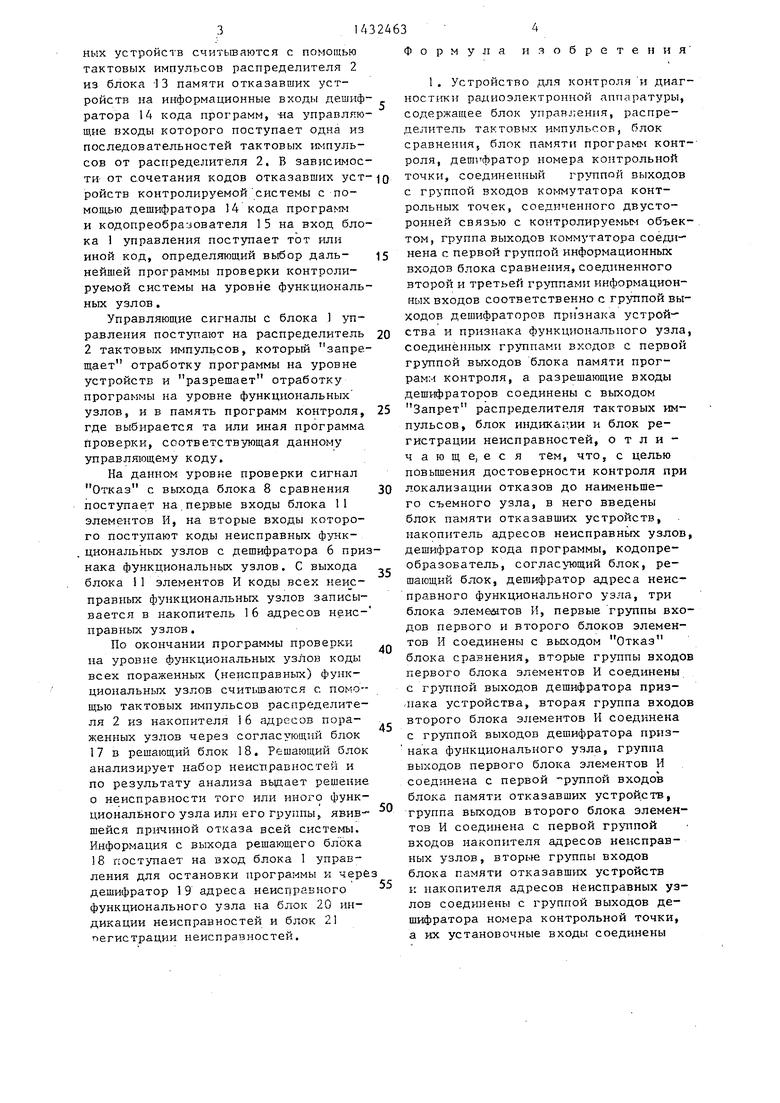

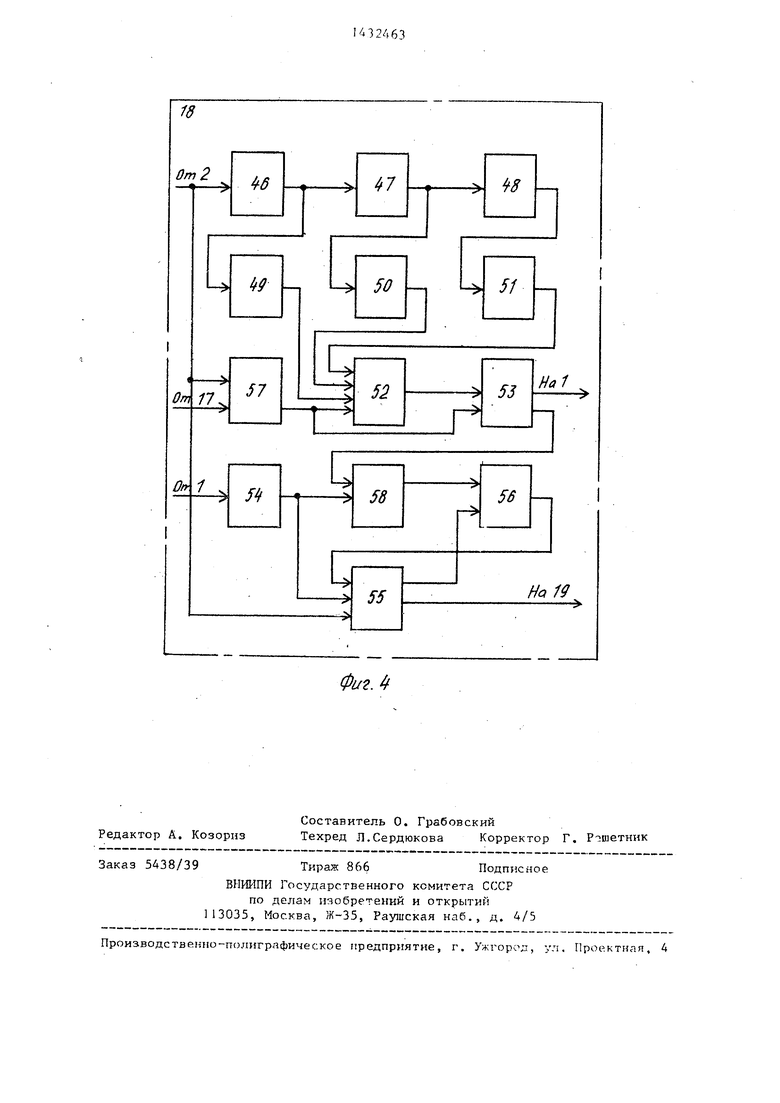

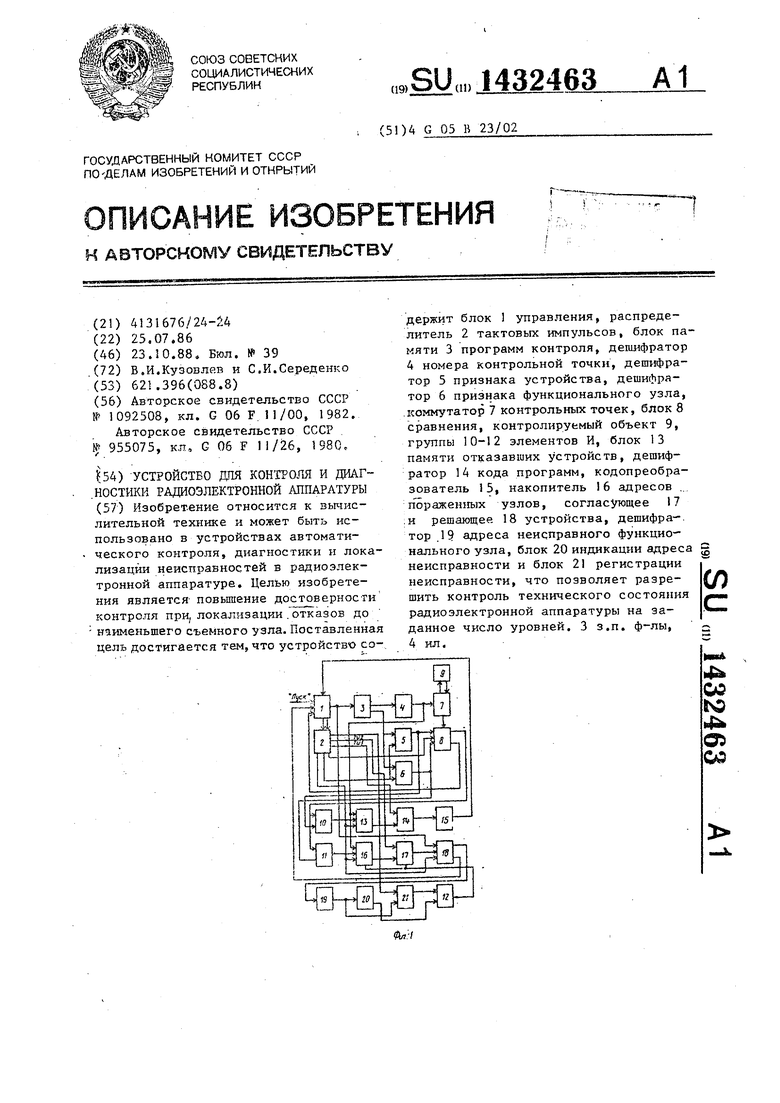

На фиг. 1 показана функциональная схема устройства; на фиг, 2 - схема блока управления; на фиг. 3 - функциональная схема распределителя тактовых импульсов; на фиг. 4 функцио- нальная схема решающего устройства.

Устройство (фиг. 1) содержит блок; 1 управления, распределитель 2 тактовых импульсов, блок 3 памяти nporpai-i контроля, дешифратор 4 номера конт- рольной точки, дешифратор 5 признака устройства, дешифратор 6 признака функционального узла, -коммутатор 7 контрольных точек, блок 8 сравнения, I контролируемый объект 9, блоки 10 - I 12 элементов И, блок 13 памяти от- I казавших устройств, дешифратор 14 I кода программ, кодопреобразователь I15, накопитель 16 адресов неисправ- : ных узлов, согласу}пщий 17 и решаю- ; щий 18 блоки, дешифратор 19 адреса ; неисправного функционального узла, ; блок 20 индикации адреса неисправности, блок 21 регистрации неисправ: НОСТИ.

Блок 1 (фиг. 2) состоит из триг- гера 22, счетчика 23 импульсов, регистра 24 адреса, дешифратора 25, элемента ИЛИ 26, первого 27, второго 28, третьего 29, четвертого 30 и пятого 31 элементов И, блока 32 элементов И,

Распределитель 2 тактовых импульсов (фиг. 3) состоит из первого триггера 33, первого 34 и второго 35 счетчиков, второго триггера 36, первого 37 и второго 38. делителей частоты, первого 39 и второго 40 дешифраторов, мультиплексора 41, элемента НЕ 42, второго 43, первого 44 и третьего 45 элементов И.

Решающий блок 18 (фиг. 4) состоит из счетчика 46, первой 47 и второй 48 декад давления тактовых импульсов дешифратора 49 единиц, дешифратора 50 десятков, дешифратора 51 сотен, демультиплексора 52, регистра 53, дешифратора 54 кода программ, элемен

0

та 55 памяти, элемента 56 сравнения, первого 57 и второго 58 элементов И.

Устройство работает следующим образом.

Контроль системы начинается с поступления на вход блока I управления сигнала Пуск. По этому сигналу в блоке управления формируются сигналы, управляюпл-1е блоком 3 памяти программ контроля и распределителем

2тактовых импульсов. Сигналы, поступающие из блока 1 управления в блок

3памяти программ контроля, определяют последовательность отработки программы контроля всей системы, условно разбитой на устройство контроля, а сигналы, поступающие из блока 1 управления в распределитель 2 тактовых импульсов 5 определяют последовательность выхода рабочих импульсов и peжRм работы устройства автоматизированного контроля о В начале отработки программы контроля распре5 делитель таковых импульсов разрешает отработку программы на уровне условных устройств и запрещает отработку программы на уровне функциональных узлов.

Если после опроса на уровне устройств всех контрольных точек контролируемого объекта 9, связанного с помощью дешифратора 4 номера конт- рольнь Х точек с блоком 8 сравнения , устройства контроля, не обнаруживается ни одной неисправности, то на выходе блока 8 сравнения формируется сигнал Норма, которьй поступает в блок 1 управления и в зависимости от выбранного режима проверки устройство контроля ожидает нового запуска либо оп-ератором от очередного сигнала Пуск (разовый режим), либо от временной метки (временный режим), либо непосредственно после прихода сигнала Норма (циклический режим).

В случае обнаружения неисправностей на уровне устройств блок 8 сравнения формирует сигнал Отказ.

Сигнал Отказ, появляющийся при каждом обнаружении неисправности, через блок 10 элементов И, на вторые входы которого поступает с дешифратора 5 признака устройства код неисправного устройства, записывает в блок 13 памяти отказавших устройств коды всех неисправных устройств.

По окончании проверки сие темь; на уровне устройств коды всех неисправ0

5

0

5

0

5

ных устройств считьшаются с помощью тактовых импульсов распределителя 2 из блока -13 памяти отказавших устройств на информационные входь дешифратора 14 кода программ, «а управляющие входы которого поступает одна из последовательностей тактовых импульсов от распределителя 2. В зависимости от сочетания кодов отказавших устройств контролируемой системы с по- мош,ью дешифратора 14 кода программ и кодопреобразователя 15 на вход блока 1 управления поступает тот или иной код, определяющий выбор дальнейшей программы проверки контролируемой системы на уровне функциональных узлов,

Управляющие сигналы с блока 1 управления поступают на распределитель 2 тактовых импульсов, который запре ш;ает отработку программы на уровне устройств и разрешает отработку программы на уровне функциональных узлов, и в память программ контроля, где выбирается та или иная программа проверки, соответствующая данному управляющему коду,

На данном уровне проверки сигнал Отказ с выхода блока 8 сравнения поступает на.первые входы блока 11 элементов И, на вторые входы которого поступают коды неисправньгх функциональных узлов с дешифратора 6 принака функциональных узлов. С выхода блока 11 элементов И коды всех неисправных функциональных узлов записывается в накопитель 16 адресов нрисправных узлов.

По окончании программы проверки на уровне функциональных узЛов коды всех пораженных (неисправных) функциональных узлов считьшаются с помощью тактовых импульсов распределителя 2 из накопителя 16 адресов пораженных узлов через согласующий блок

17в решающий блок 18. Решающий блок анализирует набор неисправностей и по результату анализа вьщает решение о неисправности того или иного функционального узла или его группы, явившейся причиной отказа всей системы. Информация с выхода решающего блока

18поступает на вход блока 1 управления для остановки программы и чере дешифратор 19 адреса неисправного функционального узла на блок 20 индикации неисправностей и блок 21

пегистрации неисправностей.

0

5

5

0

0

5

0

5

0

5

Формула изобретения

I, Устройство для контроля и диагностики радиоэлектронной аппаратуры, содержащее блок управ. тения, распределитель тактовых импульсов, блок сравнения, блок памяти программ конт- роля, дешифратор номера контрольной точки, соединенный группой выходов с группой входов коммутатора контрольных точек, соединенного двусторонней связью с контролируемьм объектом, группа выходов коммутатора соединена с первой группой информационных входов блока сравнения, соединенного второй и третьей группами информационных входов соответственно с группой выходов дешифраторов признака устройства и признака функционального узла, соединённых группами входов с первой группой выходов блока памяти программ контроля, а разрешающие входы дешифраторов соединены с выходом Запрет распределителя тактовых импульсов, блок индикаи.ии н блок регистрации неисправностей, о т л и - ч а ю щ е, е с я тем, что, с целью повьш1ения достоверности контроля при локализации отказов до наименьшего съемного узла, в него введены блок памяти отказавших устройств, накопитель адресов неисправньгх узлов, дешифратор кода программы, кодопреобразователь, согласующий блок, решающий блок, дешифратор адреса неисправного функционального узла, три блока элементов И, первые группы входов первого и второго блоков элементов И соединены с выходом Отказ блока сравнения, вторые группы входов первого блока элементов И соединены с группой выходов дешифратора приз- .пака устройства, вторая группа входов второго блока элементов И соединена с группой выходов дешифратора признака функционального узла, группа выходов первого блока элементов И соединена с первой руппой входов блока памяти отказавших устройств, группа выходов второго блока элементов И соединена с первой группой входов накопителя адресов неисправных узлов, вторые группы входов блока памяти отказавших устройств и накопителя адресов неисправных узлов соединены с группой выходов дешифратора номера контрольной точки, а их установочные входы соединены

с первым управляющим входом решающего блока и выходом распределителя тактовых импульсов, соединенного вторым выходом с управляющим входом дешифратора кода программ, подключенного группой входов к группе выходов блока памяти отказавших устройств, группа выходов дешифратора кода программ соединена с группой входов кодопреобразователя, соединенного группой выходов с первой, группой входов блока управления, подключенного вторым входом к первому выходу решающего блока, соединен- кого группой выходов с группой входов дешифратора адреса неисправного функдионального узла, связанного группой выходов с группой входов блока индикации адреса неисправности и блока регистрации неисправностей, группа информационных входов решающего блока соединена с группой выходов согласующего устройства, группа выходов накопителя адресов неисправных узлов соединена с группо информационных входов согласующего устройства, соединенного управляющим входом с третьим выходом распределителя тактовых импульсов, подключенного четвертым выходом к второй группе входов блока регистрации неисправностей, соединенного выходом с входом третьего блока элементов И, подключенного второй группой входов к группе выходов блока индикации адреса неисправности, а выходом - к синхронизирующим входам накопителя адресов неисправных узлов и согласующего блока, второй управляющий вход решающего блока соединен с управляющим входом блока памяти и с .первым выходом блока управления, связанного вторьм и третьим выходами с первым и вторым управляющими входами распределителя тактовых кмиулъсов, а первым входом - с выходом Норма блока сравнения, соединенного управляющим входом с пятым выходом распределителя тактовых импульсов, вторая группа выходов блока памяти программ контроля соединена с группой входов дешифратора номера контрольной точки, третий вход блока сравнения является входом запуска устройства, а четвертый, пятый, шестой и седьмой входь; блока управления являются установочными входами устройства.

0

g 5 5

0

5

0

5

0

2.Устройство по п 1, отличающееся тем, что блок управления включает триггер, счетчик импульсов, регистр адреса, дешифратор, элемент ИЛИ, блок элементов И и пять элементов И, выходы первого, второго и третьего элементов И соединены с первым, вторым, третьим входами элемента ИЛИ, соединенного выходом с единичным входом триггера, нулевой вход триггера является вторым входом блока и подключен к четвертому элементу И, связанному выходом с первым входом третьего элемента И и первым входом пятого элемента И, соединенного вторым входом с прямым выходом триггера, подключенного инверсным выходом к управляющему входу регистра и первому входу первого элемента И, выход пятого элемента И соединен с первым входом блока элементов И и счетным входом счетчика, соединенного выходом с информационным входом регистра, связанного

с установочными входами, а группой выходов - с выходами блока элементов И, с входом дешифратора, выход которого является первым выходом блока, выход четвертого элемента И является вторым выходом блока, выход регистра является третьим выходом блока, группа входов блока элементов И является группой входов блока, первый вход второго элемента И и второй вход третьего элемента И являются первым входом блока, второй вход первого элемента И является третьиз- входом блока, второй и третий входы второго элемента И являются четвертым и пятым входами блока, третий вход третьего элемента И является шестым входом блока, а второй вход четвертого .элемента И является седьмым входом блока,

3.Устройство по п. 1, отличающееся тем, что распределитель тактовых импульсов включает два триггера, два счетчика,, два делителя частоты, два дешифратора, мультиплексор, элемент НЕ и группу элементов И, единичный выход первого триггера соединен с входом элемента НЕ, первым входом первого элемента И и управляющим входом мультиплексора, соединенного первым информационным входом с выходом первого делителя частоты, подключенного входом к выходу второго делителя частоты и вто7

рому информационному входу мультиплексора, выход первого счетчика содинен с вхоДом первого дешифратора, соединенного выходом с вторым входом первого элемента И и первым входом второго элемента И, соединенного вторым входом с выходом элемента НЕ, вход первого триггера соединен с входом второго триггера, соединенного выходом со счетным входом второго счетчика, подключенного уп- равляюр1им входом к входу второго д лгтеля частоты, к счетному входу первого счетчика и первому входу третьего элемента И, выход второго счетчика соединен с входом второго дешифратора, соединенного выходом с вторым входом третьего элемента И и установочным входом второго счетчика, входы второго и первого триггеров являются соответственно пер- Bbw и вторым управляющими входами распределителя, выход первого триггера является выходом Запрет распределителя, выходы мультиплексора второго, первого и третьего элементов И и первого дешифратора являются соответственно первым, вторым, третьим, четвертым и пятым выходами распределителя.

4. Устройство по п. 1, отличающееся тем, что решающий блок включает счетчик, две декады деления тактовых импульсов, дешифратор единиц, дешифратор десятков, дешифратор сотен, демультиплексор, регистр, дешифратор кода программ, элемент памяти, элемент сравнения, два элемента И, счетный вход счетчи432463

5

0

5

0

5

ка соединен с входом первого элемента И, с управляющим входом эле-, мента памяти и является первым управляющим входом блока, выход счетчика подключен к входу дешифратора единиц и к входу первой декады деления тактовых импульсов, соединенной выходом с входом дешифратора десятков и входом второй декады деления тактовых импульсов, подключенным выходом к входу дешифратора сотен, соединенного выходом с первым информационным входом демультиплексора, соединенного вторым и третьим информационными входами соответственно с выходами дешифраторов десятков и единиц, управляющий вход демультиплексора подключен к выходу первого элемента И и управляющему входу регистра, соединенного информационным входом с выходом демультиплексора а выходом младшего разряда - с входом второго элемента И, связанного группой входов-с выходом дешифратора кода и информационным входом элемента памяти, а выходом - с первым информационным входом элемента сравнения, подключенного вторым информационным входом к первому информационному выходу элемента памяти, а, выходом - к синхронизирующему входу элемента памяти, группа входов первого элемента И является группой информационньк входов блока,вход дешифратора кода является вторым управляющим входом блока, второй информационный выход регистра является выходом блока, второй информационный выход элемента памяти является группой выходов блока.

Писи

г7

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Распределитель импульсов | 1986 |

|

SU1405105A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах автоматического контроля, диагностики и локализации неисправностей в радиоэлектронной аппаратуре. Целью изобретения является повышение достоверности контроля при, локализации.отказов до наименьшего съемного узла. Поставленная цель достигается тем, что устройство со-. держит блок I управления, распределитель 2 тактовых импульсов, блок памяти 3 программ контроля, дешифратор 4 номера контрольной точки, дешифратор 5 признака устройства, дешифратор 6 признака функционального узла, .коммутатор 7 контрольных точек, блок 8 сравнения, контролируемый объект 9, группы 10-12 элементов И, блок 1 3 памяти отказавших устройств, дешифратор 14 кода программ, кодопреобразователь 15, накопитель 16 адресов пораженных узлов, согласующее 17 ;и решающее 18 устройства, дешифра-. тор .19 адреса неисправного функционального узла, блок 20 индикации адреса g неисправности и блок 21 регистрации неисправности, что позволяет разрешить контроль технического состояния радиоэлектронной аппаратуры на заданное число уровней. 3 з.п. ф-лы, 4 ил. (Л с

tftneiMi

28

6

OrS

ifuWMM

n

2ff

CU

S3

21

0m rS

}2

j;

Ha2

Ha J и 18

Ha 2

rfe

Фи2Л

| Устройство для контроля и локализации неисправностей логических схем | 1982 |

|

SU1092508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для диагностирования цифровых систем | 1980 |

|

SU955075A1 |

Авторы

Даты

1988-10-23—Публикация

1986-07-25—Подача