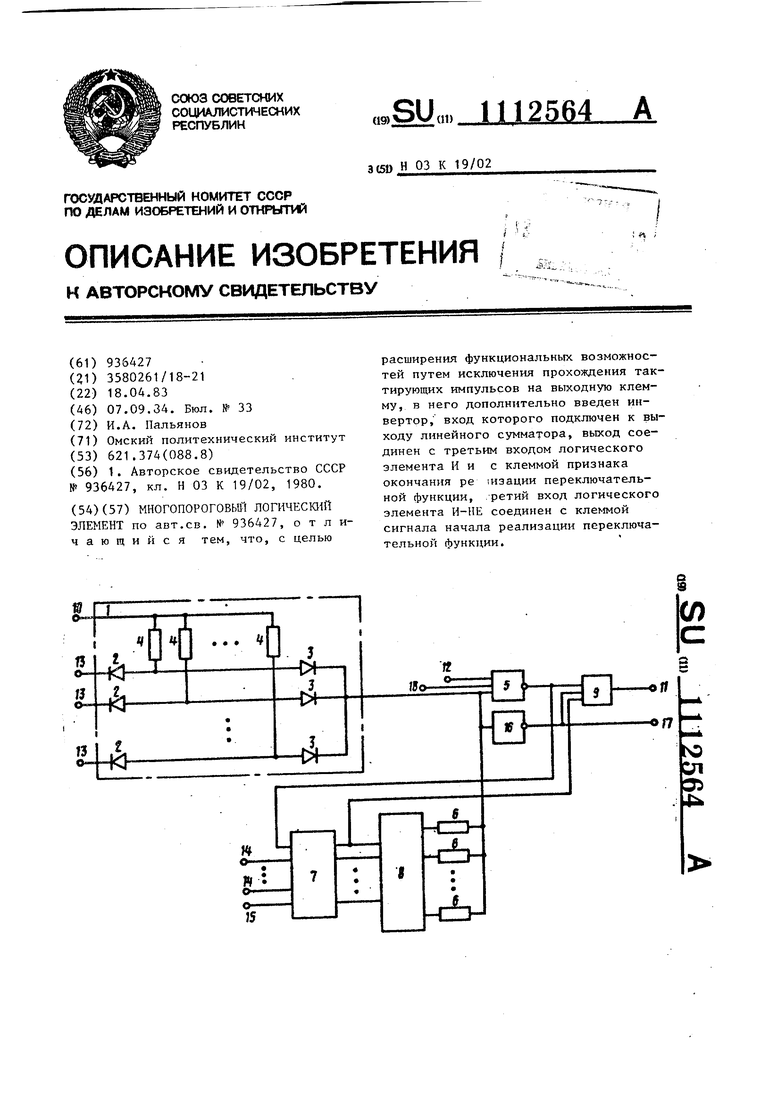

Изобретение относится к автоматике и вычислительной технике, в част ности к элементам пороговой логики По основному авт.св. W 936427 известен многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенной через разделительные диоды к первому входу логического элемента И-НЕ, которьй образует дискриминатор, и ре зисторы, определяющие пороги срабатывания, В элемент введены суммирующий счетчик, соединенный с дешифратором, и логический элемент И, выход которого соединен с выходной Клеммой многопорогового логического элемента первый вход элемента И соединен с вькодом логического элемента И-НЕ и со счетным входом суммирующего счетчика, второй вход подключен к выходу младшего разряда суммирующего счетчи ка, выходы дешифратора через резисторы, определяющие пороги срабатывания, подключены к первому входу логи ческого элемента И-НЕ, второй вход которого соединен с клеммой тактирую щих импульсов Щ. Недостатком известного многопорогового логического элемента является то, что тактирующие импульсы поступают на выходную клемму многопорогового логического элемента в моменты времени, когда на выходе младшего разряда суммирующего счетчика присут ствует сигнал логической единицыо Кроме того, подобньй элемент может быть использован только в-синхронных схемах, в которых при наличии последовательно соединенных многопороговых логических элементов каждый последующий многопороговый логический элемент должен начинать свою работу лишь после того, как в предыдущем многопороговом логическом элементе с наибольшим числом порогов срабатывания на клемму тактирующих импульсов поступает М импульсов, где М число порогов срабатывания элемента. Это сужает функциональные возможности, исключает возможность применения подобного многопорогового логическог элемента в схемах, где к его выходу должны подключаться другие логические устройства, содержащие элементы памяти, а также в асинхронных схемах цифровых устройств. Цель, изобретения - расширение функциональных возможностей путем исключения прохождения тактирующих импульсов на выходную клемму, т.е. обеспечение возможности использования многопорогового логического элемента в асинхронных схемах, а также в схемах, где к его выходу подключаются другие логические устройства, содержащие элементы памяти. Поставленная цель достигается тем, что в многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, резисторной матрицы и разделительных диодов, выход линейного сумматора подключен к первому входу логического элемента , образующего дискриминатор, весовые резисторы, счетчик, дешифратор и элемент И, выход которого соединен с выходной клеммой многопорогового логического элемента, первый вход элемента И соединен с выходом логического элемента И-НЕ и со счетным входом суммирующего счетчика, второй вход подключен к выходу младшего разряда суммирующего счетчика, выходы дешифратора через весовые резисторы подключены к первому входу логического элемента И-НЕ, второй вход которого соединен с клеммой тактирующих импульсов, выходы суммирующего счетчика соединены с соответствую цими входами дешифратора, дополнительно введен инвертор, вход которого подключен к выходу линейного сут-1матора, выход соединен с. третьим входом логического элемента И и с клеммой признака окончания реализации переключательной функции, третий вход логического элемента И-НЕ соединен с клеммой сигнала начала реализации переключательной функции. На чертеже приведена структурная схема многопорогового логического элемента. Многопороговый логический элемент содержит линейный сумматор 1, состоящий из входных диодов 2, разделительных диодов 3 и весовых резисторов 4, образутащих резистивную матрицу, дискри1-1инатор на логическом элементе И-НЕ 5, весовые резисторы 6, определяющие порог срабатывания дискриминатора, суммирующий счетчик 7, дешифратор 8 и трехвходовой логический элемент И 9, Каждая пара диодов 2 и 3 линейного cy ;лaтopa в точках, объединяющих их анодЫэ через резисторы А, определяющие вес входов, подключена К положительному полюсу источника 10 питания. Катоды диодов 3 объединены и подсоединены к первому входу логического элемента И-НЕ 5 и через резисторы 6 - к выходам дешифратора 8. Входы дешифратора 8 соединены с выходами суммирующего счетчика 7, младший разряд которого соединен еще с одним входом логического элеме та И 9. Второй вход элемента И 9 сое динен с выходом логического элемента И-НЕ 5 и со счетным входом суммирующего счетчика 7. Выход элемента И 9 подключен к выходной клемме 11 многопорогового логического элемента. Второй вход логического элемента И-НЕ 5 соединен с клеммой 12 тактирующих импульсов. На входные клеммы 13 линейного сумматора 1 поступают входные переменные многопорогового логического элемента. Входы 14 являю ся информационными входами суммирующего счетчика 7. Вход 15 является входом предварительной записи информации в двоичный счетчик. Вход инвертора 16 подключен к выходу линейного сумматора 1, выход - к треть ему входу логического элемента И 9 и к клемме 17 сигнала окончания реализации переключательной функции. Третий вход элемента Н-НЕ 5 подключе к клемме 18 сигнала начала реализации переключательной функции. Источник питания не показан. Многопороговый логический элемент работает следующим образом. Перед подачей входных сигналов в клеммы 13 линейного сумматора 1, в суммирующий счетчик 7 производится запись информации путем подачи кола в клеммы 14 и импульса записи на вход 15. Двоичньш код, записываемый в суммируюпшй счетчик 7, определяет количество порогов у многопорогового логического элемента. Положим, что а счетчик 7 записан код 00...0. Это значит, что число порогов многопорогового логического элемента равно числу резисторов 6. Двоичный код на выходе суммирующего счетчика 7 oпpeделяет какой из резисторов 6 подключен через соответствующий выход дешифратора 8 к отрицательному полюсу источника питания. Двоичный код 00...О на выходах дешифратора 8 обус лавливает подключение к отрицательно му -полюсу источника питания резистора 6, определяющего порог срабатьшания Т . Код 00...01 вызывает подключение резистора 6, соответствующего порогу срабатывания , После занесения информации в суммирующий счетчик 7 в клеммы 13 поступают входные сигналы, которые в произвольных комбинациях запирают диоды 2. Сигналы, поступающие в клеммы 13, в общем случае, могут сниматься с выходов подобных многопороговых логических элементов и приходить в различные моменты времени, в зависимости от момента окончания реализации переключательной функции соответствующим элементом. Сигналы признаков окончания реализации переключательных функций многопороговыми логическими элементами, связанными с рассматриваемым элементом, поступают в клемму 18. Как только во всех многопороговых логических элементах, связанных с рассматриваемым элементом, переключательная функция реализована, то на клемме 18, связанной с входом элемента И-НЕ 5, появляется сигнал логической единицы. Если на клеммах 13 линейного сумматора 1 присутствует комбинация входных переменных, для которой. X,CJ:.tT, то ток от. положительного полюса источника 10 питания через резисторы 4 и соответствующие входному коду открытые диоды 3 переключается в цепь резистора 6, соответствующего порогу Т, вызывая на нем падение напряжения, недостаточное для срабатывания дискриминатора на логическом элементе И-НЕ 5. Тактовые импульсы, подаваемые в клемму 12, в этом случае не проходят на счетный вход суммируюшего счетчика 7, состояние которого остается исходным 00...0. Поскольку на выходе младшего разрядЬ суммирующего счетчика 7 присутствует уровень логического нуля,то и на клемме 11 многопорогового логического элемента также присутствует уровень логического нуля. На клемме 17 сигнала окончания реализации переключательной функции присутствует сигнал логической единицы, так как на входе инвертора 16 - низкий уровень напряжения. Пусть теперь на клеммы 13 линейного сумматора 1 подана комбинация входных переменных, для которой x CO;iT2. В этом случае ток от положительного полюса источника 10 питания через резисторы 4 и открь ,тые диоды 3 переключается в цепь резисторов 6, соответствующего порогу Tjj, вызывая на нем падение напряжения, достаточное для срабатывания дискриминатора на логическом элементе И-НЕ 5. На выходе инвертора 16 в этом случае присутствует уровень напряжения логического нуля, запрещающий прохождение тактовых импульсо на клемму 11 многопорогового логического элемента через элемент И 9. Однако тактовые импульсы, подаваемые в клемму 12, проходят на выход элемента 5 и поступают на счетный вход суммирующего счетчика 7. При этом состояние суммирующего счетчика 7 изменяется с 00...О на 00...01, вызывая, тем самым, изменение порога срабатывания дискриминатора за счет подключения к отрицательному полюсу источника питания резистора 6, определяющего порог срабатывания Т. Поскольку для поступившей на клемму 13 и комбинации входных сигналов 21 X, то потенциала от протекания тока через резистор 6, соответствующий порогу , становится недостаточно для срабатывания дискриминатора на логическом элементе И-НЕ 5 и инверт ра 16. Следовательно поступление тактирующих импульсов на вход суммирующего счетчика 7 прекращается, на клемме 17 сигнала окончания реализации логической функции появляется уровень напряжения логической единицы. На клемме 11 многопорогового логического элемента, в этом случае формируется уровень напряжения логической единицы, так как на выходе младщего разряда счетчика 7, выходе элемента И-НЕ 5 и инверторе 16 присутствуют уровни напряжения логической единицы. Аналогичным образом происходит работа многопорогового логического элемента и при других комбинациях сигналов на клеммах 13 линейного сумматора 1. При этом тактирующие сигналы проходят на счетный вход сум мирующего счетчика 7 до тех пор, п пока величина 21 X, СО превосходит или равна порогу срабатывания, определяемому кодом, Г1аходящимся на суммирующем счетчике 7. И на выходе инвертора 16, в этих случаях, присутствует уровень напряжения логического нуля, запрещающий прохождение тактовых импульсов на выходную клемму 11 многопорогового логического элемента. На клемме 17 сигнала окончания реализации переключательной функции присутствует сигнал логичес пкого нуля. Как только величина 51 x;|CJ становится меньше порога срабатывания, то уровень напряжения на связанных с линейным сигналом 1 входах элемента И-НЕ 5 и инвертора 16 становится недостаточньм для их срабатывания . На выходах элемента И-НЕ 5 инвертора 16 и клемме.17 устанавливаются уровни напряжения логической единицы. п Если величина 21 Wj- больше четного порога и мекьше нечетного, то после прекращения поступления тактирующих импульсов на счетный вход суммирующего счетчика 7, младший разряд последнего устанавливается в нулевое состояние. При этом на выходе многопорогового логического элемента формируется уровень логического нуля, п Если величина Z1 Х у поступившая на входы линейного сумматора 1, больше нечетного порога, но меньше четного, то после остановки суммиругопгего счетчика 7 в его младшем разряде находится единица, которая и определяет единичное значение функции на выходе многопорогового логического элемента. Если перед поступлением входных сигналов на суммирующем счетчике 7 установлен код, отличный от кода 00...О, то многопороговый логический элемент реализует другую переключательную функцию. При этом наименьший порог срабатывания дискриминатора определяется начальным кодом, установленным на счетчике 7. Указанные изменения в структуре многопорогового логического элемента позволяют расширить его функциональные возможности за счет обеспечения

711125648

возможности его применения в асннх- элемента должны подключаться другие ронных схемах, а также в схемах, где логические устройства, содержащие к выходу многопорогового логического элементы памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1980 |

|

SU936427A1 |

| Многопороговый логический элемент | 1984 |

|

SU1262722A1 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

МНОГОПОРОГОВЬШ ЛОГИЧЕСКИП ЭЛЕМЕНТ по авт.св. № 936427, отличающийся тем, что, с целью ; п / расширения функциональных возможностей путем исключения прохождения тактирующих импульсов на выходную клемму, в него дополнительно введен инвертор, вход которого подключен к выходу линейного сумматора, выход соединен с третьим входом логического элемента И и с клеммой признака окончания ре 1изации переключательной функции, ретий вход логического элемента И-ПЕ соединен с клеммой сигнала начала реализации переключательной функции.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многопороговый логический элемент | 1980 |

|

SU936427A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1983-04-18—Подача