54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1983 |

|

SU1112564A2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент | 1984 |

|

SU1262722A1 |

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

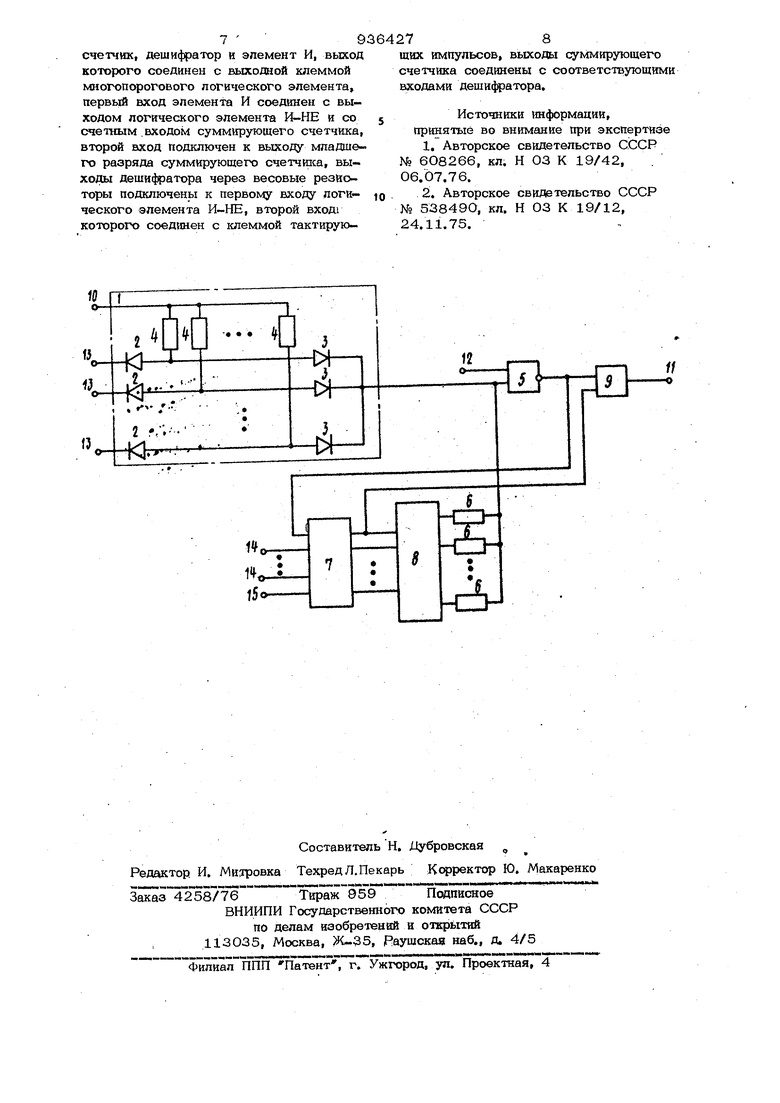

Изобретение относится к автоматике И вычислительной технике, в частности к элементам пороговой логики. Известен многопороговый логический элемент, содержащий линейный сумматор и последовательно включенньй с ним дискриминатор 1 . Недостатком известного многопорогово го логического элемента является низкая тезснологичность из-за наличия цепи последовательно соединенных резисторов, определяющих пороги срабатывания, многопорогового дискриминатора. В процессе изготовления к этим резисторакг предъявлявотся повышенные требования по трчноо ти, поскольку отклонение от номинала хотя бы одного рези:стора приводит к изме нению порогов срабатывания логических элементов многопорогового дискриминатора. Особенно высоки требовани я к точности изготовления резисторов мйогопорогового дискриминатора при большом числе порогов многопорогового логического элемента. Наиболее близким по технической сущности к предложенному является мно гопоротовый ло1М1ческий элемент, содержащий линейный сумматор, состоящий иа входных диодов к резасторной матрицы, подключенный через разделительные диоды к первому входу логического эле мента И-НЕ, образующего Л11скриминатор И резисторы, опредетаощйе пороги срабатывания 2 . Недостатком известного устройства является Низкая технологичность и точность при больщом числе порогов срабатывания. На точность данного устройства существенное влияние также оказывает разброс входньк характеристик логических элементов И-НЕ, входящих в много пороговый дискриминатор, особевшо npt являющийся при изменение темпера1урных условий работы. Кроме того, известное устройство характеривуется низкими функциональными возможностями, не позволяющими реализовать на нем более одной микропороговой функции. 393 Цель изобретения - расширение функциональных возможностей (реализация большего числа многопороговых функцсй), повьпление технологичности и точности при большом числе порогов. Поставленная цель достигается тем, что в многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и резисторь ной матрицы и разделительных диодов, выход ли}1ейного сумматора подключен к первому входу логического элемента . И-НЕ, образующего дискриминатор, и весовые резисторы, дополнительно введены суммирующий счетчик, дешифратор и эле- мент И, выход которого соединен с выход ной клеммой многопорогового логического элемента, первый вход элемента И соединен с выходом логического элемента ИЛЕ и со счетаым входом суммирующе- 20 го счетчика, второй вход подключен к выходу младшего разряда суммирующего счет11Ика, выходы дешифратора через весовые резисторы подключены к первому входу логического элемента И-НЕ, второй ВХОД которого соединен с клеммой тактирующих импульсов, выходы суммирующего счетчика соединены с соответствующими входами дешифратора. U На чертеже представлена стр турная схема многопорбгового логического элемента. . Многопороговый логический элемент содержит линейный сумматор 1, состоящи из входных диодов 2, разделительных дйодов 3, и резисторов 4, образующих ре- зисторную матр{щу, дискрим шатор на логическом элементе И-НЕ S, весовые резисторы 6, определяющие порог срабатывания дискриминатора, суммирующий счег чик 7, дешифратор 8 и элемент И 9. Каждая пара диодов 2 и 3 линейного сум матора в точках, объединяющих их аноды через резисторы 4, определяющие вес входов, подключена к положительному полюсу источника питания 10. Катоды диодов 3 объединены и подсоединены к первому входу логического элемента И-НЕ 5 и через резисторы 6 к выходам дешифгратора 8. Вхоаы дешифратора 8 соеД{шены с выходами суммирующего счерчика 7, младший разряд которсяго соединен еще и с входом логического элемента И 9, Второй вход последнего соединен с выходом логического элемента И-НЕ 5 и со счетным входом суммирующего счетчика 7. Выход элемента И 9 подключен к выходной клемме мно7гопорогового логического элемента 11. Второй вход логического элемента И-НЕ 5 соединен с клеммой 12 тактирующих импульсов. На входы 13 линейного сумматора 1 поступают входные переменные многопорогового логического элемента. Входы 14 являются информационными входами суммирующего счетчика 7. Вход 15 является входом предварительной записи информации в двоичный счетчик. Иоточник питания на чертеже не показан. Многопороговый логический элемент работает следующим образом. Перед подачей входных сигналов в клеммы 13 линейного сумматора 1 в суммирующий счетчик 7 производится запись информации путем подачи кода в клеммы 14 и импульса записи на вход 15, Двоичньш код, записываемый в суммиРУ ЩИй счетчик 7, определяет количество порогов у многопорогового логического элемента. Не теряя общности рассуждений положим, что в счетчик 7 записан коц О О... О, значит, что число пороговмногопорогового логического элемента равно числу резисторов 6, Двоичный код на выходе суммирующего счетчика 7 определяет какой нз pe3ECTt ров 6 подключен через соответствующий в Еяход дешифратора 8 к отрицательному Полюсу источника питания. Двоичный код О О... О на входах дешифратора 8 обуславливает подключение к отрицательному полюсу источника питания резистора 6, определяющего порог срабатывания код О О... 01 вызывает подключение резистора 6, соответствующего порогу срабатывания Т... После занесения информации в суммирующий счетчик 7, в клеммы 13 поступают входные сигналы, которые в произвольных комбинациях запирают днощл. 2. Одновременно с поступлением входных сигналов в клемму 12 поступают тактовые импульсы. Если на входы 13 линейного сумматора 1 поступает комбинация входных переменных, для котоИрой21 Ч. О) ток от положительного Полюса источника питания 10 через резисторы 4 и сбответствующие входному коду открытые диоды 3 переключаются в цепь резистора 6, соответствующего порогу Т, вызывая на нем падение напряжения, недостаточное для срабатывания дискриминатора на логическом элементе И-НЕ 5. Тактовые импульсы, подаваемые в клемму 12, в этом случае не проходят

на счетный вход суммирующего счетчика 7, состояние которого остается искодиым О О ... О. Поскольку на выходе младшего разряда суммирующего счетчика 7 присутствует уровень логического нуля, то и на выходе. 11 многопорогового ло гического элемента также присутствует уровень логического нуля.

Пусть теперь на входы 13 линейного сумматора 1 подана комбинация входпеременных, для которойТ С .-Шных

ir-l I

Тп ;. В ЭТОМ случае ток от положительнго полюса источника питания 10 через резисторы 4 и открытые диоды 3 пере ключается в цепь резистора 6, соответствующего п орогу Т, вызывая на нем падение напряжения, достаточное для срабатывания дискриминатора на логическом элементе И-НЕ 5, Тактовые импульсы, подаваемые в клемму 12 проходят на выход элемента 5 и поступают на счетный вход суммирующего счетчика 7. При этом состояние суммирующего счетчика 7 изменяется с О О... О на О О... О1, вызывая тем самым изменени порога срабатьшания дискриминатора за счет подключения к отрицательному аолюсу источника питания резистора 6, определяющего порог срабатывания TQ. Поокольку дня поступившей на входы 13 комI .

бинации входных сигналов2Х-(«). „,

in

потенциала от протекания тока через резистор 6, соответствующий порогу Тп, становится недостаточно для срабатывания дискриминатора на логическом элементе 7 и поступление тактирующвос импульсов на вход суммирующего счетчика 7 прекращается. На выходе 11 многопорогового логического элемента, в этом случае, формируется уровень напряжения логической единицы, так как на выходе младшего разряда счетчика 7 и выходе элемента И-НЕ 5 присутствуют уровни напряжения логической единвды.

Аналогичным образом происходит работа многопорогового логического элемента и при других комбинациях сигналов на входах 13 линейного сумматора 1. При этом тактирующие сигналы проходят на счетный вход суммирующего счетчика 7.

п до тех пор, пока величина S преis.- .

восходит или равна порогу срабатывания, определяемому кодом, находящемся на . суммирующем счетчике 7. Если величина

гД 2JX.-tt). большего четного порога к,

1-1

меньшего нечетного, то после npeiqiameния поступления тактирующих илшульсов на счетный вход суммирующего счетчика 7, младщий разряд последнего устанавливается в нулевое состояние. Прк этом на выходе многоиорогового логпческот о элемента 11 формируется уровень логиIи

ческого нуля. Если величина Sx.-U). ,

1,

поступившая на входы линейного cj viMaToра 1 больщего нечетного порога, но меньше четного, то после остановки суммирующего счетчика 7 в его младяем разряде находится единица, которая и определяет единичное значение функции на выходе 11 лдаогоиорогового логического элемента Если поступлением входных сиг. налов на суммирующем счетчике 7 установлен код, отличный от кода О О... О, то кшогопороговый логический элемент реализует другую переключательную функцгао. При этом наименьший порог срабатывания дискриминатора определяется начашьным кодом, установленным на счетчике.

Указанные изменения в структуре многопорогового логического элемента позволяют повысить его технологичность и точность за счет исключения из его схемы цепи последовательно включенньтх резисторов, определяющих пороги срабатывания дискриминатора, а также за счет того, что в дискриминаторе используется только одий логический элемент И-НЕ. Кроме того, расширяются функциональные возможности предложенного элемента, поскольку он позволяет реализовать неоколько различньЕХ переключательных функций, число которых равно числу порогов в многопороговом логическом элементе.

Формула изобретения

Многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, резисторной Matw рицы и разделительных диодов, выход линейного сумматора подключен к первому входу логического элемента И-НЕ, обра- зующего дискриминатор, и весовые резисторы, отличающийся тем, что, с целью расширения функционалы ых возможностей, повышения технологичнооти и точности при большом числе порогов, он дополнительно содержит суммирующий

счетчик, дешифратор и элемент И, выход которого соединен с выходной клеммой многопорогового логического элемента, первый вход элемента И соединен с выходом логического элемента И-НЕ и со счетным .входом суммирующего счетчика, второй вход подключен к выходу младшего разряда суммирующего счетчшса, выходы дешифратора через весовые резисторы подключены к первому входу логического элемента И-НЕ, второй входг которого соединен с клеммой тактирующих импульсов, выходы суммирующего счетчика соединены с соответствующими Ежодами дешифратора.

Источники жформадии, принятые во внимание при экспертизе

Авторы

Даты

1982-06-15—Публикация

1980-10-23—Подача