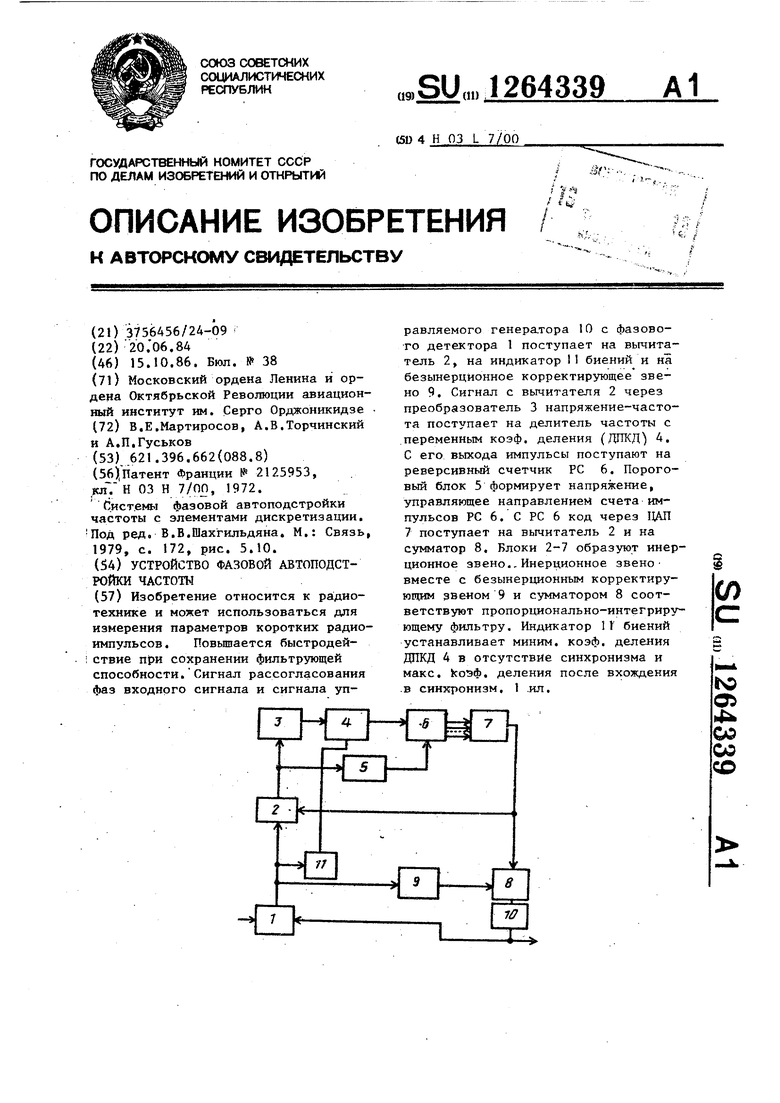

Изобретение относится к радиотехнике и может быть использовано для измерения параметров коротких радиоимпульсов. Цель изобретения - повьппение быстродействия устройства при сохранении фильтрующей способности. На чертеже представлена структур ная электрическая схема устройства фазовой автоподстройки частоты, .Устройство фазовой автоподстройки частотЬ) содержит фазовый детектор 1, вьгчитатель 2, преобразователь 3 напряжение-частота, делител 4 частоты с переменным коэффициенто деления (/ЩКД), пороговый блок 5, реверсивный счетчик 6, цифроаналого вый преобразователь 7, сумматор 8, безынерционное корректирующее звено 9, генератор 10, управляемый напряжением, и индикатор 11 биений. Устройство работает следующим об разом, При подаче на входы фазового дете тора 1 входного сигнала и сигнала генератора 10, управляемого напряже нием, сигнал о рассогласовании фаз поступает на вход вычитателя 2 и с выхода последнего на преобразовател 3 напряжение-частота, Предположим, что частота следования импульсов преобразователя 3 пропорциональна модулю входного напряжения, т,е. Ul.-)KnH. /U8.n«.( + )/. Тогда частота следования импульсов с выхода ДПКД 4 f(4- --ГИЧ-ипм(.+ ; ig А U 1 л - коэффициент деления.ДПКД 4 с переменным коэффициентом .деления. При этом пороговый блок 5 опреде ляет знак и (+) и в соответствии Вхпмч Vс этим, управляет направлением счета импульсов реверсивным счетчиком 6, При большой разрядности цифроаналогового преобразователя 7 QvJujCtn „ пнч и (+) U.n-(t напряжение на выходе цифроаналогового образователя 7; - дискрет его выходного напряжения. Следовательно блоки 3-7 в совоку ности являются генератором с постоянной времени -г NjfrUK Ifу чпп С помощью вычитателя 2 генератор хвачен цепью отрицательной обратой связи, т,е, преобразуется в инерионное звено, а благодаря включеию безынерционного корректирующего вена 9 с коэффициентом передачи К асть схемы с входа вычитателя 2 до ыхода сумматора 8 соответствует ропорционально-интегрирующему фильру (звену с запаздыванием по фазе) передаточной функцией 1 п;к W(P) (HK) де - оператор дифференцирования, В отсутствие синхронизма индикаор 11 биений вьщает на управляющий ход ДПКД 4 логический сигнал, соотетствующий минимальному коэффицинту деления N , , при этом ы 1 j .aчI 1 v где Яу(1«-К) 5„г, - полоса удержания предлагаемого устройства;S и . - соответственно крутизна фазового детектора 1 и. крутизна генератора 10, управляемого напряжением, В этом случае устройство по своим параметрам эквивалентно бесфильтровой схеме, имеющей малое время вхождения в синхронизм, т,е, высокое быстродействие. После вхождения в синхронизм напряжение биений на выходе фазового детектора I пропадает, индикатор 1 1 биений вьадает сигнал, соответствующий максимальному коэффициенту деления N ДПКД 4, постоянная времени возрастает в N yN, раз и предлагаемое устройство становится по своим параметрам системой фазовой автоподстройкй частоты с пропорционально-интегрирующим фильтром и имеет малую шумовую полосу. Таким образом, изобретение обеспечивает повышение быстродействия предлагаемого устройства при сохра-. нении фильтрующей способности, т.е. малой шумовой полосы в режиме син хронизма. Формула изобретени Устройство фазовой автоподстройки частоты, содержащее последовательно соединенные фазовый детектор, первый вход которого является входом устройства, безынерционное корректирующее звено, сумматор, к второму входу которого подключен реверсивный счетчик через цифроаналоговый преобразователь, и генератор, управляемый напряжением, выход которого подключен к второму входу фазового детектора, а также пороговый блок, выход которого соединен ЗЯ4. с управляющим входом реверсивного счетчика, отличающееся тем, что, с целью повьшения быстродействия при сохранении фильтрующей способности, между выходом фазового детектора и счетным входом реверсивного счетчика включены последовательно соединенные вычита- тель, второй вход которого соединен с выходом цифроаналогового преобразователя, преобразователь напряжение-частота и делитель с переменным коэффициентом деления, между входом управления которого и выходом фазового детектора включен индикатор биений, а выход порогового блока соединен с выходом вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1987 |

|

SU1474838A1 |

| Синтезатор частот | 1979 |

|

SU785943A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1469554A1 |

| Синтезатор частот | 1980 |

|

SU886254A2 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Следящий фильтр-демодулятор | 1980 |

|

SU1020970A1 |

Авторы

Даты

1986-10-15—Публикация

1984-06-20—Подача