Изобретение относится к вычислительной технике и может быть использовано для управления ламятью.

Целью изобретения - повышение быстродействия устройства.

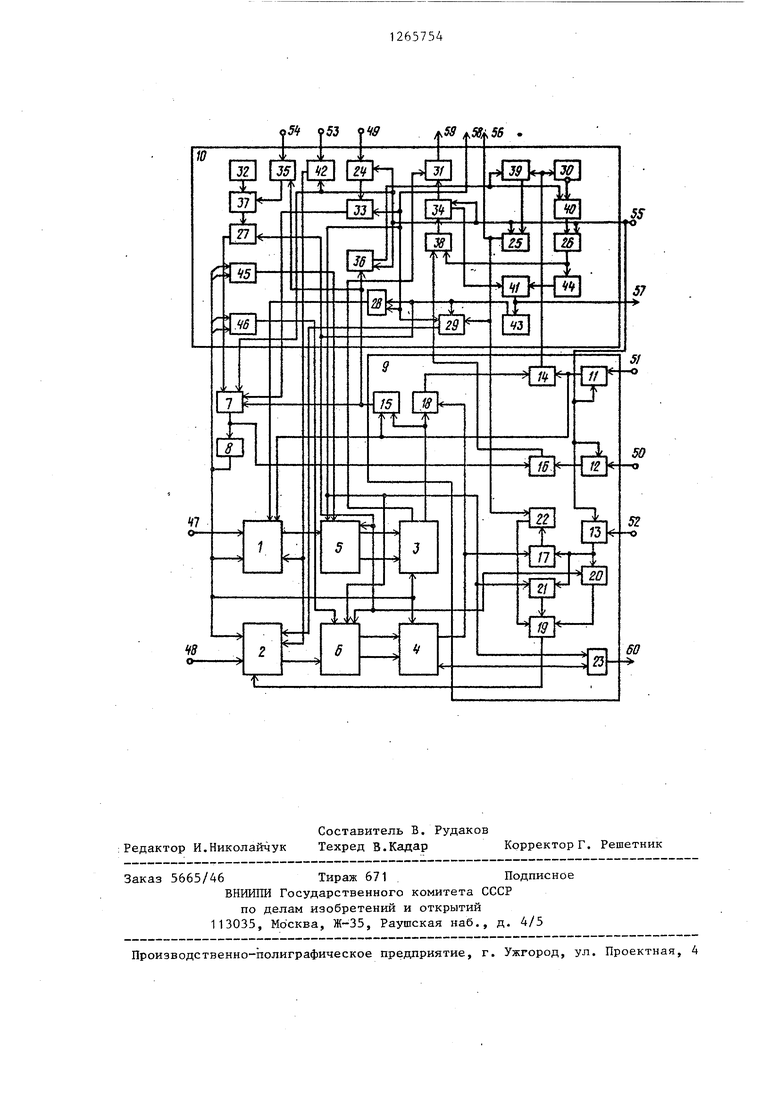

На чертеже изображена структурная схема устройства для управления памятью.

Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 коммутаторы, первый 5 и второй 6 блоки памяти, счетчик 7, дешифратор 8, блок 9 логического анализа и блок 10 местного управления.

Блок 9 логического анализа содержит первый 11, второй 12 и третий 13 регистры, первый 14, второй 15-и третий 16 блоки сравнения, первый 17 и второй 18 сумматоры, блок 19 элементов ИЛИ и блоки 20-23 элементов И с первого по четвертый.

Блок 10 местного управления содержит регистр 24, первый 25 и второй 26 триггеры, первый 27, второй 28 и третий 29 элементы ИЛИ, элемент НЕ 30, первый блок 31 элементов И, генератор 32 импульсов, второй блок 33 элементов И, третий 34, четвертый 35 и пятый 36 триггеры, элементы И 37-41 с первогопо пятый, шестой, триггер 42, формирователь 43 импульсов, элемент 44 задержки, второй 45 и третий 46 блоки элементов ИЛИ.

Устройство имеет входы 47-55 и выходы 56-60.

Сущность работы устройства для управления памятью заключается в следующем. Для каждой освободившейся области памяти заданной емкости и с определенным начальным адресом устанавливается место в таблиде начальны адресов свободных областей памяти, проверяется условие, является ли новая свободная область смежной с какой-либо из имеющихся областей. Если условие выполняется, то емкости двух областей суммируются. В противном случае проверяется условие, заполнена ли вся таблица свободной памяти, и если заполнена, то производится деление таблицы на две части и вновь поступившая область записывается на первое свободное место первой части таблицы. В противном случае вновь поступившей области памяти определяется место в соответствии с ее начальным адресом.

Устройство работает, следующим образом.

В исходном Состоянии счетчик 7, регистры 11-13 и 24 и триггеры 25, 26, 34-36 и 42 обнулены.

По входу 51 в регистр 11 записывается код начального адреса А освободившейся области памяти, а по входу 52 в регистр 13 - ее объем V. По входу 54 поступает импульс запуска и устанавливает триггер 35 в единичное состояние. При этом разрешается прохождение импульсов с генератора 32 через элементы И 37 и ИЛИ 27 на счет3 ный вход счетчика 7. Дешифратором 8 разрешается последовательное подключение ячеек блока 5 памяти через коммутатора 3 к входу блока 15. При этом производится сравнение содержи0 мого i-й (,n) ячейки блока 5 памяти (кода начального адреса А;(i-й свободной области памяти) с содержимым регистра 11 (код А). При выполнении условия А А; на выходе

5 блока 15 появляется сигнал, который обнуляет триггер 35 (чем запрещается прохождение импульсов с генератора 32), уменьшает содержимое счетчика 7 на единицу и устанавливает в единичное состояние триггер 36.

0

В результате проведенных действий в таблице памяти, реализованной блоками 5 и 6 памяти, установлено место для вновь освободившейся области папяти с начальным адресом А и ем5костью V. Затем проверяется, является ли эта область смежной с (1-1)-й, т.е. проверяется условие А,-, V, А (в блоке 6 памяти из ячеек хранятся коды емкостей свободных облас0тей памяти, коды начальных адресов которых хранятся в блоке 5 памяти).

При этом на выходе сумматора 18 появляется код суммы А{ + i-i который сравнивается с кодом А блоком 14. Если коды совпадают, то на выходе блока 14 имеется единичный сигнал, который устанавливает в единичное состояние триггер 25, сигнал с единичного выхода которого разрешает запись через элементы И 22 и ИЛИ 19 и коммутатор 2 кода суммы емкостей V. + V с выхода сумматора 17 в (1-1)-ю ячейку блока 6 памяти и вьздается на выход 56 устройства в качестве окончания его работы. 3 В противом случае триггер 26 уст навливается в единичное состояние (через элемент И 40) и имеет место один из следующих двух случаев: вся таблица заполнена, т.е. i-1 п-1; не вся таблица заполнена, т.е. i-14 п-1. В первом случае на выходе блока появляется единичный сигнал, который через элемент И 38 устанавливает триггер 34 в единичное состояние. Сигнал с единичного выхода этого триггера поступает на выход 58 в качестве сигнала окончания работы устройства, разрешает выдачу на выходы 59 и 60 устройства соответственно кодов начальных адрзсов из второй половины ячеек блока 5 памяти (через коммутатор 3 и элементы И31) и их емкостей из второй половины ячеек блока 6 памяти (через коммутатор 4 и элементы И 23), т.е. производится раздвоение таблицы свободной памяти (одна таблица переполняется, по этому она делится на две части,одна часть остается в блоках 5 и 6 памяти а другая подается на выходы устройства и записывается в другие блоки памяти). Кроме того, при этом обнуля ются вторые половины ячеек блоков 5 и 6 памяти, разрешается запись в -7П , счетчик 7 кода числа у + 1 из регистра 24 (куда он заносится по входу 49 устройства) через элементы И 33 и /п запись в (у + 1)-е ячейки блоков 5 и 6 памяти соответственно кодов, А (из регистра 11 .через коммутатор 1) и V (из регистра 13 через элементы И 21, ИЛИ 19 и коммутатор 2). При выполнении условия -1 п-1 необходимо записать код A(V) в i-ю ячейку блока 5(6) памяти, предварительно сдвинув (i,n-1)-e ячейки вниз на одну ячейку. В этом случае импуль с единичного выхода триггера 26 чере Элемент И 41 разрешает сдвиг на одну ячейку вниз информации для (i,n-1)-x ячеек блоков 5 и 6 памяти, увеличивает содержимое счетчика 7 на единицу и разрешает запись кодов А, V соответственно в i-e ячейки блоков 5 и 6 памяти. Единичный сигнал с i-ro выхода дешифратора 8 поступает на i-й вход (i, п-1)-х блоков элементов ИЛИ 45 и 46, чем разрешается сдвиг вниз на одну ячейку (Т п-1)-х ячеек 75Д 5 и 6 памяти. Сигнал с выхода блоков элемента И 41 в качестве сигнала окончания работы поступает на выход 57 устройства. При появлении сигнала на одном из выходов 56-58 устройства операционная система вьщает сигнал Исходное , состояние на вход 55 устройства, коTopbrti обнуляет счетчик 7, регистры 11-13 и 24 и триггеры 25, 26, 34-36 и 42. По входам 47 и 48 производится первоначальная установка содержимого ячеек блоков 5 и 6 (с помощью триггера 42), при этом в первую ячейку блока 5 памяти записывается максимальный адрес данного внешнего устройства, затем по входу 53 поступает импульс, который обнуляет триггер 42 ц- счетчик 7. На этом работа устройства заканчивается. Формула изобретения 1. Устройство для управле Я паблокимятью , дешифратор и счетчик, выход памяти которого соединен с входом-дешифратора, выход которого подключен к первым входам коммутаторов, выходы первого и второго коммутаторов соединены соответственно с первыми входами первого и второго блоков памяти, выходы которых подключены соответственно к вторым и третьим входам третьего и четвертого коммутаторов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок логического анализа и блок местного управления,причем первый и второй выходы третьего коммутатора соединены соответственна с первыми входами блока местного управления и блока логического анализа. первый и второй выходы четвертого коммутатора подключены соответственно к второму и третьему входам блока логического анализа, вторые входы первого и второго коммутаторов являются одним из входов устройства, выход дешифратора соединен с вторым входом блока местного управления, выход счетчика подключен к четвертому входу блока логического анализа, выходы блока местного управления с первого по четвертый соединены соответственно со счетным и первым установочными входами счетчика, с третьим входом первого коммутатора и вторым установочным входом счетчика, вычитающий вход которого соединен с первым выходом блока логического анализа, четвертый вход первого коммутатора соединен с вторым выходом блока логического анализа, пятый вход первого коммутатора и третий вход второго коммутатора подключены к пятому выходу блока местного управления, чет вертый вход второго коммутатора соединен с шестым выходом блока местного управления, выходы которого с седьмого по десятый подключены соответственно к второму входу второго блока памяти, к третьему входу блока логического анализа, второму входу первого блока памяти и третьему входу второго блока памяти, третьему входу первого блока памяти, четвертые входы блоков памяти подключены к восьмому выходу блока местного управления, первый выход блока логического анализа соединен с третьим входом блока местного управления,чет- 25 вертый вход которого соединен с треть им выходом блока логического анализа, пятый вход которого соединен с одиннадцатым выходом блока местного управления, пятый вход которого соединен с четвертым выходом блока логического анализа, пятый выход блока логического анализа соединен с пятым входом второго коммутатора, выходы блока местного управления и блока логического анализа с шестого по деся1254 тыи являются входами устройдругимиходы блока местного управления с двенадцатого по пятнадцатый и шестой выход блока логического анализа. 2. Устройство по П.1, отличающееся тем, что блок логического анализа содержит регистры. блоки сравнения, сумматоры, блоки элементов И и блок элементов ИЛИ, причем выход первого регистра подключен к первым входам первого и второго блоков сравнения, выход второго регистра соединен с первым входом третьего блока сравнения, выход третьего регистра подключен к первым входам первого сумматора и первого и второго блоков элементов И, входы блока элементов ИЛИ соединены, с выходами блоков элементов И с первого по третий, выходы первого и второго сумматоров подключены соответственно к первому входу третьего блока элементов И и второму входу первого блока сравнения, выходы блоков сравнения, блока элементов ИЛИ, четвертого блока элементов И и первого регистра являются выходами блока логического анализа, входами которого являются входы регистров, четвертого блока элементов И и второго сумматора, вторые входы блоков элементов И с первого по третий, первого сумматора, второго и третьего блоков сравнения.

5if 053 9fff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки изображений объектов | 1987 |

|

SU1495830A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления памятью. Цель изобретения - повышение быстродействия устройства. Устройство содержит коммутаторы, блоки памяти, счетчик, дешифратор, блок логического анализа и блок местного управления. Принцип работы устройства состоит в следующем. Определяется место для поступившего фрагмента памяти в таблице свободной памяти, наращивается соответствующий фрагмент памяти в таблице, если поступивший фрагмент является для него смежным, вновь поступивший фрагмент записывается в таблицу в соответствии с его начальным адресом, если он не является смежным, и таблица разделяется на две части, если она была полностью заполнена. 1 з.п. Р ф-лы, 1 ил. СЛ

| Заявка Великобритании № 1405496, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для ввода информации | 1981 |

|

SU993234A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1984-12-27—Подача