соединен с единичным входом второго триггера, единичный выход которого соединен с вторым управляю1ЦИМ входом коммутатора, с инверсным входом четвертого и первым входом пятого элементов И, выходы четвертого и пятого элементов И соединены соответственно с управляющим входом блока формирования адреса и с единичным входом четвертого триггера, единичный выход которого соединен с первым входом первого элемента И, информационные выходы блока памяти адресов эталонов соединены с информационными входами второго регистра, информационные выходы которого соединены с информационными входами пятого элемента ИЛИ и с входами элементов И второй группы, выход пятого элемента ИЛИ соединен с первым входом шестого, инверсными входами седьмого, восьмого, первым инверсным входом девятого элементов И и вторыми входами элементов И второй группы, выходы элементов И второй группы сединены с первыми входами элементо ИЛИ третьей, группы, выходы которых соединены с группой адресных входов третьего блока памяти микрокоманд, единичный выход первого триггера соединен с входом считывания второго блока памяти микрокоманд и первым входом шестого элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, а информационньае выходы первого сч чика соединены с входами блока анализа, первый выход блока анализа соединен с первым входом десятого и инверсным входом одиннадцатого , элементов И, выход которого соединен с входом четвертого элемента И и управлякндими входами элементов И третьей группы, второй выход блока анализа соединен с первым входом седьмого элемента ИЛИ, выход которого соединен с инверсными входами двенадцатого и тринадцатого элементов И и является управляющим выходом устройства, установочный первый и второй тактовые вхоДы устройства соединены соответственно с установленным входом второго счетчика, с входами двенадцатого и тринадцатого элементов И, выход двенадцатого элемента И соединен с вторыми входами первого, второго и третьего элементов И, выход десятого элемента И соединен с первы информационным входом коммутатора с единичным входом третьего триггера, выход тринадцатого элемента И соединен с вторым информационным входом KOivwyTaTOpa, с первыми входами восьмого и девятого элементов выход которого соединен с входом одинадцатого элемента И, с втор входом пятого элемента И и вторым

входом первого элемента ИЛИ, выход которого соединен с входом обнуления первого счетчика, выход первого элемента задержки соединен с входом обнуления четвертого триггера и со счетным входом второго счетчика, информационный выход которого соединен с входами элементов И четвертой группы, с информационными входами блока памяти адресов эталонов и с входами дешифратора, выход которого соединен с вторым входом седьмого элемента ИЛИ, выход шестого элемента И соединен с входом чтения третьего блока памяти микрокоманд, через второй элемент задержки - с вторым входом второго элемента ИЛИ, с инверсными входами элементов И четвертой группы, выходы которых соединены с вторыми входами элементов ИЛИ третьей группы, информационные выходы, первого и третьего блоков памяти микрокоманд соединены соответственно с вторыми и третьими входами элементов ИЛИ втрой группы, выход второго.элемента И соединен с входом седьмого элемента И и с инверсным входом шестого элемента И, выход седьмого элемента И соединен с входом чтения первого блока памяти микрокоманд, с вторым входом шестого элемента ИЛИ, и с .входом чтения блока памяти адресов эталонов, выходы микроопераций регистра микрокоманд соединены с вторыми входами элементов И третьей группы, выходы которых образуют группы выходов микроопераций устройства, выходы контрольного разряда, адресные выходы и выходы микроопераций регистра микрокоманд соединены с группой информационных входов третьего блока памяти , с группой входов первого сумматора по модулю два, инверсный выход которого соединен с первьпл входом восьмого элемента ИЛИ, выходы регистра адреса соединены с входами второго сумматора по модулю два, инверсный выход которого соединен с вторым входом восьмого элемента ИЛИ, выход контрольного разряда регистра микрокоманд соединен с информационным входом второго сумматора по модулю два, выход восьмого элемента ИЛИ соединен с вторым инверсным входом девятого элемента И и с вторым входом восьмого элемента И, выход которого соединен с вторым входом десятого элемента И, группа адресных выходов блока формирования адреса соединена с вторыми входами элементов ИЛИ первой группы.

2. устройство по п. 1, отличающееся тем, что блок анализа содержит первый и второй элементы И и элемент ИЛИ, причем первый, второй, третий и четвёртый входы группы входов блока соединены соответственно с первым, втор1Ш и третьим входами первого элемента И и с первым входом элемента ИЛИ, выход которого является первым выходом блока, выход первого элемента И соединен с вторым входом элемента ИЛИ, второй, третий и четвертый входы группы входов блока соединены соответственно с первым, вторым и третьим входами второго элемента И, выход которого является вторым выходом блока.

3. Устройство по п. 1, отличающееся тем, что блок формирования адреса содержит первую вторую и третью группы элементов И и группу сумматоров по модулю два, причемуправлякмций вход блока соеди.. нен с первыми входами элементов И первой и второй групп, выходы которых образуют соответственно группы

немодифицируемых и модифициру 1ых частей адресных выходойв блока, группа немода1фицированных разрядов первой группы входов блока соединена с вторыми входами соответствующих элементов И первой группы, группа модифицированных разрядов первой группы входов блока соединена с первыми входами соответствующих сумматоров по модулю два, выходы которых соединены с вторыми входами соответствующих элементов И второй группы, входы кода проверяемого логического условия первой группы входов блока соединены .с первьши входами соответствующих элементов И третьей группы, Ш:1ходы которых соединены с вторыми входами соответствующих сумматоров по модулю два группы, вторая группа входов блока соединена с вторыми входами соответствуюп№1Х элементов И третьей группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммный процессор | 1980 |

|

SU980098A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

1. МИКРОПРСЯРАЬИНОЕ УСТРОЙСТЮ УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, первый триггер, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ, регистр микрокоманд, регистр адреса, блок формирования адреса, причем выходы регистра адреса микрокоманд соединены с адресными входами первого блока памяти микрокоманд, группа адресных выходов регистра микрокоманд соединена с входами первой группы входов блока формирования адреса, первая группа информационных входов устройства соединена с второй группой входов.блока формирования адреса, отличающ е ее я тем, что,, с целью повышения быстродействия и отказоустойчивости устройства, введены первый и второй счетчики, второй, третий и четвертый триггеры, третий блок памяти микрокоманд, блок памяти адресов эталонов, блок анализа, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатой, двенадцатый и тринадцатый элементы И, четвёртый, пятый, шестой, седьмой и восьмой эл ленты ИЛИ, дешифратор, первый и второй элементы задержки, первый и второй регистры, первая, вторая и третья .группа элементов ИЛИ, первая, вторая, третья и четвертая группа элементов И, первый и второй сумматоры по модулю два и коммутатор, причшл вторая группа информационных входов устройства соединена с первыми входами элементов И первой группы, выходы КОТО1ЯШ соединены с первыми -входами элементов ИЛИ первой группы, выходы последних соеда нены с входами регистра адреса, .вы-, ходы регистра адреса соединены с адресньми входами блока пгшяти адресов эталонов и второго блока памяS ти микрокоманд, выход которого соединен с информационным входом первого регистра, первый управляющий вход устройства соединен с вторыми входами элементов И первой группы, с первыми входами первого, второго и третьего эл1ементов ИЛИ, с ус тановочными входами регистра микрокоманд и первого триггера, нулевой выход которого соединен с установочн1Л4 входом первого регистpai и первым управляющим входом коммутатора, выход первого элемента И соединен с входом записи .блока памяти адресов эталонов, с входом записи третьего блока памяти микрокоманд, с входом третьего элемента ИЛИ, с входом первого элемента задержки, выход третьего элемента ИЛИ соединен с установочными входам второго и тре.тьего триггеров нулевой выход которого соеда нен с первым входсж второго элемента И, выхода первого регистра соединены с входгши четвертого элемента ИЛИ второй группы, выходы которых соединены с информационными входами регистра микро- . команд, выход четвертого элемента ИЛИ соединен с первым входом третьего элемента И, выход которого

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проект ровании устройств управления цифровых систем. Известно микропрограммное устройство управления с восстановлением функционирования при сбоях, содержащее блок регистров, блок па мяти микрокоманд и регистр микроко манды С ЗНедостатком известного устройст является низкая отказоустойчивость обусловленная невозможностью автоматического восстановления работоспособности при устойчивых отказах ячеек блока памяти микрокоманд. Известно также микропрограммное устройствр управления с водстановлением при сбоях, содержащее блок регистров,блок памяти микрокоманд и регистр микрокоманды {2. Недостатком этого устройства яв ляется низкая отказоустойчивость, обусловленная отсутствием автомати ческого восёт ановяейия работоспо собности при устойчивых отказах. Наиболее бтшзким по техническо сущности и достигаемому положитель ному эффекту к предлагаемому является микропрограммное устройство управления, содержащее первый и вт рой блоки памяти микрокоманд, первый триггер, три элемента И, три элемента ИЛИ, регистр микрокоманд, регистр адреса, блок формирования адреса, причем выходы регистра адресасоединены с адресными входами первого блока памяти микрокомандг выходы первой группы выходов регистра микрокоманд соединёЕШ с входами первой группы входов блока формирования адреса, входы второй группы входов -которого соединены с входами первой группы входов устройства. В данвс 4 устройстве микропрограмкы, записанные в первом блоке памяти, разбиты на сепленты. После выполнения каждого сегмента ымкропрогра11Ф1ы ос чаёствляется его обновление восстановление путем перезаписи эталонных значений микрокОг манд, входяищх в данный сегмент микрокоманд первого блока памяти микрокоманд, из соответствующих, йчеек п 1мяти микрокоманд второго блока памяти. При зацикливании внутри сегмента, обновление его осуществляется по истечении допустимого промежутка времени, прошедшего с момента начала выполиения микрокоманд, хранящихся в- йем ЗЦНедостатками данного устройства являются низкое быстродействие и низкая отказоустойчивость. Низкое быстродействие устройства обусловлено отсутствием избирательности .при обновлении информации, т.е. тем, что обновлению подвергается при отказе полностью весь сегмент микрокоманд, хотя для сохранения .работоспособности устройства управления достаточно обновлять лишь искаженные микрокоманды. Низкая отказоустойчивость устройства обусловлена тем, что описанная дисциплина его функционирования не обеспечивает, полной защиты от повторного проявления случай ных сбоев в первом блоке памяти, а возможность обнаружить ошибки в информации в момент ее считывания из первого блока памяти и выдачи на выход отсутствует. Кроме того, при устойчивых отказах ячеек перво го блока памяти микрокоманд последующее обновление информации в нем не приводит к обходу отказавших ячеек и восстановлению соответству щих микрокоманд, вследствие чего устройство становится неработоспособным. Таким образом, отсутствие избирательности при восстановлении информации, невозможность обнаружени ошибок в информации, считываемой из первого блока памяти микрокоман а также невозможность восстановления информации при наличии отказав ших ячеек в первом блоке памяти снижает быстродействие и отказоустойчивость устройства. Цель изобретения. - повышение бы стродействия и отказоустойчивости микропрограммного устройства управ ления. Поставленная цель достигается тем, что в микропрограммное устрой ство .управления, содержащее первый и второй блоки памяти микрокоманд, первый триггер, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ, регистр микрокоманд, регистр адреса, блок фор мирования адреса, причем выходы регистра адреса микрокоманд соединены с адресными входами первого блока памяти микрокоманд, группа адресных выходов регистра микрокоманд соединены с входами первой группы входов блока формирования ад реса, первая группа информационных входов устройства соединена с второй группой входов блока формирования адреса, введены первый и второй счетчики, второй, третий и четвертый триггеры, третий блок памяти микрокоманд, блок памяти адресов эталонов, блок анализа, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, две надцатый и тринадцатый элементы И, четвертый, пятый, шестой, седьмой и восьмой элементы ИЛИ, дешифратор первый и второй элементы задержки, первый и второй регистры, первая, вторая и третья группа элементов ИЛИ, первая, вторая, третья и четвертая группа элементов И, первый и второй сумматоры -по модулю два и коммутатор, причем вторая групп;, информационных входов устройства соединена с первыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ первой группы, выходы последних соединены с входами регистра адреса, выходы регистра адреса соединены с адресными входами блока памяти адресов эталонов и второго блока памяти микрокоманд, выход которого соединен с информационным входом первого регистра, первый управляющий вход устройства- соединен с вторыми входами элементов И первой группы, с первыми входами первого, второго и третьего элементов ИЛИ, с установочными входами регистра микрокоманд и первого триггера, нулевой выход которого соединен с установочным входом первого регистра и первым управляющим входом коммутатора, выход первого элемента И соединен с входом записи блока памяти адресов эталонов, с входом записи третьего блока памяти микрокоманд, с вторым входом третьего элемента ИЛИ, с входом первого элемента задержки, выход третьего элемента ИЛИ соединен с установочными входами второго и третьего триггеров, нулевой выход которого соединен с первым входом второго элемента И, выходы первого регистра соединены с входами четвертого элемента ИЛИ второй группы, выходы которых соединены с информационными входами регистра микрокоманд, выход четвертого элемента ИЛИ соединен с первым входом третьего элемента И, выход которого соединен с единичным входом второго триггера, единичный выход которого соединен с вторым управляющим входом коммутатора, с инверсным входом четвертого и первым входом пятого элементов И выходы четвертого и пятого элементов И соединены соответственно с управляющим входом блока формирования адреса и с единичным входом четвертого триггера, единичный выход которого соединен с первым входом первого элемента И, информационные выходы блока памяти адресов эталонов соединены с информационными входами второго регистра, информационные выходы которого соединены с информационными входами пятого элемента ИЛИ и с входами элементов И второй группы, выход пятого элемента ИЛИ соединен с первым входом шестого, инверсными входами седьмого, восьмого, первым инверсным входом девятого элементов Ни вторыми входами элементов И второй группы, выходы элементов И второй группы соединены с первыми входами элементов ИЛИ третьей группы, выходы которых соединены с группой адресных входов третьего блока памяти микрокоманд, единичный выход первого триггера соединен с входом считывания второго блока памяти микрокоманд и первым входом шестого, элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, а информационные выходы первого счетчика соединены с входами блока анализа, первый выход блока анализа соединен с первым входом десятого и инверсным входом одиннадцатого элементов И, выход которого соединен с входом четвертого элемента И и управляющими входами элементов К третьей груп пы, .второй выход блока анализа соединен с первым входом седьмого эле мента ИЛИ, выход которого соединен с инверсными входами двенадцатого и тринадцатого элементов. И и является управляющим выходом устройства, установочный первый и второй тактовые входы устройства соединены соответственно с установленным входом второго счетчика, с входами двенадцатого и тринадцатого элементов И, выход двенадцатого элемента И соединен с вторыми входами первого, второго и третьего элементов И, выход десятого элемента И соединен с первым информационным входом коммутатора и с единичным входом третьего триггера, выход тринадцатого элемента И соединен с вторым информационным входом коммутатора, с первыми входами восьмого и девятого элементов И, выход которого соединен с входом одиннадцатого элемента И, с вторым входом пятого элемента И и вторым входом первого элемента ИЛИ, выход которого соединен с входом обнуления- первого счетчика, выход первог элемента задержки соединен с входо обнуления четвертого триггера и со счетным входом второго счетчика, и формационный выход которого соедин с входами элементов И четвертой группы, с информационнЕлми .входами блока памяти адресов эталонови с входами дешифратора, выход которог соединен с вторым входом седьмого элемента ИЛИ, выход шестого элемента И.соединен с входом чтения третьего блока памяти микрокоманд, через второй элемент задержки - с вторым входом второго элемента ИЛИ с инверсными входами элементов И ч вертой группы, выходы которых соед нены с вторыми входами элементов И третьей группы, информационные выходы первого и третьего блоков памяти микрокоманд соединены соответ венно с вторыми и третьими входами элементов ИЛИ второй группы, выход второго элемента И соединен с входом седьмого элемента Ни с инверс ным входом шестого элемента И, вых седьмого элемента И соединен с входом чтения первого блока памяти микрокоманд, с вторым входом шестого элемента ИЛИ, с входом чтения блока памяти адресов эталонов, выходы микроопераций регистра микрокоманд соединены с вторыми, входами элементов И третьей группы, выходы которых образуют группу выходов микроопераций устройства, выходы контрольного разряда, адресные выходы и выходы микроопераций регистра микрокоманд соединены с группой информационных входов третьего блока памяти, с группой входов первого сумматора по модулю два, инверсный выход которого соединен с первым входом восьмого элемента ИЛИ, выходы регистра адреса соединены с входами второго сумматора по модулю два, инверсный выход которого соединен с вторым входом восьмого элемента ИЛИ, выход контрольного 1зазряда регистра микрокоманд соединен р информационным входом второго сумматора по модулю два, выход восУьмого элемента ИЛИ соединен с вторым инверсным входом девятого элемента И и с вторым входом восьмого эле иента И, выход которого соединен с вторым входом десятого элемента И, группа адресных выходов блока формирования адреса соединена с вторыми входами элементов ИЛИ первой группы. Кроме того, блок анализа содержит первый и второй элементы И и элемент ИЛИ, причем первый, второй, третий и четвертый входы группы входов блока соединены соответственно с первым, вторым и третьим входами первого элемента И и с первым входом элемента ИЛИ, выход которого является первым выходом блока, выход первого элемента И соединен с вторым входом элемента ИЛИ, второй,. третий и четвертый входы группы входов блока соединены соответственно с первым, вторым и третьим входами второго элемента И, выход которого является вторым выходом блока. Кроме того, блок формирования адреса содержит первую, вторую и третью группы элементов И и группу сумматоров по модулю два, причем управляющий вход блока соединен с первыми входами элементов И первой и второй групп, выходы которых образуют соответственно группы немодифицируемых и модифицируемых частей адресных выходов блока, группа немодифицированных разрядов nepiвой группы входов блока соединена с вторыми входами соответствующих элементов И первой группы, группа модифицированных разрядов первой группы входов блока соединена с первыми входами соответствующих сумматоров по модулю два, выходы которых соединены с вторыми входами соответствующих элементов И второй группы, входы кода проверяемого логического условия первой группы входов блока соединены с первыми входами соответствующих элементов И третьей группы, выходы которых соединены с вторыми входами соответствующих сумматоров по модулю два группы, вторая группа входов блока соединен с вторыми входами соответствующих элементов И третьей группы

Сущность изобретения состоит в повышении быстродействия микропрограммного устройства управления за счет исключения неискаженных микрокоманд из числа обновляемых, а также в повышении его отказоустойчивости путем осуществления контроля правильности формирования микрокоманд перед их выполнением и автоматического их .восстановления при устойчивых отказах ячеек памяти первого блока памяти микрокоманд.

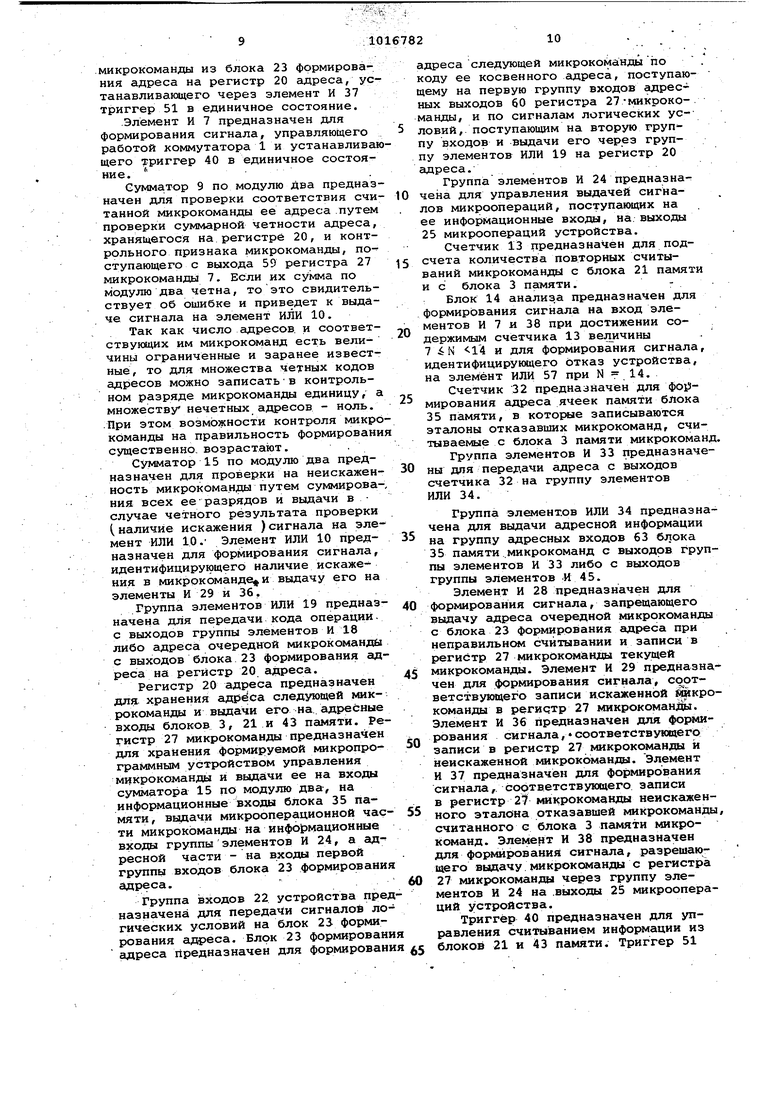

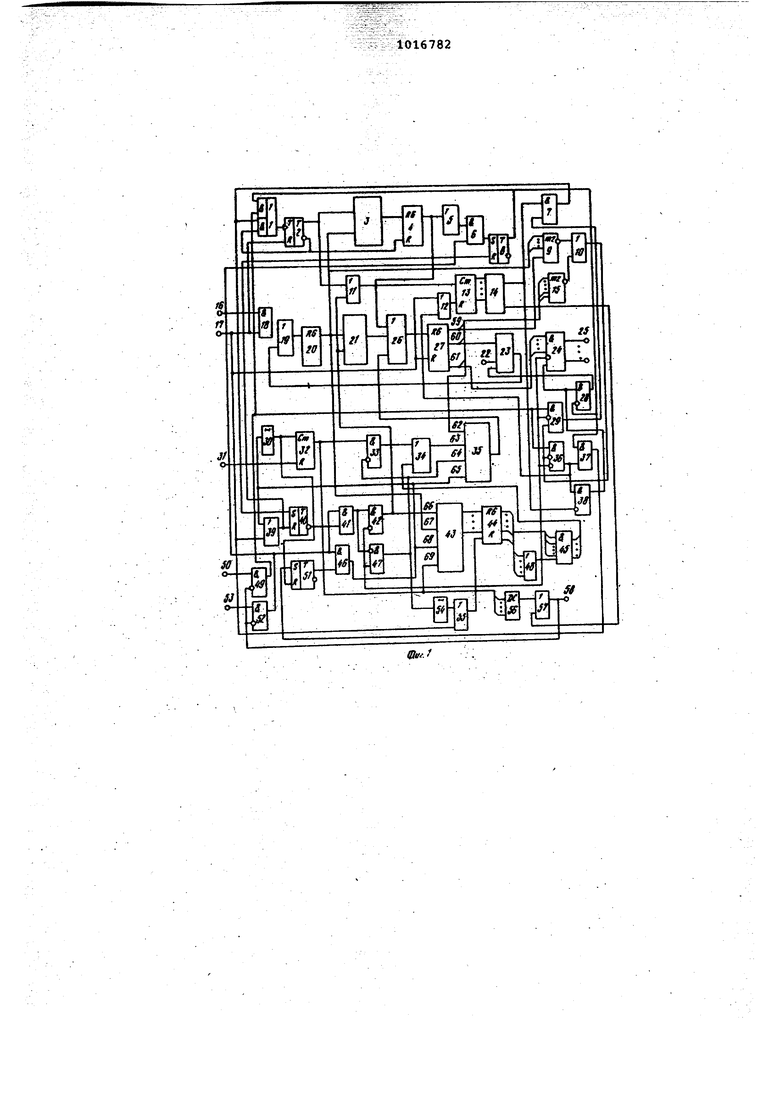

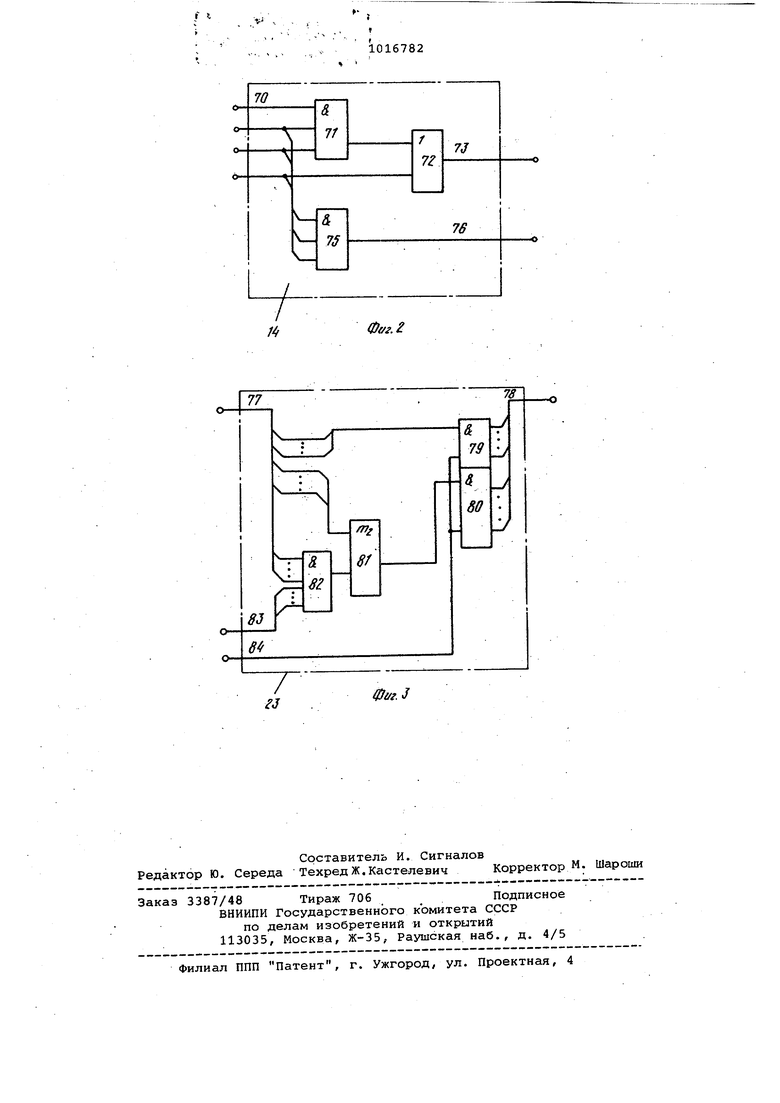

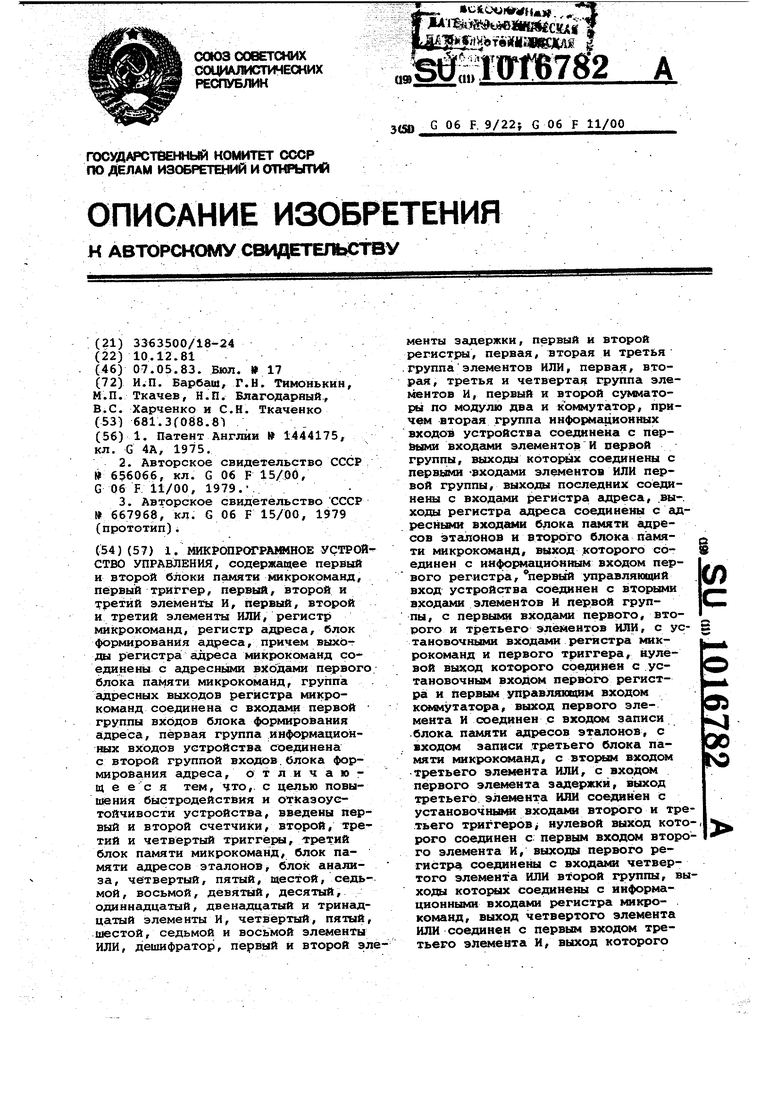

На фиг. 1 представлена функциональная схема предлагаемого микропрограммного устройства управления на фиг. 2 - функциональная схема блока анализа; на фиг. 3 - функциональная схема блока формирования адреса.

Микропрограммное устройство управления содержит (фиг. 1) коммутатор 1, первый триггер 2, второй блок 3 памяти микрокоманд, первый регистр 4, четвертый элемент ИЛИ 5, третий элемент И 6, десятый элемент И 7, второй триггер 8, второй сумматор 9 по модулю два, восьмой элемент ИЛИ 10, шестой элемент ИЛИ 11, первый элемент ИЛИ 12, первый счетчик 13, блок 14 анализа, первый сумматор 15 по модулю два, вторую группу входов 16 устройства, первый вход 17, первую группу элементов И 18, первую группу элементов ИЛИ 19, регистр 20, первый блок 21 памяти.микрокоманд, первую группу входов 22 устройства, блок 23 формирования адреса, третью группу элементов И 24, выходы 25 микроопераций устройства, вторую группу .элементов ИЛИ 26, регистр 27 микрокоманды, четвертый элемент И 28, восьмой элемент И 29, первый элемент 30 задержки, второй вход 31 устройства, второй счетчик 32, четвертую группу элементов И 33, третью группу элементов ИЛИ .34, третий блок 35 памяти микрокоманд, шестой элемент И 36, десятый элемент И 37, одиннадцатый элемент И 37, третий элемент ИЛИ 39, третий триггер 40, второй элемент И 41, седьмой элемент И 42, блок 43 памяти адресов э.талонов, второй регистр 44, вторую группу элементов И 45, первый элемент И 46, шестой элемент И 47, пятый элемент ИЛИ 48, тринадцатый элемент И 49, четвертый вход 50, четвертый триггер 51, двенадцатый элемент И 52, третий вход 53 устройства, второй элемент 54 задержки второй ИЛИ 55, дешифратор 56, седьмой элемент ИЛИ 57, выход отказа устройства 58, выходы группы выходов регистра 27 микрокоманды выход 59 контрольного разряда, адресные выходы 60, выходы 61 микроопераций, группу 62 информационных входов блока 35, группу адресных входов 63 блока 35, вход 64 чтения блока 35, вход 65 записи блока 35, вход 66 чтения блока 43, группу адресных входов 67 блока 43, вход 68 записи блока 43, группу информационных входов 69 блока 43 памяти. Блок 14 анализа (фиг. 2 содержит группу входов 70, первый элемент И 71, элемент ИЛИ 72, первый выход 73, второй элемент И 75, второй выход 76. Блок формирования .адреса (фиг. 3 содержит первую группу входов 77, группу выходов 78, первую группу элементов И 79, вторую группу элементов И 80, группу сумматоров 81 по модулю два, третью группу элементов И 82, вторую группу входов 83, управляющий вход 84.

Назначение основных функциональных элементов функциональной схемы микропрограммного устройства управления (фиг. 1) состоит в следующем

БЛОК 21 памяти микрокоманд предназначен для хранения и выдачи микрокоманд на регистр 27. Блок 35 памяти предназначен для хранения эталонов отказавших микрокоманд, считываекых при отказе последних из блока 3 памяти микрокоманд. Блок 43 памяти адресов эталонов отказавших микрокоманд предназначен для хранения адресов ячеек памяти блока 35 памяти микрокоманд, в которых записаны эталоны отказавших микрокоманд по данному адресу, т.е. адреса ячеек памятя блока 43 памяти и блока 21 памяти совпадают.

Коммутатор 1 предназначен для формирования сигнала изменения состояния триггера 2 на противоположное. Регистр 4 предназначен для хранения считанной из блока 3 памяти эталонной микрокоманды. Триггер 2 предназначен для управления считыванием эталонной микрокоманды из блока 3 памяти микрокоманд.

Элемент ИЛ)(1 5 и элемент И 6 предназначены для формирования сигнала на S-вход триггера 8. Триггер 8 предназначен для формирования сигнала, изменяющего через коммутатор состояние триггера 2 на противоположное, через элемент И 28 запрещающего выдачу адреса очередной .микрокоманды из блока 23 формирования адреса на регистр 20 адреса, ус танавливакмцего через элемент И 37 триггер 51 в единичное состояние. .Элемент И 7 предназначен для формирования сигнала, управляющего работой коммутатора 1 и устанавлива щего триггер 40 в единичное состояние. Сумматор 9 по модулю два предназ начен для проверки соответствия счи танной микрокоманды ее адреса .путем проверки суммарной четности гщреса, хранящегося на регистре 20, и контрольного признака микрокоманды, поступающего с выхода 59 регистра 27 микрокоманды 7. Если их сумма по модулю два четна, то это свидительствует об ошибке и приведет к выдаче сигнала на элемент ИЛИ 10. Так как число адресов, и соответствующих им микрокоманд есть величины ограниченные и заранее известные, то для множества четных кодов адресов можно записатьв контрольном разряде микрокоманды единицу, а множеству нечетных адресов - ноль. .При этом возможности контроля микро команды на правильность формировани существенно, возрастает. сумматор 15 по модулю два предназначен для проверки на неискаженность микрокоманды путем суммироваНИИ всех ее разрядов и выдачи в случае четного результата проверки (наличие искажения )сигнала на элемент ИЛИ 10. Элемент ИЛИ 10 предназначен для формирования сигнала, идентифицирующего наличие искажения в микрокоманде и выдачу его на элементы И 29 и 36. Группа элементов ИЛИ 19 предназначена для передачи кода операций, с выходов группы элементов И 18 либо адреса очередной микрокоманда с выходов блока 23 формирования адреса на регистр 20 адреса. Регистр 20 адреса предназначен для хранения адреса следующей микрокоманды и выдачи его на адресные входы блоков 3, 21 и 43 памяти. Регистр 27 микрокоманды предназна ен для хранения формируемой микропрограммным устройством управления микрокоманды и выдачи ее на входы сумматора 15 по модулю два, на информационные входы блока 35 памяти, вьщачи микрооперационной час ти микрокоманды на инфо45мационные входы группы элементов И 24, а адресной части - на входы первой группы входов блока 23 формировани адреса. Группа входов 22 устройства пред назначена для передачи сигналов логических условий на блок 23 формирования адреса. Блок 23 формировани адреса предназначен для формировани адреса следующей микрокоманды по . коду ее косвенного адреса, поступаю- ему на первую группу входов адресных выходов 60 регистра 27-микрокоманды, и по сигналам логических ус-ловий, поступающим на вторую группу входов и выдачи его через группу элементов ИЛИ 19 на регистр 20 адреса. Группа элементов И 24 предназначена для управления выдачей сигналов микроопераций, поступающих на ее информационные BXOJUJ, на выходы 25 микроопераций устройства. Счетчик 13 предназначен для подсчета количества повторных считываний микрокоманды с блока 21 памяти и с блока 3 памяти.- . : Блок 14 анализ.а предназначен для формирования сигнала на вход элементов и 7 и 38 при достижении содержимым счётчика 13 вел.ичины 7 iN 14 и для формирования сигнала, идентифицирующего отказ устройства, на элемент ИЛИ 57 при N - 14. Счетчик 32 предназначен для формирования адреса ячеек памяти блока 35 памяти, в которые записываются эталоны отказавших микрокоманд, считываемые с блока 3 памяти микрокоманд. Группа элементов И 33 предназначены для передачи адреса с выходов счетчика 32 на группу элементов ИЛИ 34. Группа элементов ИЛИ 34 предназначена для выдачи адресной информации на группу адресных входов 63 блока 35 памяти микрокоманд с выходов группы элементов И 33 либо с выходов группы элементов И 45. Элемент И 28 предназначен для формирования сигнала, запрещающего выдачу адреса очередной микрокоманды с блока 23 формирования адреса при неправильном считывании и записи в регистр 27 микрокоманды текущей микрокоманды. Элемент И 29 предназначен для фрр|мирования сигнала, соответствующего записи искаженной микрокоманды в регистр 27 микрокоманды. Элемент и 36 предназначен для формирования сигнала,соответствующего записи в регистр 27 MHKpOKOMaHj j и неискаженной микрокоманды. Элемент И 37 предназначен для формирования сигнала, сортветствующего записи в регистр 2 микрокоманды неискаженного эталона отказавшей микрокоманды, считанного с блока 3 памяти микрокоманд. Элемент И 38 предназначен для формирования сигнала, разрешающего выдачу.микрокоманды с регистра 27 микрокоманды через группу элементов И 24 на .выходы 25 микроопераций устройства. Триггер 40 предназначен для управления считыванием информации из блоков 21 и 43 памяти. Триггер 51

предназначен для формирования сигнала, разрешающего запись информации в блоки 43 и 45 памяти, и увеличивающего содержимое счетчика 32 на единицу. Элемент И 42 предназначен для формирования сигнала на вход считывания информации блоков 21 и 43 памяти и увеличения содержимого счетчика 13 на единицу. Элемент И 46 предназначен для формирования сигнала на входы записи блоков 43 и 35 памяти, на - вход триггера 40 и увеличивающего содержимое счетчика 32 на единицу. Элемент И 47 предназначен для формирования сигнала на вход 64 считывания блока 35 памяти и обнуляющего через элемент 54 задержки и элемент-ИЛИ 55 регистр 44. Регистр 44 предназначен для хранения адреса эталона отказавшей микрокоманды, хранящегося в блоке 35 памяти микрокоманд считанного с блока 43 памяти.

Группа элементов И 45 предназначена для выдачи кода адреса с регис ра 44 на группу элементов ИЛИ 34.

Элементы И 52 и 49 предназначены для разрешения подачи тактовых импульсой первой и второй фазы с соответствуюй№1Х выходов генератора татовых импульсов не показан ), поступающих G третьего 53 и четвертого 50 входов устройства на его элемента при исправном функционировании устройства и на содержимое счетчика 32. Дешифратор 56 предназначен для формирования сигнала в момент, когда содержимое счетчика 32 достигнет определенного 3 наче.ния.

Элемент ИЛИ 57 предназначен для формирования сигнала Отказ устройства . Элемент И 71 предназначен для формирования сигнала при единичном значении первого, второго и третьего входов. Элемент ИЛИ 72 предназначен для формирования сигнала, соответствующего содержимому счетчика 13 7 и выдачи его на выход 73 блока 14. Элемент И 75 предназначен для формирования сигнала, соответствующего, содержимому счетчика 13 14 и выдачи его на выход 76 блока 14.

Назначение основных функциональных элементов блока 23 формирования адреса (фиг. 3) состоит в следующем

Группа элементов И 80 предназначена для выдачи модифицированной части адреса очередной микрокоманды выходов 78 блока при наличии сигнала на управляющем входе блока 84. Группа элементов И 79 предназначена для передачи немодифидируемой части адреса на выходы группы выходов 78 блока при наличии сигнала на управляющем входе 84 блока, а группа сумматоров 81 по модулю два предназначена для формирования модифицированной части адреса очередной микрокоманды. Группа элементов И 82 предназначена для управления подаче кода логического условия модифицирующего модифицируемую часть адреса очередной микрокоманды и выдачу его на группу сумматоров 81 по модулю два.

Группа входов 77 предназначена для передачи на элементы блока 23 формирования адреса немодифицированного кода адреса очередной микрокоманды.

Группа входов 83 предназначена для передачи в блок 23 формирования адреса сигналов логических условий с группы входов 22 устройства. Вход 31 предназначен для выдачи сигнала обнуления на вход счетчика 32.

Блок 23 формирования адреса функционирует следующим образом.

Косвенный адрес очередной микрокоманды состоит из трех полей: поле немодифицируемой части адреса; поле модифицируемой части адреса} поле кода проверяемого логического условия.

В зависимости от содержимого третьего поля возможны два режима работы блока формирования адреса.

Первый режим. Содержимое третьеГо поля косвенного адреса - нулевое. Этот режим соответствует работ микропрограммного устройства управления на линейных участках микропрограмм.

В эТом режиме код косвенного адреса очередной микрокоманды управления поступает на группу входов 77 блока 23. Первое поле адреса поступает на первые входы элементов И группы элементов И 79. Вторгре поле адреса поступает через группу .сумматоров 81 по модулю два на первые входы элементов И группы элементов И 80. При наличии сигнала на управляющем входе блока 84 адрес очередной микрокоманды с выходов . групп элементов И 80 и 79 поступает на группу выходов 78 блока.

Второй реямм. Содержимое третьег поля косвенного адреса очередной микрокоманды - ненулевое.

Этот режим соответствует формированию адреса очередной микрокоманды в точке ответвления микропрограммы.

Косвенный адрес очередной микрокоманды поступает на группу входов 77 блока 7. Код с первого поля адреса поступает на первую группу входов группы элементов И 79. Код с второго поля адреса поступает на первую группу входов группы сумматоров 81 по модулю два.

Код с третьего поля адреса поступает на первую группу входов

группы элементов И 82. Код логических условий с группы входов 83 поступает на вторую группу входов группы элементов И 82. Код результата проверки логических условий с выходов группы элементов И 82 поступает на входы второй группы входов группы сумматоров 81 по модулю два, где модифицирует содержимое второго поля косвенного адреса очередной микрокоманды. Сигналы с выходов группы сумматоров 81 по модулю два поступают на входы группы информационных входов группы элементов И 80. .

При наличии сигнала на входе 84 блока, адрес очередной микрокоманды с выходов группы элементов И 80 поступает на группу выходов 78 блока 23.

Предлагаемое микропрограммное устройство управления (фиг.. 1 )

работает следующим образом. I

На входы 53 и 50 поступают тактовые импульсы первой и второй фазы не перекрывающиеся во времени. На вход 17 перед началом выполнени микpoпpoгpaм и поступает из центрального устройства управления (не показано ) сигнал Пуск, запускающий работу устройства. Работа устройства возможна в следующих режимах: выполнение микропрограмм, сбо при считывании микрокоманд, отказ ячейки памяти, в которой хранится считываемая микроко1у1анда, выполнени вместо отказавшей микрокоманды эталона.

Работа устройства в .первом режиме осуществляется следующим образом.

При поступлении сигнала Пуск :на вход 17 устройства, код операции с основной памяти вычислительной системы (не показано )через группы входов 16, группу элементов И 18 и группу элементов ИЛИ 19 поступает на регистр адреса 20 и записывается в нем.

Триггеры 2 и 40, регистры 4, 27 и 44, счетчик 13 обнуляются по нуле вому входу. На выходе сумматора 15 по модулю два появляется единичный сигнал, который открывает через элемент ИЛИ 10 элемент И 29 и закрывает элемент И 36.

Далее на вход 53 устройства поступает тактовый импульс первой фазы. Он проходит через элементы И 52 И 41 и 42, на вход 66 считывания блока 43 памяти, управляющий вход блока 21 памяти микрокоманд и через элементы ИЛИ 11 на счетный вход счетчика 13. При этом из блока 21 памяти микрокоманд считывается первая микрокоманда микропрограммы, соответствующая коду операции поступившей в регистр 20 адреса. Через

группу элементов ИЛИ 26 она поступа ет на регистр 27 микрокоманды и записывается в нем. Из блока 43 памяти считывается нулевой код, Со.держимое счетчика 13 увеличивается,

на единицу. Так как содержимое счетчика меньше семи то сигналы на выходах 14 анализа.отсутствуют.

На сумматоре 9 по модулю два производится проверка правильности

0 считывания очередной микрокоманды

путем суммирования по модулю два адрес.г микрокоманды с выходов регистра 20 и контрольного разряда с выхода 59 регистра 27.микрокоманды.

5 При неправильном считывании

сумма получается четной и на выходе появится сигнал. При правильном считывании сигнала на выходе не будет.

На сумматоре 15 по модулю два производится проверка правильности

0 формирования микрокоманды путем суммирования по модулю два всех ее . разрядов. Если микрокоманда неискажена на выходе сумматора 15 по модулю два сигнал отсутствует и наоборот.

0 через элемент И 49, элемент И 36 :. .на вход элемента ИЛИ 12 и элемента И 38. При этом счетчик 13 обнуляется, группа элементов И 24 открывается по второму управляюще5. му ВХОДУ, и сигналы микроопераций .с выходов 61 регистра 27 микрокйманды поступают на выходы 25 микроопераций устройства. Сигнал с выхода элемента И 38 поступает через элемент И 28 на управляющий

0 вход блока 23 формирования адреса. При этом адрес очередной микрокоманды с выходов блока 23 формиро. вания адреса поступает через группу элементов ИЛИ 19 в регистр 20

5 адреса и записывается в нем.

С приходом очередного тактового импульса первой фазы на вход 53 устройства И.З блока 21 памяти микрокоманд считывается очередная микрокоманда и микропрограммное устройство функционирует аналогично описанному выше алгоритму.

После выполнение последней микрокоманды микропрограммы, на вход

С 17 устройства поступает сигнал Пуск, По этому сигналу код очередной операции с группы входов 16 устрой.с.тва поступает через группу элементов И 18, группу элементов ИЛИ 19 на регистр 20 и записывается

в нем.

Далее устройство функционирует .аналогично описанному выше алгоритму.

Если после считывания очередной

5 микрокоманды .из блока 21 памяти ми.крокоманд в регистр 27 микрокома ды, либо сумматор 9 по модулю два, либо сумматор 15 по модулю два обнаружит искажение микрокоманды, то на выходе элемента И 10 появляется сигнал.. При поступлении тактового импульса второй фазы с входа 50 устройства через элемент И 49 на выхо де элемента и 29 появляется сигнал а на выходе элемента И 36 нет. Сиг нал. с выхода элемента И 29 поступает на первый вход элемента И 7. Так как на втором входе элемента И 7 сигнал отсутствует, то сигнал на его выходе не появляется. Так как на выходе элемента И 36с нал отсутствует, то группа элемент И 24 закрыта по первому управляюще входу и на управляющий вход блока формирования адреса сигнал не поступает. При этом код микроопераци на выходы 25 устройства не подаетс а адрес очередной микрокоманды с выходов блока 23 формирования адреса не передается в регистр 20 адреса, и его содержимое не изменя ется. С поступлением следующего такто вого импульса первой фазы с входа 53 устройства, по описанному выше алгоритму, из блока 21 памяти микрокоманд повторно считывается эта же микрокоманда и записывается в регистр 27 микрокоманды. Содержани счетчика 13 увеличивается на единицу. . Далее, аналогично описанному выш алгоритму, она проверяется на неискаженность суг в иаторами 9 и 15 ПО-модулю два. Если сумматоры 9 и 15 по модулю два не обнаружат искажения микрокоманды, то сигнал на выходе элемента ИЛИ 10 отсутствует При поступлении очередного тактового второй фазы с вход 50 устройства на выходе элементов И 36 и 38 появляются сигналы, по которым сигналы микроопераций поступают с регистра 27 микрокоманда на выходы 25 микроопераций устройства, адрес очередной 1инкрокоманды передается в регистр 20 адреса с выходов блока 23 формирования адреса, счетчик 13 устанавливается в нулевое состояние. С приходом очередного тактового импульса первой фазы на вход 53 устройства осуществляется считывание из блока 21 памяти микрокоманд по адресу, записанному в регистре 20 адреса, очередной микрокоманды и обработка ее по описанному выше алгоритму. Если же при повторном считывании микрокоманды сумматоры 9 и 15 по модулю два снова обнаружат искажение микрокоманды, то устройство функционирует аналогично функционированию при обнаружении искажения микрокоманды при первом ее считывании. Если в течение семи повторных считываний микрокоманды из первого блока 21 памяти ее искажение не исчезает, то в устройстве производится идентификация отказа ячейки памяти блока 21 памяти и устройство переходит в третий режим работы. При этом содержимое счетчика 13 равно семи и на выходе элемента ИЛИ 10 существует высокий потенциал, то с приходом тактового импульса второй фазы на вход 50 устройства на выходе элемента И 7 появляется сигнал, который поступает на единичный .вход триггера 40, переводя его в единичное состояние, а также через четвертый .коммутатор 1, открытого по первому входу сигналом с инверсного выхода триггера 2, поступает на счетный вход триггера 2 и устанавливает его в единичное состояние. Сигнал с прямого выхода триггера 2 увеличивает содержимое счетчика на единицу при этом содержимое счетчика становится равным восьми и поступает на управляющий, вход блока 3 памяти микрокоманд. При этом из блока 3 памяти микрокоманд считывается микрокоманда - эталон отказавшей микрокоманды и записывается в регистр 4 и в регистр 27 микрокоманды. Во время считывания микрокоманды - эталона, которое может быть больше интервала времени между моментами появления на входах 53 и 50 тактовых импульсов первой и второй фазы, сигналы на управляющие входы блока 23 формирования адреса и группы элементов И 24 блокируются путем закрытия по второму входу элемента И 38 сигналом с первого выхода блока 14 анализа. После записи микрокоманды - эталона в регистр 4 на выходе элемента ИЛИ 5 появляется сигнал. При поступлении очередного тактового импульса фазы на вход 53 устройства на выходе элемента И 6 появляется сигнал, который поступает на единичный вход триггера 8 и устанавливает его в единичное состояние. С поступлением тактового импульса второй фазы на вход 50 устройства на выходе коммутатора 1 формируется сигнал, переводящий триггер 2 в нулевое состояние и на выходе 51 в единичное состояние, если микрокоманда - эталон считана из блока памяти 3 микрокоманд без искажений (сигнал на выходе элемента ИЛИ 10 отсутствует ).. С поступлением тактового импуль са первой фазы на вход 53 устройCTfla на выходе элемента И 46 появляется сигнсш, который поступает на входы 65 и 68 записи блока 35 памяти и блока 43 памяти соответственно, на элемент ИЛИ 39 и на элемент 30 задержки.

При этом в блоке 35 памяти микрокоманд записывается микрокоманда эталон отказавшей микрокоманды с выходов регистра 27 микрокоманды п адресу, формируемому счетчиком 32. В блок 43 памяти записывается адрес, по которому микрокоманда.- эт лов записана в блок 35 памяти микрокоманд. Эта адресная информация поступает с выходов счетчика 32 на информационные входы 69 блока. 43 памяти и записывается по адресу, поступакидему на адресные входы67 блока 43 памяти с выходов регистра 20 адреса.

После записи информации в блоки 35 и 43 триггеры 40, 51 и 8 сигналом, поступающим на их нулевые входы обнуляются, .а содержимое счетчика 32 увеличивается на единицу, формируя таким образом адрес следующей свободной ячейки памяти блока 35 памяти. С приходом очередного тактового импульса первой фазы на вход 53 устройства из блока 21 памяти микрокоманд считывается очередная микрокоманда и устройство функционирует аналогично описанному выше алгоритму,.

Если микрокоманда - эталон отказавшей микрокоманды при считывании из блока 3 памяти микрокоман записывается регистр 27 микрокоман с искажениями, то на элементе ИЛИ 10 появляется сигнал. При этом сигналы микроопераций на выходе 25 микроопераций устройства не поступают, адрес очередной микрокоманды с выходов блока 23 формирования адреса 23 на регистр 20 адреса не поступает, сигнал на выходе элемента И 38 отсутствует.

С поступлением тактового импульса второй фазы на вход 50 устройства на выходе коммутатора 1 формируется сигнал, переводящий триггер 2 в единичное состояние. При этсм из блока 3 памяти микрокоманд микрокоманда - эталон отказавшей ФIKpoкoмaнды считывается повторно, в счетчик 13 записывается едшница (его содержимое становится равным девяти ). Далее микропрограммное устройство функционирует анешогично первому считыванию микрокоманды эталона из блока 3 памяти микрокоманд.

Если при повторном считывании микрокоманда - эталон не искажена, то она обрабатывается аналогично обработке неискаженной микрокоманд при первом ее считывании. Если при

повторном считывании в регистр 27 микрокоманд снова записана искаженная микрокоманда, то она считывается из блока 3 памяти микрокоманд третий раз. При этом микропрограммное устройство управления функционирует аналогично как при первом и втором ее считывании.

Если в течение сами, считываний микрокоманда - эталон записывает0ся в регистр микрокоманды 27 с искажением, то содержимое счетчика

13становится равным четырнадцати. При этом на втором выходе блока

14анализа появляется сигнал, идентифицирующий наличие отказа в уст5ройстве . Этот сигнал поступает через элемент ИЛИ 57 на выход 58 отказа устройства и запрещает выдачу на схему тактовых импульсов первой и второй фазы через элементы

0

И 49 и 52.

Отказ устройства наступает также, когда число отказавших микрокоманд превышает определенное число ячеек блока 35 памяти микроко5манд.

Если количество отказавших микрокоманд становится равным заданному числу, то на выходе дешифратора 56 появляется сигнал, иденти0фицирующий отказ микропрограммного устройства управления.

При повторных обргицениях в процессе выполнения микропрограммы к отказавшим микрокомандам, для которых в блоке 35 памяти микрокоманд

5 записаны Микрокоманды - эталоны , устройство функционирует следующим образом.

При поступлении тактового импульса первой фазы на вход 53 уст0ройства из блока 21 памяти микрокоманд и блока 43 памяти параллельно считывается информация и записывается соответственно в регистр 27 микрокоманды и в регистр 44.

5 При этом в регистр 44 записываетг 7я код адреса микрокоманды -эталона отказавшей микрокоманды, хранящейся в блоке 35 памяти микрокоманд (третий режи работы устройства) .

0

При этом на выходе элемента ИЛИ 48 появляется сигнал (ъ регист ре 44 записан ненулевой код ). Этот сигнал блокирует выдачу информации

5 через группу элементов И 24. Форквфование сигнало на выходах элементов И 29, 36 и 42 разрешает формирование (жгналов на выходах группы элементов И 45 и на выходе эле0мента И 47.

Очередной тактовый импульс первой фазы формирует на выходе элемента И 47 сигнал, по которому из блока 35 памяти микрокоманд по адресу, поступающему на его адресные

5

ВХОДЫ 63 с выходов группы элементов И 45 через группу элементов ИЛИ 34 считывается микрокоманда - эталон отказавшей микрокоманд и записывается в регистр 27 микрокоманды.

Сигнал с выхода элемента И 47, пройдя через элемент 54 задержки и элемент ИЛИ 55, установит в нулевое состояние, pentстр 44.

Далее устройство функционирует аналогично как в первом, втором и третьем режимах работы.

Таким образом, избирательность при обновлении информации, т.е. замена при искажении одной из микрокоманд сегмента не всего сегмента микрокоманд, а только отказавшей микрокоманды микрокомандой эталоном и последующее ее использование вместо отказавшей позволяет

существенно повысить быстродействие микропрограммного устройства управления.

Кроме того, выполнение вместо отказавших микрокоманд соответствую тих им микрокоманд - этгшонов, храняишхся в третьем блоке памяти микрокоманд позволяет существенно повысить отказоустойчивость функционирования микропрограммного устройства управления, позволяет использовать его в системах с накоплением отказов.

Применение предлагаемого устг ройства управления в качестве .микропрограммного устройства управления, позволит повысить быстродействие и отказоустойчивость последних.

70

d

Л

77

& 75

1

1016782

7J

7г

76

Фаг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Продольно сбалансированное рессорное подвешивание тележки железнодорожного подвижного состава | 1987 |

|

SU1444175A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-07—Публикация

1981-12-10—Подача