11

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях в системах автоматического управления.

Целью изобретения является расширение класса решаемьтх задач за счет возможности вычисления дискретных ортогональных полиномов Лежандра вто рого порядка.

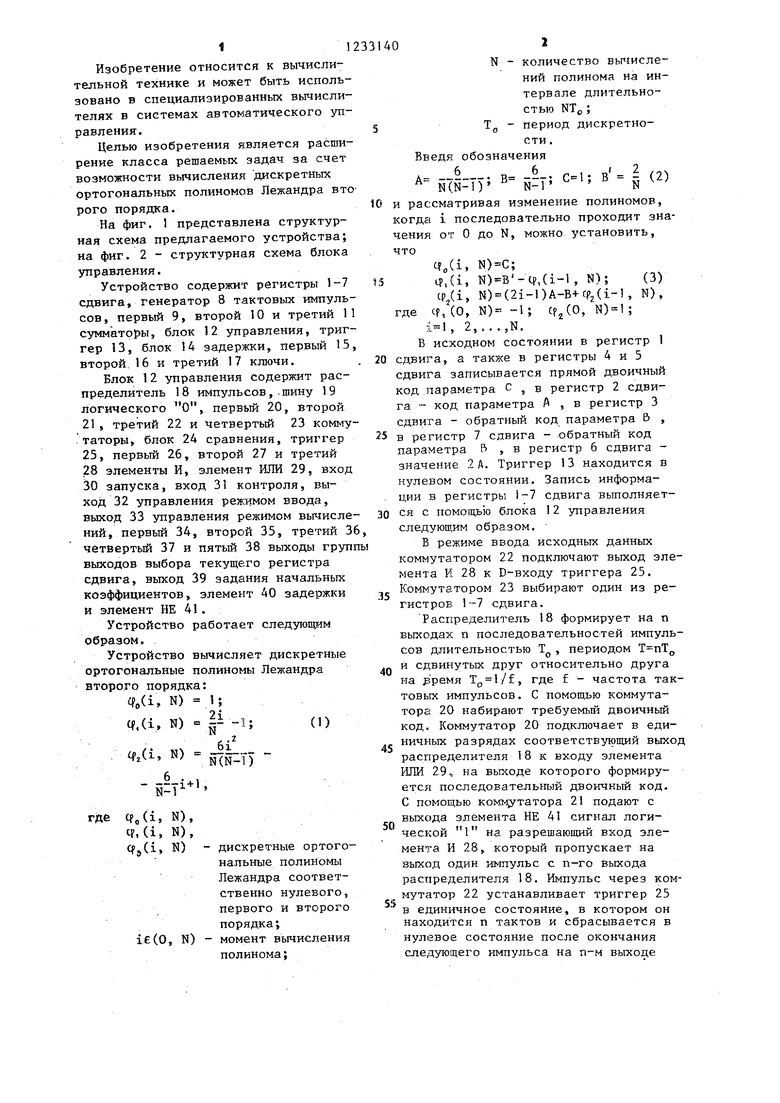

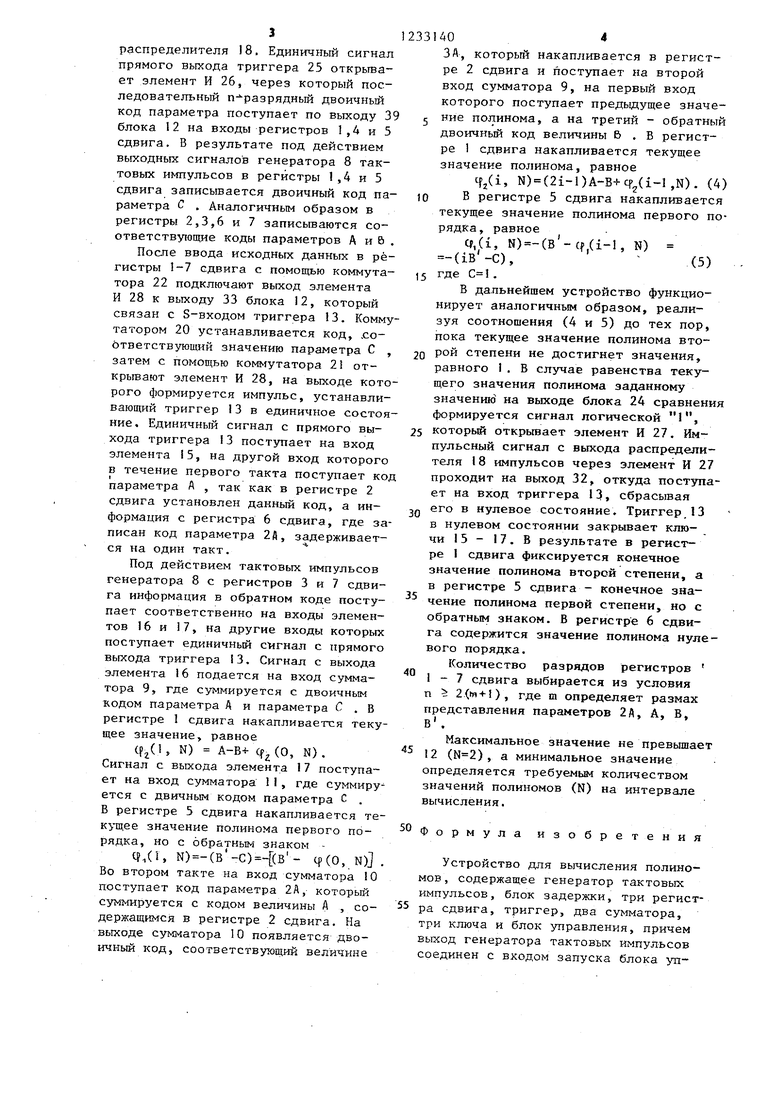

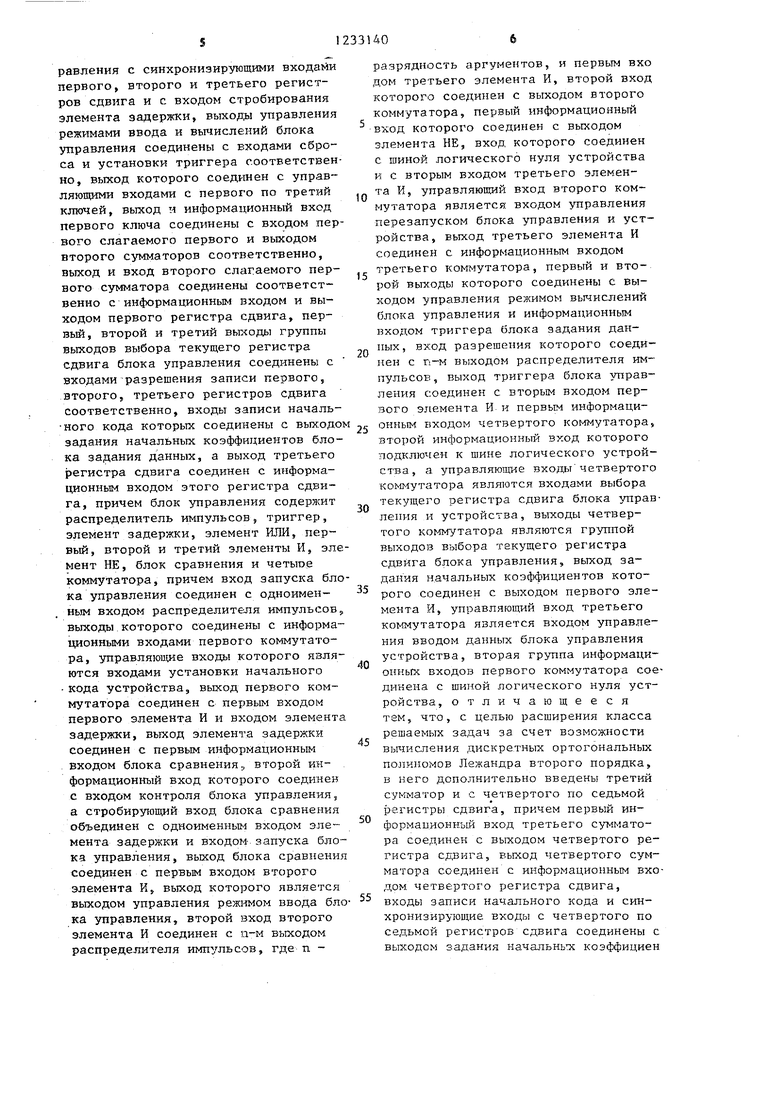

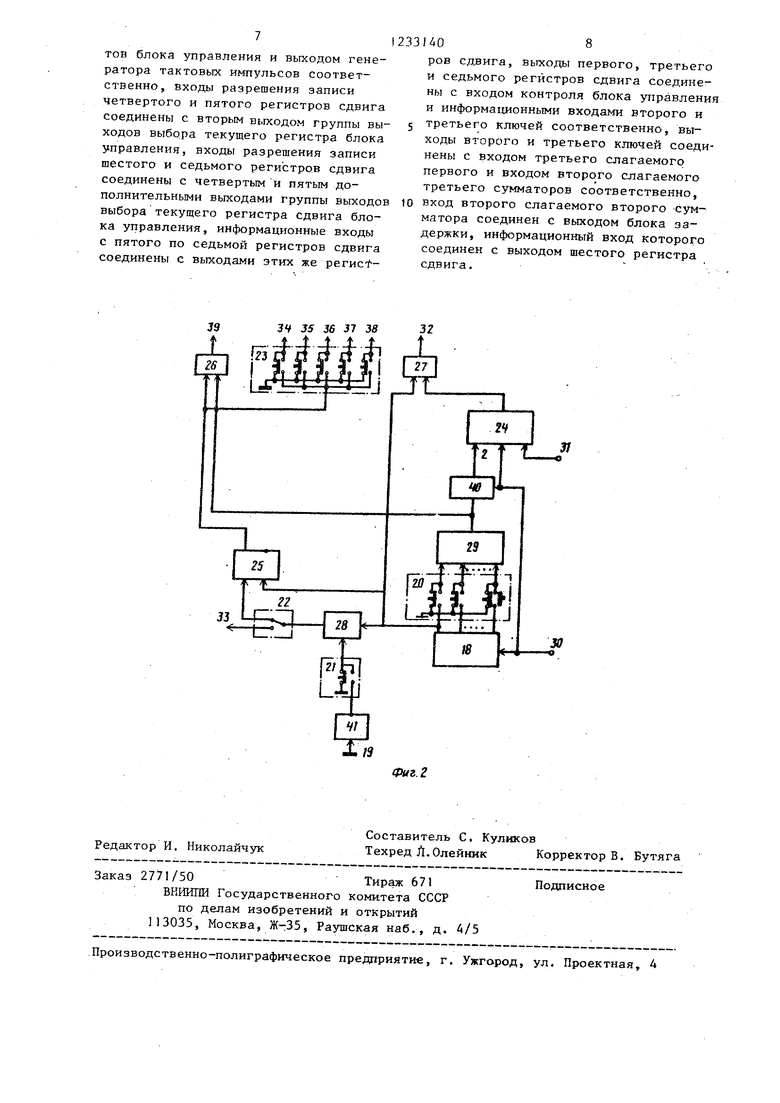

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока управления,

Устройство содержит регистры 1-7 сдвига, генератор 8 тактовых импульсов, первый 9, второй 10 и третий И сумматоры, блок 12 управления, триггер 13, блок 14 задер:яжи, первый 15 второй. 16 и третий 17 ключи.

Блок 12 управления содержит распределитель 18 импульсов,.шину 19 логического О, первый 20, второй 21, третий 22 и четвертьй 23 комму- .таторы, блок 24 сравнения, триггер 25, первый 26, второй 27 и третий 28 элементы И, элемент ИЛИ 29, вход 30 запуска, вход 31 контроля, выход 32 управления режимом ввода, выход 33 управления режимом вычислений, первый 34, второй 35, третий 36 четвертый 37 и пятый 38 выходы групп выходов выбора текущего регистра сдвига, выход 39 задания начальньпс коэффициентов, элемент 40 задержки и элемент НЕ 41,

Устройство работает следующим образом.

Устройство вычисляет дискретные ортогональные полиномы Лежандра второго порядка:

(О

где

N) нальные полиномы Лежандра соответственно нулевого, первого и второго порядка;

момент вычисления полинома;

;5

0

5

0

5

N - количество вьпшсле- ний полинома на интервале длительностью NTj,;

Tg - период дискретности. Введя обозначения

Й(1-Т)

и рассматривая изменение полиномов, когда i последовательно проходит значения от о до N, можно установить, что

, N)C;

if,(i, N)B -CF,(i-l, N); (3)

tp,{i, N) (2i-l)A-B+4-2(1- N),

где

1

0

5

50

55

ер/СО, N)- -1; C(,j(0, N) 1;

, 2,...,N.

В исходном состоянии в регистр сдвига, а также в регистры 4 н 5 сдвига записывается прямой двоичный код .параметра С ,, в регистр 2 сдвига - код параметра Л , в регистр 3 сдвига - обратный код параметра & , в регистр 7 сдвига - обратный код параметра Р , в регистр 6 сдвига - значение 2 А. Триггер 13 находится в нулевом состоянии. Запись информации в регистры 1-7 сдвига вьшолняет- ся с помощью блока 12 управления следующим образом.

В режиме ввода исходных данных коммутатором 22 подключают выход элемента И 28 к D-входу триггера 25. Коммутатором 23 выбирают один из ре- гистроЕ 1-7 сдвига.

Распределитель 18 формирует на п вьгходах п последовательностей импульсов длительностью Т, периодом и сдвинутых друг относительно друга на 1ремя Tp l/f, где f - частота тактовых импульсов. С помощью коммутатора 20 набирают требуемьш двоичньй код. Коммутатор 20 подключает в еди- ничньпс разрядах соответствующий выход распределителя 18 к входу элемента ИЛИ 29,, на выходе которого формируется последовательный ДВОРГЧНЫЙ код. С помощью коммутатора 2 подают с выхода элемента НЕ 41 сигнал логической 1 на разрешающий вход элемента И 28, который пропускает на выход один импульс с п-го выхода распределителя 18. Импульс через коммутатор 22 устанавливает триггер 25 в единичное состояние, в котором он находится п тактов и сбрасывается в нулевое состояние после окончания следующего импульса на п-м выходе

3

распределителя 8, Единичный сигнал прямого выхода триггера 25 открьгеа- ет элемент И 26, через который последовательный п- разрядный двоичный код параметра поступает по выходу 39 блока 12 на входы регистров 1,4 и 5 сдвига. В результате под действием выходных сигналов генератора 8 тактовых импульсов в регистры 1,4 и 5 сдвига записывается двоичный код параметра С , Аналогичным образом в регистры 2,3,6 и 7 записываются соответствующие коды параметров А и В .

Поспе ввода исходных данных в регистры 1-7 сдвига с помощью коммутатора 22 подключают выход элемента И 28 к выходу 33 блока 12, который связан с S-входом триггера 13. Коммутатором 20 устанавливается код, .соответствующий значению параметра С , затем с помощью коммутатора 21 открывают элемент И 28, на выходе которого формируется импульс, устанавливающий триггер 13 в единичное состояние. Единичный сигнал с прямого выхода триггера I3 поступает на вход элемента 15, на другой вход которого в течение первого такта поступает ко параметра А , так как в регистре 2 сдвига установлен данный код, а информация с регистра 6 сдвига, где записан код параметра 2Д, задерживается на один такт.

Под действием тактовых импульсов генератора 8 с регистров 3 и 7 сдвига информация в обратном коде поступает соответственно на входы элементов 16 и 17, на другие входы которых постзшает единичный с |гнал с прямого выхода триггера 13. Сигнал с выхода элемента 16 подается на вход сумматора 9, где суммируется с двоичньм кодом параметра А и параметра С , В регистре 1 сдвига накапливается текущее значение, равное

(f(I, N) A-B-f-Cf O N). Сигнал с выхода элемента 17 поступает на вход сумматора 1I, где суммируется с двичным кодом параметра С . В регистре 5 сдвига накапливается текущее значение полинома первого порядка, но с обратным знаком (l, N)-(B -C)-(B - q(0,N)J Во втором такте на вход сумматора 10 поступает код параметра 2А, который су1 мируется с кодом величины А , содержащимся в регистре 2 сдвига. На выходе сум1 атора 10 появляется двоичный код, соответствующий величине

33140

ЗА, которьй накапливается в регистре 2 сдвига и поступает на второй вход сумматора 9, на первый вход которого поступает предыдущее значе- 5 ние полинома, а на третий - обратный двоичный код величины В . В регистре 1 сдвига накапливается текущее значение полинома, равное

cf(i, N) (2i-l)A-B+cp(i-l,N). (4) 10 В регистре 5 сдвига накапливается текущее значение полинома первого порядка, равное

Q,(i, N)-(B -((-, N) -(1в -С), (5)

)5 где ,

В дальнейшем устройство функционирует аналогичным образом, реализуя соотношения (4 и 5) до тех пор, пока текущее значение полинома вто- 2Q рой степени не достигнет значения, равного 1. В случае равенства текущего значения полинома заданному значению на выходе блока 24 сравнения формируется сигнал логической I, 25 которьй открывает элемент И 27. Импульсный сигнал с выхода распределителя I8 импульсов через элемент И 27 проходит на выход 32, откуда постзта- ет на вход триггера 13 сбрасывая его в нулевое состояние. Триггер,13 в нулевом состоянии закрывает ключи 15 - 17, В результате в регистре 1 сдвига фиксируется конечное значение полинома второй степени, а в регистре 5 сдвига - конечное значение полинома первой степени, но с обратным знаком. В регистре 6 сдвига содержится значение полинома нулевого порядка.

Количество разрядов регистров 1 - 7 сдвига выбирается из условия п 5 2(ь1 + 1), где m определяет размах представления параметров 2Д, А, В,

в .

Максимальное значение не превышает 12 (), а минимальное значение определяется требуемьм количеством значений полиномов (N) на интервале вычисления.

30

35

40

50

Формула изобретения

Устройство для вычисления полиномов, содержащее генератор тактовых импульсов, блок задержки, три регист- ра сдвига, триггер, два сумматора, три ключа и блок управления, причем выход генератора тактовых импульсов соединен с входом запуска блока управления с синхронизирующими входами первого, второго и третьего регистров сдвига и с входом стробирования элемента задержки, выxoд)I управления режимами ввода и вычислений блока управления соединены с входами сброса и установки триггера соответственно, выход которого соединен с управляющими входами с первого по третий ключей, выход и информационный вход первого ключа соединены с входом первого слагаемого первого и выходом второго сумматоров соответственно, выход и вход второго слагаемого первого сумматора соединены соответственно с информационным входом и выходом первого регистра сдвига, первый, второй и третий выкоды группы выходов выбора текущего регистра сдвига блока управления соединены с входами разрешения записи первого, второго, третьего регистров сдвига соответственно, входы записи началь- ного кода которых соединены с выходо задания начальных коэффициентов блока задания данных, а выход третьего )егистра сдвига соединен с информационным входом этого регистра сдвига, причем блок управления содержит распределитель импульсовj триггер, элемент задержки, элемент ИЛИ, первый, второй и третий элементы И, элемент НЕ, блок сравнения и четыое коммутатора, причем вход запуска блока управления соединен с одноименным входом распределителя импульсов,, выходы которого соединены с информационными входами первого коммутатора, управляющие входы которого являются входами установки начального кода устройства, выход первого коммутатора соединен с пе1)вым входом первого элемента И и входом элемента задержки, выход элемента задержки соединен с первым информационным . входом блока сравнения., второй ин- . формационный вход которого соединен с входом контроля блока управления, а стробирующий вход блока сравнения объединен с одноименным входом элемента задержки и входом- запуска блока управления, выход блока сравнения соединен с первым входом второго элемента И, выход которого является выходом управления режимом ввода блока управления, второй вход второго элемента И соединен с п-м выходом распределителя импульсов, где и 0

5

0

5

0

5

0

5

0

5

разрядность аргументов, и первым вхо дом третьего элемента И, второй вход которого соединен с выходом второго коммутатора, первый информационный вход которого соединен с выходом элемента НЕ, вход, которого соединен с шиной логического нуля устройства и с вторым входом третьего элемента И, управляюисий вход второго коммутатора является входом управления перезапуском блока управления и устройства, выход третьего элемента И соединен с информационным входом третьего коммутатора, первый и второй выходы которого соединены с выходом управления режимом вычислений блока управления и информационным входом триггера блока задания данных, вход разрешения которого соединен с п-м выходом распределителя импульсов, выход триггера блока, управления соединен с вторым входом первого элемента И и первым информационным входом четвертого коммутатора, второй информационный вход которого подключен к шине логического устройства, а управляющие входы четвертого коммутатора являются входами выбора текущего регистра сдвига блока управления и устройства, выходы четвертого коммутатора являются группой выходов выбора текущего регистра сдвига блока управления, выход задания начальных коэффициентов которого соединен с выходом первого элемента И, управляющий вход третьего коммутатора является входом управления вводом данных блока управления устройства, вторая группа ииформаци- онньгх входов первого коммутатора соединена с шиной логического нуля устройства, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности вычисления дискретных ортогональных полиномов Лежандра второго порядка, в него дополнительно введень третий cyKiMaTOp и с четвертого по седьмой регистры сдвига, причем первый информационный вход третьего сумматора соединен с выходом четвертого регистра сдвига, выход четвертого сумматора соединен с информационным входом четвертого регистра сдвига, входы записи начального кода и синхронизирующие входы с четвертого по седьмой регистров сдвига соединены с выходом задания начальнь х коэффициен

7

тов блока управления и выходом генератора тактовых импульсов соответственно, входы разрешения записи четвертого и пятого регистров сдвига соединены с вторым выходом группы выходов выбора текущего регистра блока управления, входы разрешения записи шестого и седьмого регистров сдвига соединены с четвертЬпи и пятым дополнительными выходами группы выходо выбора текущего регистра сдвига блока управления, информационные входы с пятого по седьмой регистров сдвига соединены с выходами этих же регисФ331408

ров сдвига, выходы первого, третьего и седьмого регистров сдвига соединены с входом контроля блока управления и информационными входами второго и 5 третьего ключей соответственно, выходы второго и третьего ключей соединены с входом третьего слагаемого первого и входом второго слагаемого третьего сумматоров соответственно, 10 вход второго слагаемого второго сумматора соединен с выходом блока задержки, информационный вход которого соединен с выходом шестого регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полинома второй степени | 1982 |

|

SU1026140A1 |

| Устройство для ввода информации | 1980 |

|

SU947848A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

Редактор И, Николайчук

Заказ 2771/50Тираж 671

ВКИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель С. Куликов

Техред Л.Олейник Корректор В. Бутяга

Подписное

| Устройство для вычисления полиномов второй степени | 1980 |

|

SU920714A1 |

| Устройство для вычисления полинома второй степени | 1982 |

|

SU1026140A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-07-16—Подача