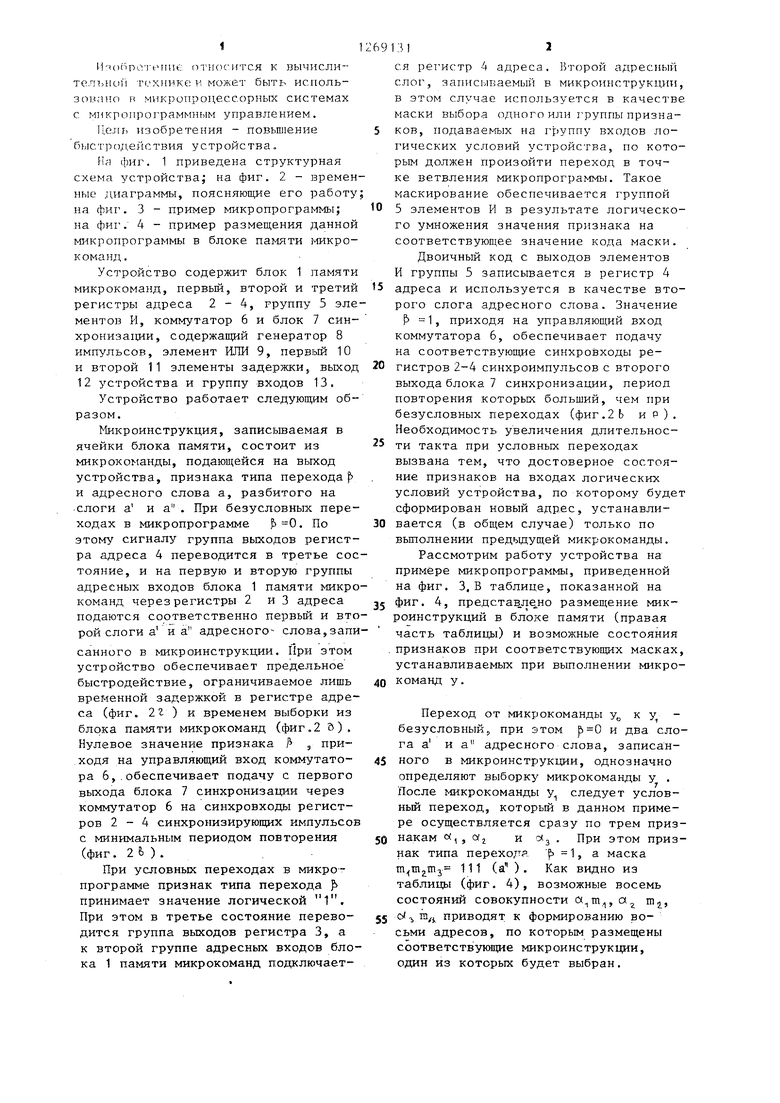

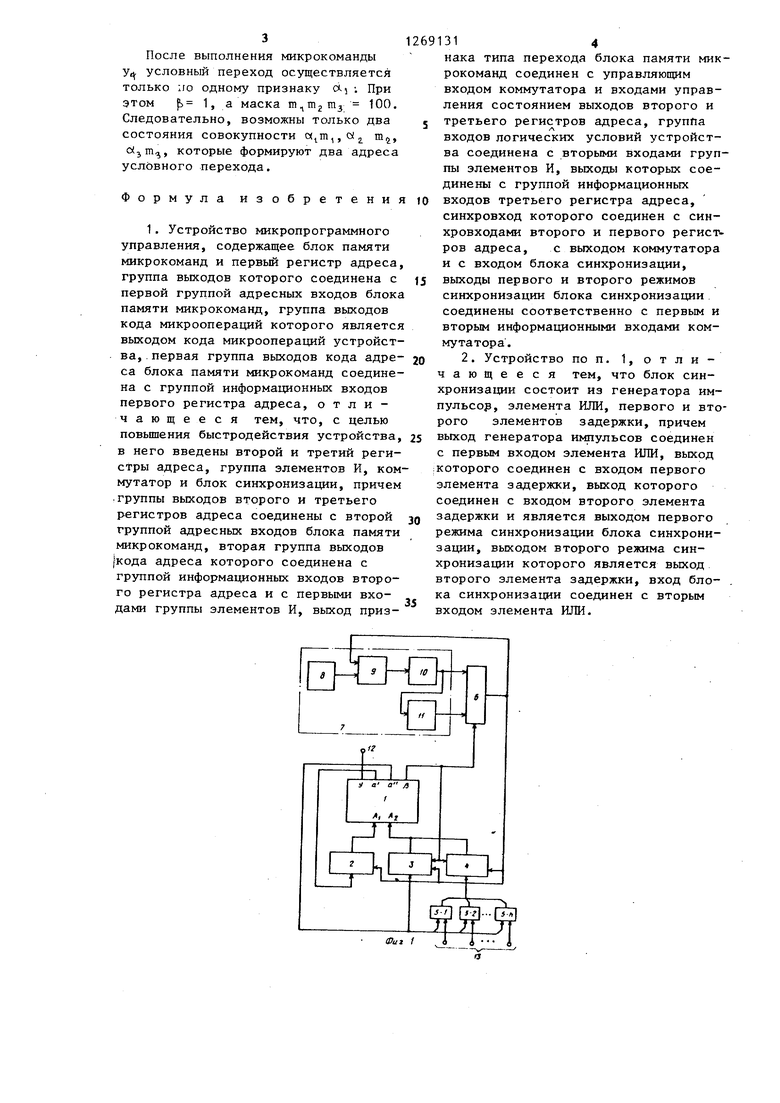

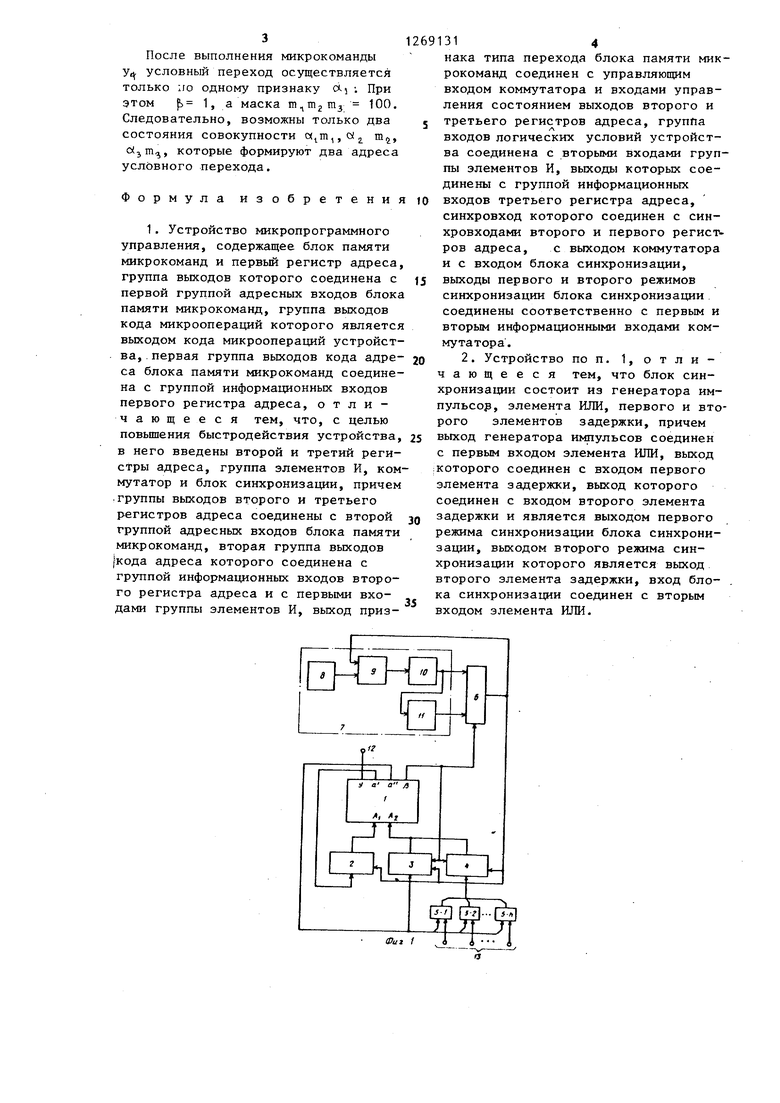

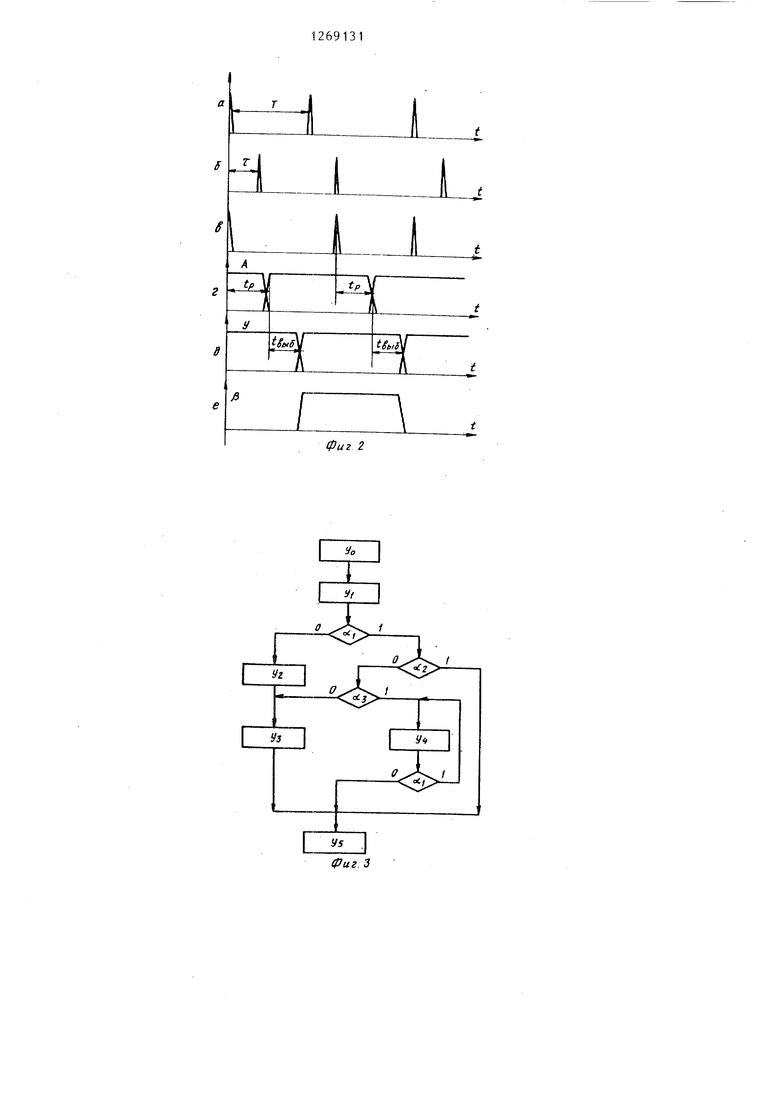

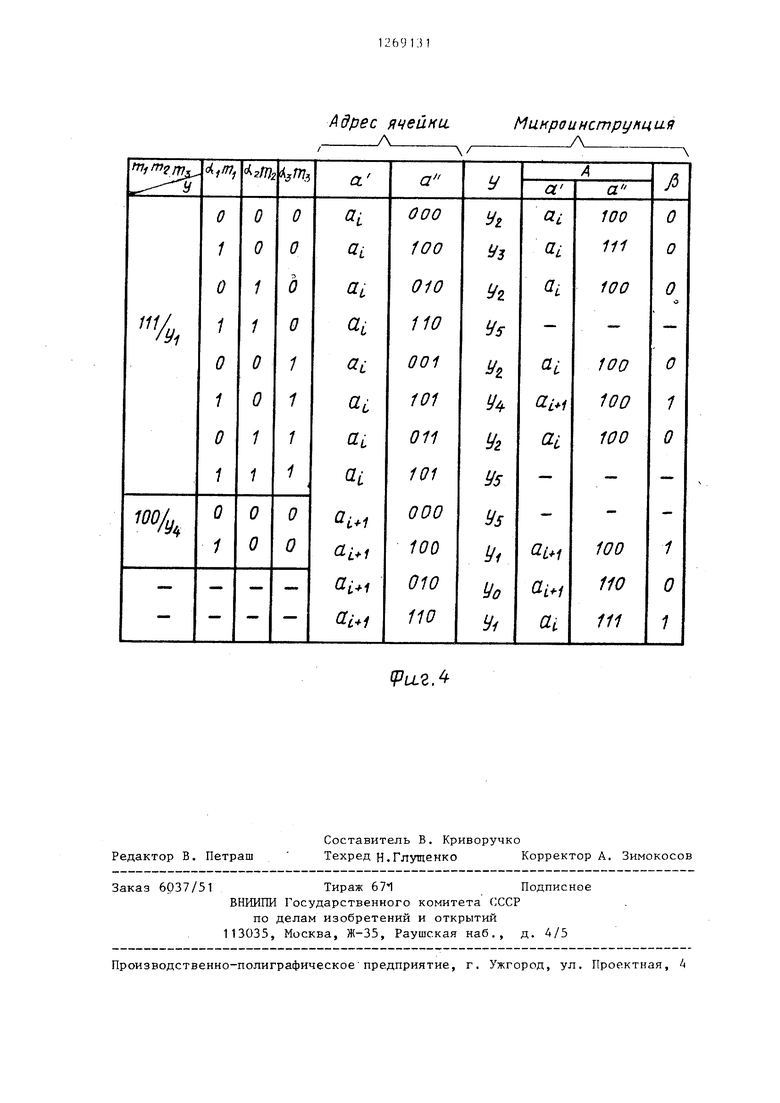

СО И-ч(1поетеггие относится к вычнсли-тельнс 1 | технике и может быть использо1. в мирсропроцессорных системах с MHKponporpaMMHfiiM управлением. Целт, изобретения - повьппение быст :1оде1 ствия устройства. Hfi ()иг. 1 приведена структурная схема устройства; на фиг. 2 - времен ные диаграмм), поясняющие его работу на фиг. 3 - пример микропрогра1 1мы; на фиг. 4 - пример размещения данной микропрограммы в блоке памяти 1чикрокоманд. Устройство содержит блок 1 памяти микрокоманд, первьш, второй и третий регистры адреса 2-4, группу 5 эле ментов И, коммутатор 6 и блок 7 синхрониза1щи, содержащий генератор 8 импульсов, элемент ИЛИ 9, первый 10 и второй 11 элементы задержки, выход 12 устройства и группу входов 13. Устройство работает следующим образом. Микроинструкция, записываемая в ячейки блока памяти, состоит из микрокоманды, подающейся на выход устройства, признака типа перехода f и адресного слова а, разбитого на слоги а и а . При безусловных пере ходах в микропрограмме f 0. По этому сигналу группа выходов регист ра адреса 4 переводится в третье со тояние, и на первую и вторую группы адресных входов блока 1 памяти микр команд через регистры 2 и 3 адреса подаются соответственно первый и вт рой слоги а и а адресного- слова,зап санного в микроинструкции. При этом устройство обеспечивает предельное быстродействие, ограничиваемое лишь временной задержкой в регистре адре са (фиг. 2i } и временем выборки из блока памяти микрокоманд (фиг.2 Э), Нулевое значение признака f , при,ходя на управляющий вход коммутатора 6,.обеспечивает подачу с первого выхода блока 7 синхронизации через коммутатор 6 на синхровходы регистров 2-4 синхронизирующих импульсо с минимальным периодом повторения (фиг. 2 Ь ) . При условных переходах в микропрограмме признак типа перехода f принимает значение логической 1, При этом в третье состояние переводится группа выходов регистра 3, а к второй группе адресных входов бло ка 1 памяти микрокоманд подключает312ся регистр 4 адреса. Второй адресный слог, записываемый в микроинструкции, в этом случае используется в качестве маски выбора одного или группы признаков, подаваемых на группу входов логических условий устройства, по которым должен произойти переход в точке ветвления микропрограммы. Такое маскирование обеспечивается группой 5 элементов И в результате логического умножения значения признака на соответствующее значение кода маски. Двоичный код с выходов элементов И группы 5 записывается в регистр 4 адреса и используется в качестве второго слога адресного слова. Значение Р 1, приходя на управляющий вход коммутатора 6, обеспечивает подачу на соответствующие синхровходы регистров 2-4 синхроимпульсов с второго выхода блока 7 синхронизации, период повторения которых больший, чем при безусловных переходах (фиг.2 Ь и Р) . Необходимость увеличения длительности такта при условных переходах вызвана тем, что достоверное состояние признаков на входах логических условий устройства, по которому будет сформирован новый адр.ес, устанавливается (в оба(ем случае) только по выполнении предыдущей микрокоманды. Рассмотрим работу устройства на примере микропрограммы, приведенной на фиг. 3. В таблице, показанной на фиг. 4, представлено размещение микроинструкций в блоке памяти (правая часть таблицы) и возможные состояния признаков при соответствующих масках, устанавливаемых при выполнении микрокоманд у. Переход от микрокоманды у к у безусловный5 при этом и два слога а и а адресного слова, записанного в микроинструкции, однозначно определяют вЕлборку микрокоманды у . После микрокоманды у следует условный переход, который в данном примере осуществляется сразу по трем признакам «, , o(i и . При этом признак типа перехо/тя. 1, а маска 111 (а ) . Как видно из таблицы (фиг. 4), возможные восемь состояний совокупности ,,, а т, Ы приводят к формированию восьми адресов, по которым размещены соответствуюище микроинструкции, один из которых будет выбран. После выполнения микрокоманды у условный переход осуществляется только ;ю одному признаку dj ; При т, - 100. Следовательно, возможны только два состояния совокупности m, o(jm, которые формируют два адреса условного перехода. Формула изобретения 1. Устройство микропрограммного управления, содержащее блок памяти микрокоманд и первый регистр адреса группа выходов которого соединена с первой ГРУППОЙ адресных входов блока памяти микрокоманд, группа выходов кода микроопераций которого является выходом кода микроопераций устройства, .первая группа выходов кода адреса блока памяти микрокоманд соединена с группой информационных входов первого регистра адреса, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены второй и третий регистры адреса, группа элементов И, ком мутатор и блок синхронизации, причем .группы выходов второго и третьего регистров адреса соединены с второй группой адресных входов блока памяти микрокоманд, вторая группа выходов кода адреса которого соединена с группой информационных входов второго регистра адреса и с первыми входами группы элементов И, выход признака типа перехода блока памяти микрокоманд соединен с управляющим входом коммутатора и входами управления состоянием выходов второго и третьего регистров адреса, группа входов логических условий устройства соединена с вторыми входами группы элементов И, выходы которых соединены с группой информационных входов третьего регистра адреса, синхровход которого соединен с синхровходами второго и первого регис-рров адреса, с выходом коммутатора и с входом блока синхронизации, выходы первого и второго режимов синхронизации блока синхронизации соединены соответственно с первым и вторым информационными входами коммутатора. 2. Устройство по п. 1, отличающееся тем, что блок синхронизации состоит из генератора импульсор, элемента ИЛИ, первого и второго элементов задержки, причем выход генератора И1 ульсов соединен с первым входом элемента ИЛИ, выход KOTOporo соединен с входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и является выходом первого режима синхронизации блока синхронизации, выходом второго режима синхронизации которого является вькод второго элемента задержки, вход блока синхронизации соединен с вторЬЕМ входом элемента ИЛИ.

±1I

9

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1200294A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1310815A1 |

| Микропроцессор | 1983 |

|

SU1140126A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных системах с микропрограммным управлением. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок памяти микрокоманд, три регистра адреса, группу элементов И, коммутатор и блок синхронизации. Цель изобретения достигается .за счет одновременной обработки нескольких логических условий в устройстве. 1 з.п. ф-лы, 4 Ш1.

Адрес ячейни.

Ми и рои н струп ц и я

Л

л

IPLL2A

| Майоров С.А., Новиков Г.И | |||

| Структура ЭВМ.-Л.: Машиностроение, 1979, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Там же, с | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1986-11-07—Публикация

1985-05-07—Подача