1 13

Изобретение от-носится к вычислительной технике, в частности к микропроцессорам с микропрограммным управлением.

Цель изобретения - увеличение

быстродействия устройства.

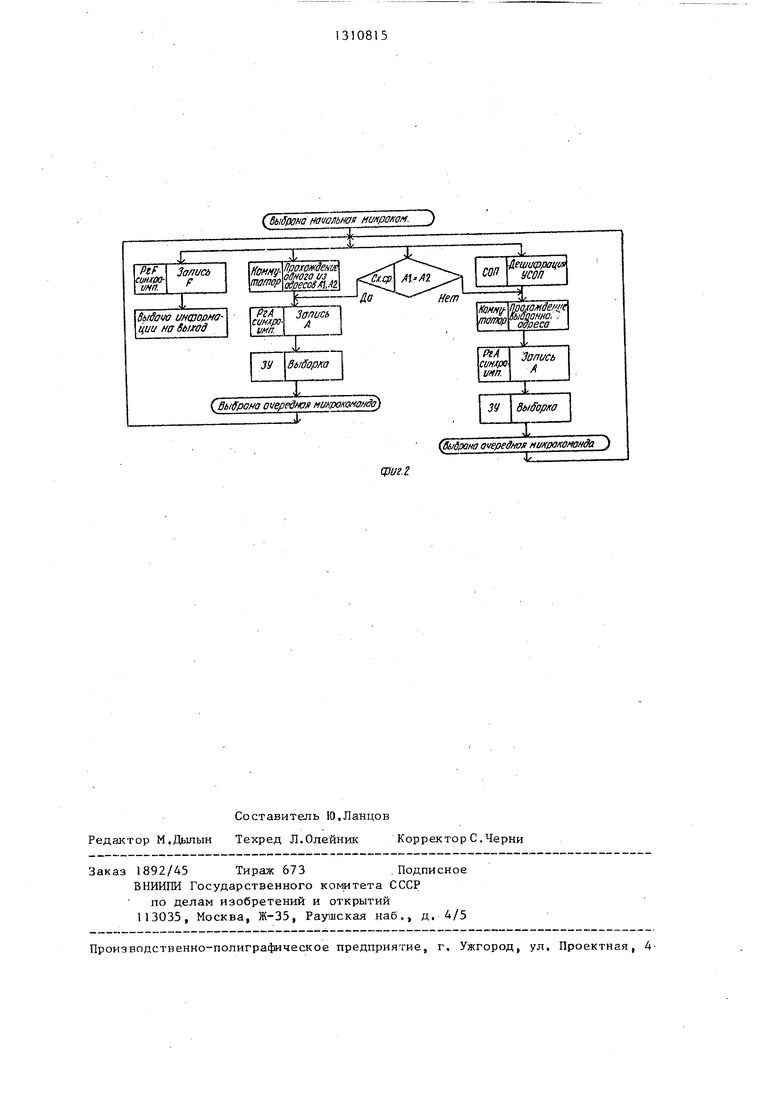

На.фиг.1 представлена функциональная схема устройства; на фиг.2 - алгоритм функционирования устройства.

Устройство (фиг. О содержит ре- гистр адреса, блок 2 памяти микропрограмм, регистр 3 микроопераций, блок 4 анализа условий, коммутатор 5, схему 6 сравнения и генератор 7 тактовых импульсов.

Блок 4 анализа условий содержит дешифратор 8, группу 9 элементов И, элемент ИЛИ 10 и инвертор 11.

Устройство работает следующим образом.

В исходном положении регистр 1 адреса обнуляется, в результате происходит выборка по нулевому адресу начальной микрокоманды из блока 2 памяти микропрограмм. С момента выдачи этой микрокоманды начинается первый такт работы устройства. После микроинструкции F записывается в регистр 3 микроопераций, код признака УСОП поступает на управляющий вход блока 4. Старшие и младшие разряды адреса А1 и А2 поступают на коммутатор 5 и схему 6 сравнения, которая управляет генератором 7.

С началом такта происходит декоди рование кода УСОП в дешифраторе 8, прохождение разрядов адреса А1 или А2 через коммутатор 5, процедура сравнения А1 и А2 в схеме 6 и запись поля F в регистр 3. Далее алгоритм функционирования зависит от типа перехода к следующей микрокоманде.

При безусловном переходе схема 6 вырабатывает сигнал l ()р по которому генератор 7 сразу выдает импульс на синхровход регистра 1. В регистр заносится очередной адрес А следующей микрокоманды (), по которому в блоке 2 начинается ее выборка.

При условном переходе схема 6 вы- рабатьюает О (), по которому генератор 7 выдает синхроимпульсы на регистр 1 с задержкой, с учетом за- держки формирования достоверных сиг5

81

5

0

0

5 0

5 0

55

52

налов блоком 4 и задержки на прохождение А1 или А2 через открытое плечо коммутатора 5. При состоянии признака. открывается плечо для А1, при ПР 1 - для А2/А1 либо А2 заносится в регистр 1; по зтому адресу в блоке 2 начинается выборка. Выборка i-ro признака происходит путем дешифрации кода УСОП в дешифраторе 8 и выдачи разрешающего сигнала на i-1 элемент И (9-i). Далее сигнал распространяется через элемент ИЛИ 10 и инвертор 11.

Формула изобретения

Микропрограммное устройство управления, содержащее регистр адреса, регистр микроопера1Ц1й, блок памяти микропрограмм , коммутатор, блок анализа условий и генератор тактовых импульсов, причем первый и второй выходы блока анализа условий соединены с первьм и вторым управ-ляющими входами коммутатора, выход поля микроопераций блока памяти микропрограмм соединен с информационным входам регистра микроопераций, выход которого является выходом микроопераций устройства, входы условий устройства являются информационными входами блока анализа условий, управляющий вход которого соединен с выходом поля условий блока памяти микропрограмм, выход старших разрядов адреса которого соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом младших разрядов адреса блока памяти микропрограмм, адресный вход которого соединен с выходом регистра адреса, выходы первого и второго режимов синхронизации генератора тактовых импульсов соединены соответственно с синхровходами регистра микроопераций и регистра адреса, отличающееся тем, что, с целью увеличения быстродействия, в него введена схема сравнения, причем выходы старших и младших разрядов адреса блока памяти микропрограмм соединены соответственно с первым и вторым входами схемы сравнения, выход которой соединен с входом запуска генератора тактовых импульсов.

HpUSHOftU

(fluff-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1295392A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1091160A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к вычислительной технике и может использоваться в микропроцессорных системах с микропрограммным управлением. Цель изобретения - увеличение быстродействия. Устройство содержит региистр адреса, блок памяти микропрограмм регистр микроопераций, блок анализа условий, коммутатор, схему сравнения и генератор тактовых импульсов. Цель изобретения достигается тем, что при безуслов}1ых переходах генератор формирует укороченную по длительно - сти серию синхроимпульсов работы устройства. . ил. (Л X :л

| Майоров С.А | |||

| , -Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| - Л.: Машиностроение, 1974, с | |||

| Эксцентричный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию и т.п. работ | 1924 |

|

SU203A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Майоров С.А | |||

| , Новиков Г.И, Структура ЭВМ | |||

| - Л,: Машиностроение, 1979, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1987-05-15—Публикация

1985-09-09—Подача