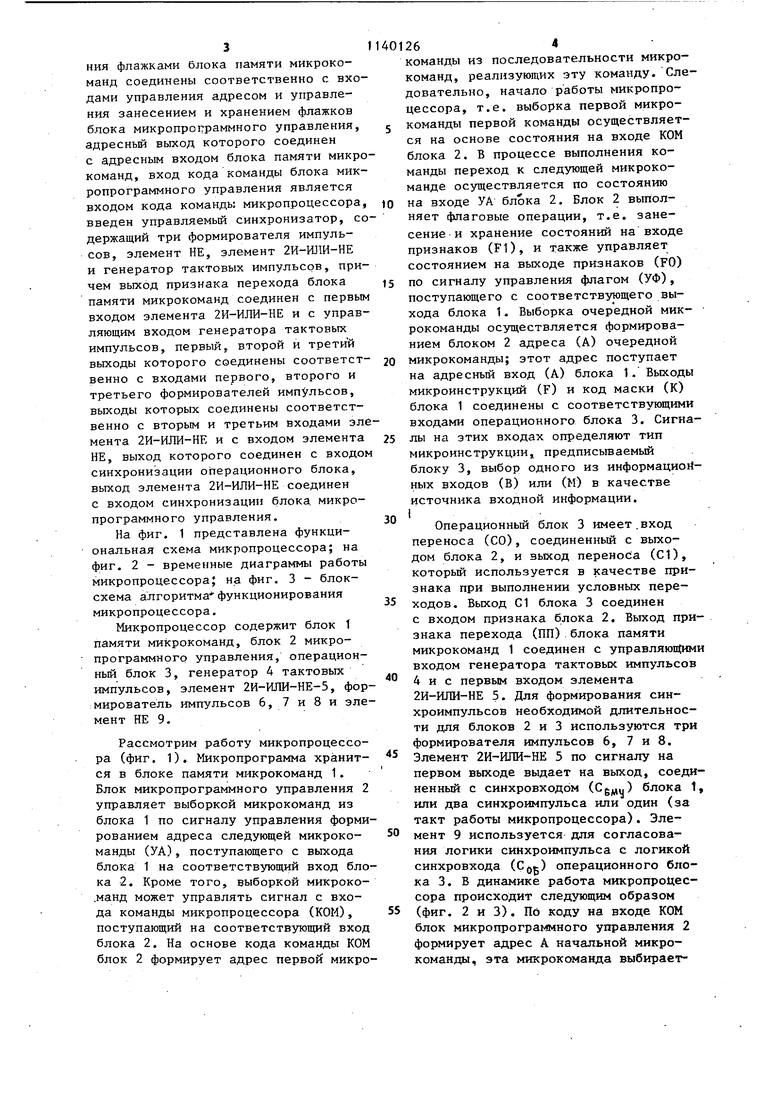

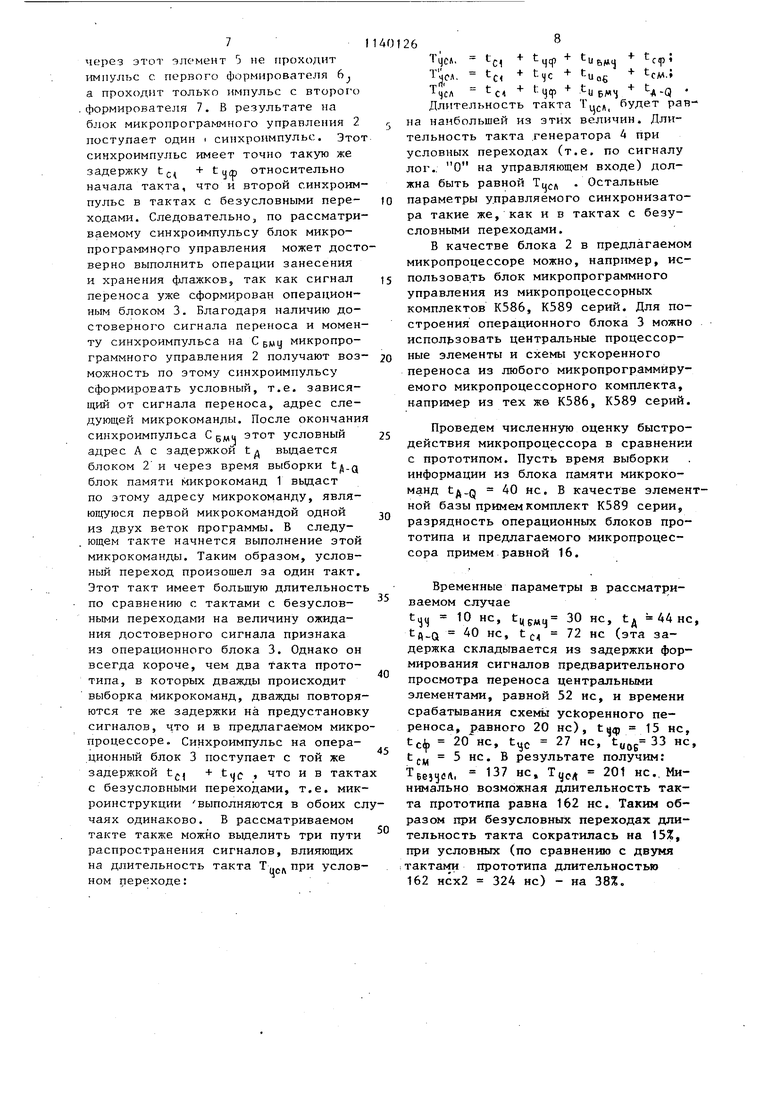

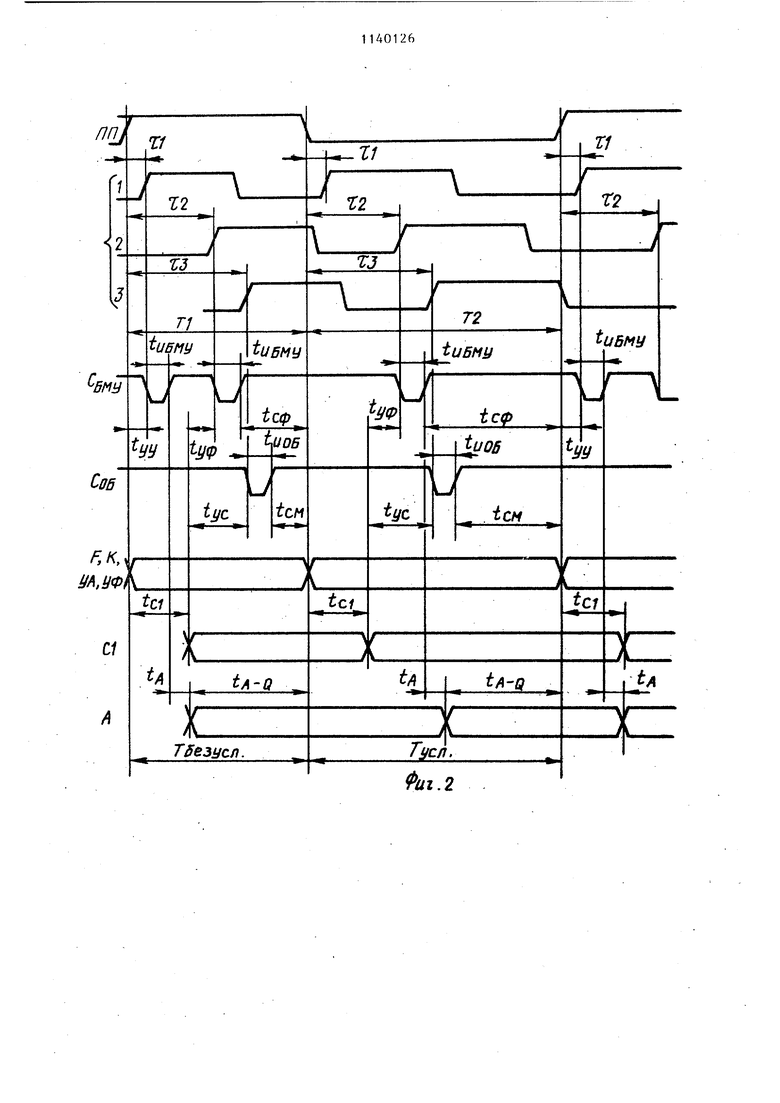

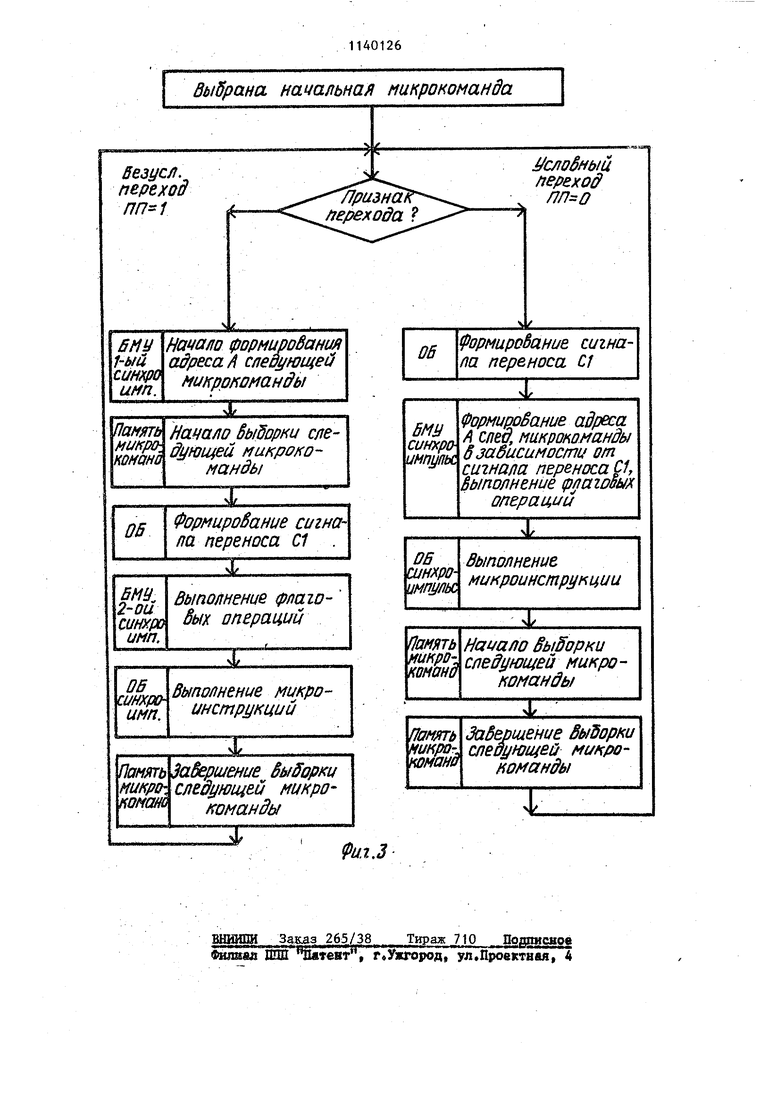

11 Изобретение относится к вычислительной технике, в частности к микро процессорным системам с микропрограм мным управлением, используемым, например, для обработки радиолокационных сигналов. Известен микропроцессор, включающий блок микропрограммного управления, блок памяти микрокоманд, операционный блок Л , В этом микропроцессоре выборка микрокоманды из блока памяти микрокоманд и выполнение этой микрокоманды операционным блоком происходит последовательно в течение такта, что увеличивает его длительность. Наиболее близким к предлагаемому является микропроцессор, содержащий блок микропрограммного управления-, блок памяти микрокоманд и операционный блок, причем выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выход признаков которого соединен с входом переноса операцион ного блока, вход кода операции которого соединен с выходом кода микроопераций блока памяти микрокоманд, выход кода маскирования которого соединен с входом маски операционного блока, выход адреса обращения и памя ти данных которого является адресным выходом микропроцессора, инфорг мационный выход микропроцессора соединен с информационным выходом операционного блока, первый и вто- рой информационные входыкоторого являются соответственно первым и. вторым информационными входами микр процессора, выходы кода управления флажками и кода управления формированием адреса следующей микрокоманды блока памяти микрокоманд соединены соответственно с входами управ ления занесением и хранением флажков и управления адресом блока микропрограммного управления, адрес.ный выход которого соединен с адрес ным входом блока памяти микрокоманд вход кода команды блока микропрограммного управления является входом кода команды мшсропроцессором. В этом микропроцессоре конвейерный регистр задерживает выбранную в текущем такте из блока памяти микрокоманд микрокоманду до начала 62 следующего такта. С другой стороны, с началом следующего такта начинается выборка очередной микрокоманды из блока памяти микрокоманд.. Таким образом, происходит частичное нало- жение во времени процедур выборки очередной микрокоманды из блока памяти микрокоманд и выполнение предыдущей микрокоманды в операционном блоке. Это сокращает длительность такта 2 . Однако в связи с тем, что выполнение микрокоманды задерживается до следующего такта, соответственно задерживается и выполнение условных переходов по результатам выполнения микрокоманды. Таким образом, в этом микропроцессоре требуется два такта на выполнение условного перехода, что приводит к увеличению времени выполнения микропрограмм и к уменьшению полезной емкости блока памяти микрокоманд, часть ячеек которого приходится заполнять пустыми микрокомандами (приходящимися на второй такт условного перехода). Кроме того, в длительность такта входит время записи информации в конвейерный регистр, что несколько увеличивает длительность такта. I . Цель изобретения - повышение быстродействия . Поставленная цель достигается тем, что в микропроцессор, содержащий блок памяти микрокоманд, блок микропрограммного управления и операционный блок, причем выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выход признаков которого соединен с входом переноса операционного блока, вход кода операции которого соединен с выходом кода микроопераций блока памяти микрокоманд, выход кода маскирования которЬго соединен с входом маски операционного блока, выход адреса обращения к памяти данных которого является адресным выходом микропроцессора, информационный выход микропроцессора соединен с информационным выходом операционного блока, первьй и второй информационные входы которого являются соответственно первым и вторым информационными входами микропроцессора, выходы кода управления формированием адреса следующей микрокоманды и кода управле3НИИ флажками блока памяти микрокоманд соединены соответственно с вхо дами управления адресом и управления занесением и хранением флажков блока микропро17раммного управления, адресный выход которого соединен с адресным входом блока памяти микр команд, вход кода команды блока мик ропрограммного управления является входом кода команды микропродессора введен управляемый синхронизатор, с держащий три формирователя импульсов, элемент НЕ, элемент 2И-ШШ-НЕ и генератор тактовых импульсов, при чем выход признака перехода блока памяти микрокоманд соединен с первы входом элемента 2И-ИЛИ-НЕ и с управ ляющим входом генератора тактовых импульсов, первый, второй и третий выходы которого соединены соответст венно с входами первого, второго и третьего формирователей импульсов, выходы которых соединены соответственно с вторым и третьим входами эл мента 2И-ИЛИ-НЕ и с входом элемента НЕ, выход которого соединен с входо синхронизации операционного блока, выход элемента 2И-ИЛИ-НЕ соединен с входом синхронизации блока микропрограммного управления. На фиг, 1 представлена функциональная схема микропроцессора; на фиг. 2 - временные диаграммы работы микропроцессора; на фиг. 3 - блоксхема алгоритма функционирования микропроцессора. Микропроцессор содержит блок 1 памяти микрокоманд, блок 2 микропрограммного управления, операционный блок 3, генератор А тактовых импульсов, элемент 2И-ИЛИ-НЕ-5, фор мирователь импульсов 6, 7 и 8 и эле мент НЕ 9. Рассмотрим работу микропроцессора (фиг. 1). Микропрограмма хранится в блоке памяти микрокоманд 1. Блок микропрограммного управления 2 управляет выборкой микрокоманд из блока 1 по сигналу управления форми рованием адреса следующей микрокоманды (УА), поступающего с выхода блока 1 на соответствующий вход бло ка 2. Кроме того, выборкой микроко.манд может управлять сигнал с входа команды микропроцессора (КОМ), поступающий на соответствующий вход блока 2. На основе кода команды КОМ блок 2 формирует адрес первой микро 264 команды из последовательности микрокоманд, реализующих эту команду. Следовательно, начало работы микропроцессора, т.е. выборка первой микрокоманды первой команды осуществляется на основе состояния на входе КОМ блока 2. В процессе выполнения команды переход к следующей микрокоманде осуществляется по состоянию на входе УА блока 2. Блок 2 выполняет флаговые операции, т.е. занесение и хранение состояний на входе признаков (F1), и также управляет состоянием на выходе признаков (FO) по сигналу управления флагом (УФ), поступающего с соответствующего выхода блока 1. Выборка очередной микрокоманды осуществляется формированием блоком 2 адреса (А) очередной микрокоманды; этот адрес поступает на адресный вход (А) блока 1. Выходы микроинструкций (F) и код маски (К) блока 1 соединены с соответствующими входами операционного блока 3. Сигналы на этих входах определяют тип никроинструкции предписываемый блоку 3, выбор одного из информациой- ных входов (В) или (М) в качестве источника входной информации. Операционный блок 3 имеет .вход переноса (СО), соединенный с выходом блока 2, и выход переноса (С1), который используется в качестве признака при выполнении условных переходов. Выход 01 блока 3 соединен с входом признака блока 2. Выход признака перехода (ПП).блока памяти микрокоманд 1 соединен с управляюпотаи входом генератора тактовых импульсов / ч и с первым входом элемента 2И-ИЛИ-НЕ 5. Для формирования синхроимпульсов необходимой длительности для блоков 2 и 3 используются три формирователя импульсов 6, 7 и 8. Элемент 2И-ИЛИ-НЕ 5 по сигналу на первом выходе вьщает на выход, соединенный с синхровходом () блока 1, или два синхроимпульса или один (за такт работы микропроцессора). Элемент 9 используется для согласования логики синхроимпульса с логикой синхровхода () операционного блока 3. В динамике работа микропроцессора происходит следующим образом (фиг. 2 и 3). По коду на входе КОМ блок микропрограммного управления 2 формирует адрес А начальной микрокоманды, эта микрокоманда выбирается из блока памяти микрокоманд 1 и оказывается на его выходах. С этого момента начинается первый такт работы микропроцессора. Такты с безусловным и условным переходами отличаются друг от друга.

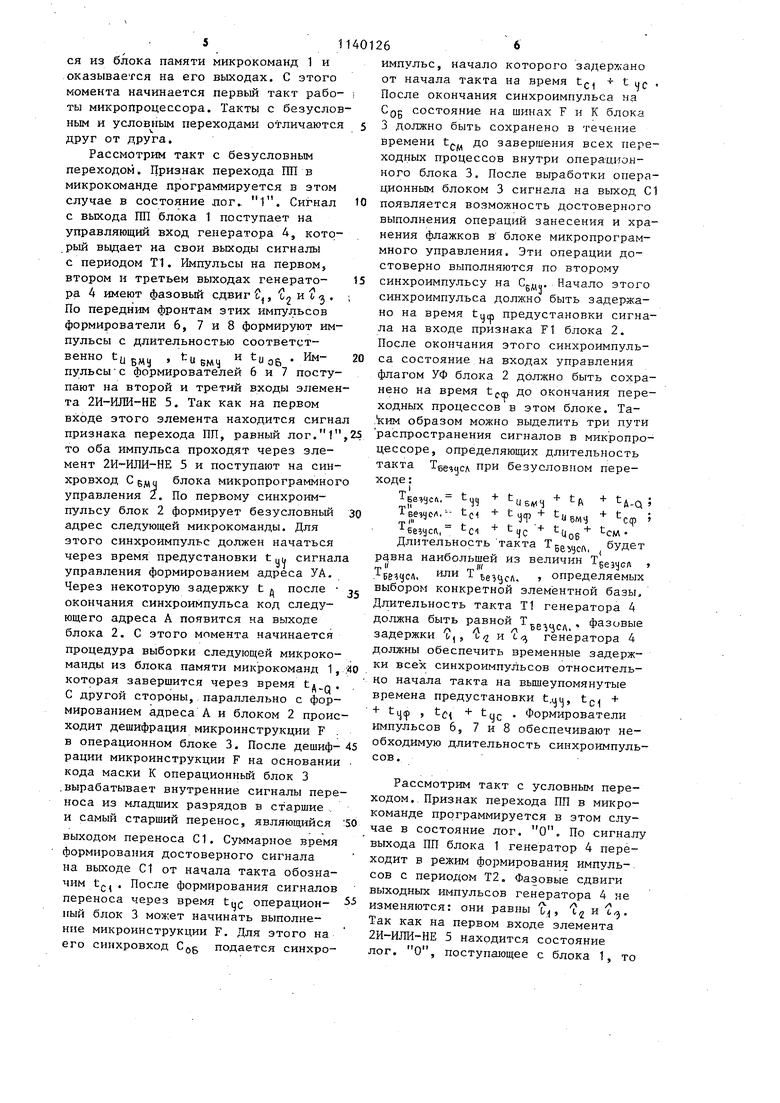

Рассмотрим такт с безусловным переходом. Признак перехода ГШ в микрокоманде программируется в этом случае в состояние лог. 1. Сигнал с выхода ПП блока 1 поступает на управляющий вход генератора 4, который выдает на свои выходы сигналы с периодом Т1. Импульсы на первом, втором и третьем выходах генератора 4 имеют фазовый сдвиг С,, и (/ . По передним фронтам этих импульсов формирователи 6, 7 и 8 формируют импульсы с длительностью соответственно tuBMD ему об пульсыс формирователей 6 и 7 поступают на второй и третий входы элемента 2И-ИЛИ-НЕ 5. Так как на первом входе этого элемента находится сигна признака перехода ПП, равный лог,1 то оба импульса проходят через элемент 2И-ИЛИ-НЕ 5 и поступают на синхровход Сем у блока микропрограммног управления 2, По первому синхроимпульсу блок 2 формирует безусловный адрес следующей микрокоманды. Для этого синхроимпульс должен начаться через время предустановки t ,, сигнал управления формированием адреса УА. Через некоторую задержку t д после окончания синхроимпульса код следующего адреса А появится на выходе блока 2. С этого момента начинается процедура выборки следующей микрокоманды из блока памяти микрокоманд 1, которая завершится через время tin.

/-, «

О другой стороны, параллельно с формированием адреса А и блоком 2 происходит дешифрация микроинструкции F . в операционном блоке 3. После дешифрации микроинструкции F на основании кода маски К операционный блок 3 .вырабатывает внутренние сигналы переноса из младших разрядов в старшие и самый старший перенос, являющийся выходом переноса С1. Суммарное время формирования достоверного сигнала на выходе С1 от начала такта обозначим t . После формирования сигналов переноса через время операционный блок 3 может начинать выполнение микроинструкции F. Для этого на его синхровход подается синхроимпульс, начало которого задержано от начала такта на время t t чс После окончания синхроимпульса на состояние на шинах F и К блока 3 должно быть сохранено в течение времени t., до завершения всех переходных процессов внутри операционного блока 3. После выработки операционным блоком 3 сигнала на выход С появляется возможность достоверного выполнения операций занесения и хранения флажков в блоке микропрограммного управления. Эти операции достоверно выполняются по второму синхроимпульсу на Cg,.. Начало этого синхроимпульса должно быть задержано на время tym предустановки сигнала на входе признака F1 блока 2. После окончания этого синхроимпульса состояние на входах управления флагом УФ блока 2 должно быть сохранено на время t(ф до окончания переходных процессовв этом блоке. Та.ким образом можно выделить три пути распространения сигналов в микропроцессоре, определяющих длительность такта Тбечисл при безусловном переходе:

ТБе.усл, ty + t(,g + tft + ;

)ел,---- t(, + ty(p+ + t ;

, Ci -ijC Uoe Длительность такта будет

наибольшей из величин Tggjucrt ,

БИусл, ™ т 6e3tjcA. J определяемых выбором конкретной элементной базы. Длительность такта Т1 генератора 4 должна быть равной Т,..,..,..,. , фазовые

Г Л nCJJl.H,

задержки с,,, L.,2 и с генератора 4 должны обеспечить временные задержки всех синхроимпульсов относительно начала такта на вьш1еупомянуть е времена предустановки t,uu, t + + tLj(p , t + t(j(. . Формирователи импульсов 6, 7 и 8 обеспечивают необходимую длительность синхроимпульсов.

Рассмотрим такт с условным переходом. Признак перехода ПП в микрокоманде программируется в этом случае в состояние лог. О. По сигналу выхода ПП блока 1 генератор 4 переходит в режим формирования импульсов с периодом 12. Фазовые сдвиги выходных импульсов генератора 4 не изменяются: они равны , t и t. Так как на первом входе элемента 2И-ИЛИ-НЕ 5 находится состояние лог. О, поступающее с блока 1, то через этот эле-мент 5 не проходит liMiiyjibc с. первого формирователя 6 а проходит только импульс с второг-о формирователя 7. В результате на блок микропрограммного упраиления 2 поступает один i синхроимпульс. Это синхроимпульс имеет точно такую же задержку t. + tllф относительно начала такта, что и второй синхроим пульс в тактах с безусловными переходами. Следовательно, по рассматри ваемому синхроимпульсу блок микропрограммного управления может дост верно выполнить операции занесения и хранения флажков, так как сигнал переноса уже сформирован операционным блоком 3. Благодаря наличию достоверного сигнала переноса и моменту синхроимпульса на С ему микропрограммного управления 2 получают возможность по этому синхроимпульсу сформировать условный, т.е. зависящий от сигнала переноса, адрес следующей микрокоманды. После окончани синхроимпульса С этот условный адрес А с задержкой tд вьщается блоком 2 и через время выборки .g блок памяти микрокоманд 1 выдаст по этому адресу микроко 1анду, являющуюся первой микрокомандой одной из двух веток программы. В следующем такте начнется выполнение этой микрокоманды. Таким образом, условный переход произошел за один такт. Этот такт имеет большую длительност по сравнению с тактами с безусловными переходами на величину ожидания достоверного сигнала признака из операционного блока 3. Однако он всегда короче, чем два такта прототипа, в которых дважды происходит выборка микрокоманд, дважды повторяются те же задержки на предустановку сигналов, что и в предлагаемом микро процессоре. Синхроимпульс на операционный блок 3 поступает с той же задержкой t t,|C « что и в такта с безусловными переходами, т,е, микроинструкции выполняются в обоих сл чаях одинаково. В рассматриваемом такте также можно вьщелить три пути распространения сигналов, влияющих на длительность такта Тц при условном переходе: ijcft, - tj,, + t + tug + t,.; Т ,,од tj., + t(jc + . - t(., + t:(jqp + ty + t.q Длительность такта будет равна наибольшей из этих величин. Длительность такта генератора 4 при условных переходах (т.е. по сигналу лог,. О на управляющем входе) должна быть равной Тцс , Остальные параметры управляемого синхронизатора такие же, как и в тактах с безусловными переходами. В качестве блока 2 в предлагаемом микропроцессоре можно, например, использовать блок микропрограммного управления из микропроцессорных комплектов К586, К589 серий. Для построения операционного блока 3 можно использовать центральные процессорные элементы и схемы ускоренного переноса из любого микропрограммируемого микропроцессорного комплекта, например из тех же К586, К589 серий. Проведем численную оценку быстродействия микропроцессора в сравнении с прототипом. Пусть время выборки информации из блока памяти микрокоманд tд.Q 40 НС. В качестве элементной базы примем комплект К589 серии, разрядность операционных блоков прототипа и предлагаемого микропроцессора примем равной 16, Временные параметры в рассматриваемом случае ty 10 НС, tцpдy 30 НС, tд Ь44нс, A-Q С, t(. 72 не (эта задержка складывается из задержки формирования сигналов предварительного просмотра переноса центральными элементами, равной 52 не, и времени срабатывания схемы ускоренного переноса, равного 20 не), tУФ 15 не, tf-ip 20 НС, 27 НС, to(jg 33 не, tjy 5 НС. В результате получим: (5Л, 137 НС. Туед 201 не,, Минимально возможная длительность такта прототипа равна 162 не. Таким образом при безусловных переходах длительность такта сократилась на 15%, при условных (по сравнению с двумя актами прототипа длительностью 162 нсх2 324 не) - на 38%.

иг.1 i -t

T1

tuffny

tuGMy

;

г

tcф

- l ijJDB

yy

Г tcM

tyc 4

«-i

r

/L

X-g

Тёезусл.

72

tuBMy

tuBMy

ic(f

tuos

ici

tA

/i-g

t

Т усл. Фиг.2 Фи.1.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1986 |

|

SU1361572A1 |

| Микропроцессор | 1985 |

|

SU1336023A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1269131A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1310815A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Микропроцессор | 1982 |

|

SU1035610A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Микропроцессор | 1982 |

|

SU1045231A1 |

МИКРОПРОЦЕССОР, содержащий блок микропрограммного управления, блок памяти микрокоманд и операционный блок, причем выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выход признаков которого соединен с входом переноса операционного блока, вход кода операции которого соединен с выходом кода микроопераций блока памяти микрокоманд, выход кода маскирования которого соединен с входом маски операционного блока, выход адреса обращения к памяти данных которого является адресным выходом микропроцессора, информационный выход микропроцессора соединен с информационным выходом операционного блока, первый и второй информационные входы которого являются соответственно первым и вторым информационными входами микропроцессора, выходы кода управления- формированием адреса следующей микрокоманды и кода управления флажками блока памяти микрокоманд соединены соответственно с входами управления адресом и управления занесением и хранением флажков блока микропрог граммного управления, адресный выход которого соединен с адресным входом блока памяти микрокоманд, вход кода команды блока микропрограммного управления является входом кода команды микропроцессора, отличающийся тем, что, с целью повы;Шения быстродействия, ок содержит управляемый синхронизатор, содержащий три формирователя ийпульсов, элемент НЕ, элемент 2И-ИЛИ-НЕ и ге(П нератор тактовых импульсов, причем выход признака перехода блока памяти микрокоманд соединен с первым входом элемента 2И-ИЛИ-НЕ и с управляющим входом генераторатактовых импульсов, первый, второй и третий выходы которого соединены соответственно с входами первого, второго и третьего формирователей импульсов, выходы которых соединены соответствш но с вторым и третьим входами элемента 2И-Ш1И-НЕ и с вхЪдом элемента НЕ, выход которого соединен с входом синхронизации операционного блока, выход элемента 2И-ИЛИ-НЕ соединен с входом синхронизации блока микропрограммного управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Березенко А.И., Корягин Л.И., Назарьян А.Р | |||

| Микропроцессорные комплекты повьппенного быстродействия, М., Радио и связь, 1981, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с | |||

| Схема обмотки ротора для пуска в ход индукционного двигателя без помощи реостата, с применением принципа противосоединения обмоток при трогании двигателя с места | 1922 |

|

SU122A1 |

Авторы

Даты

1985-02-15—Публикация

1983-01-26—Подача