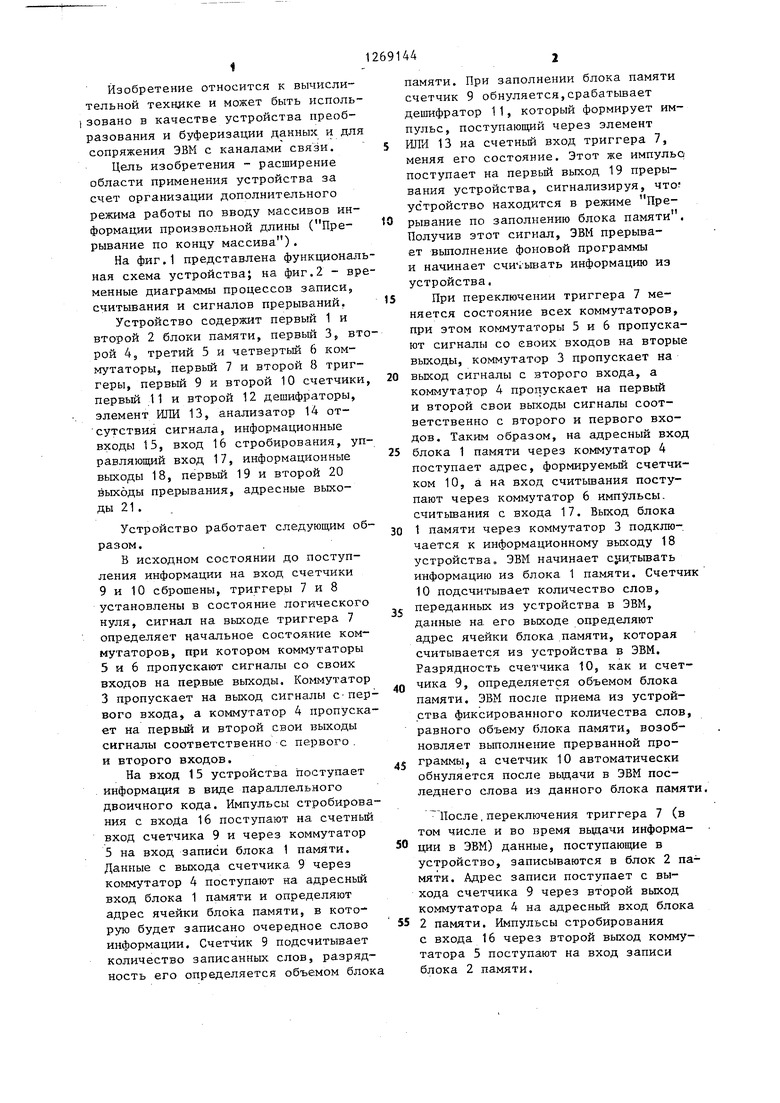

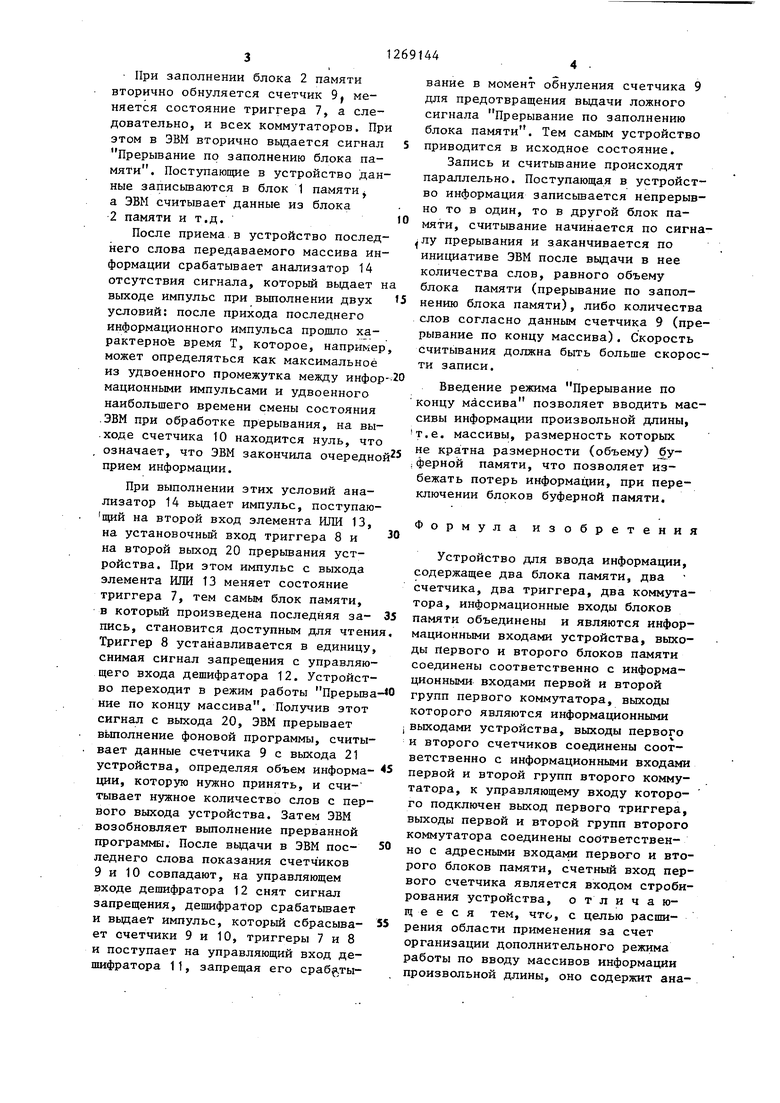

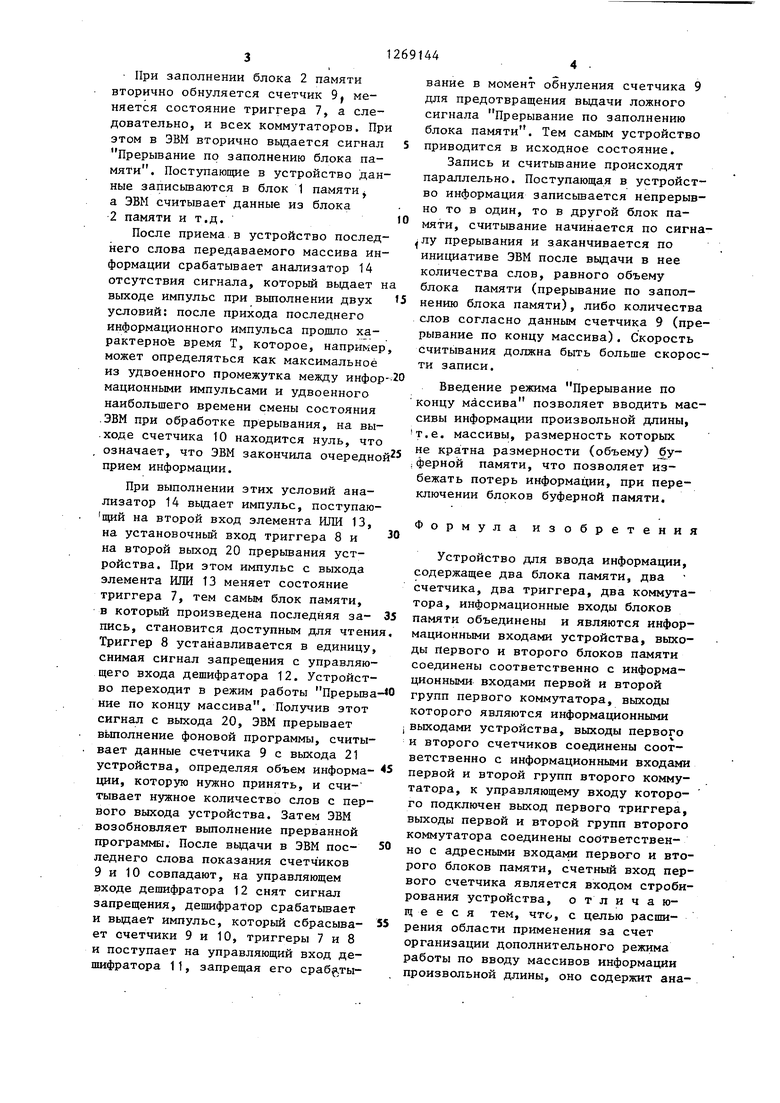

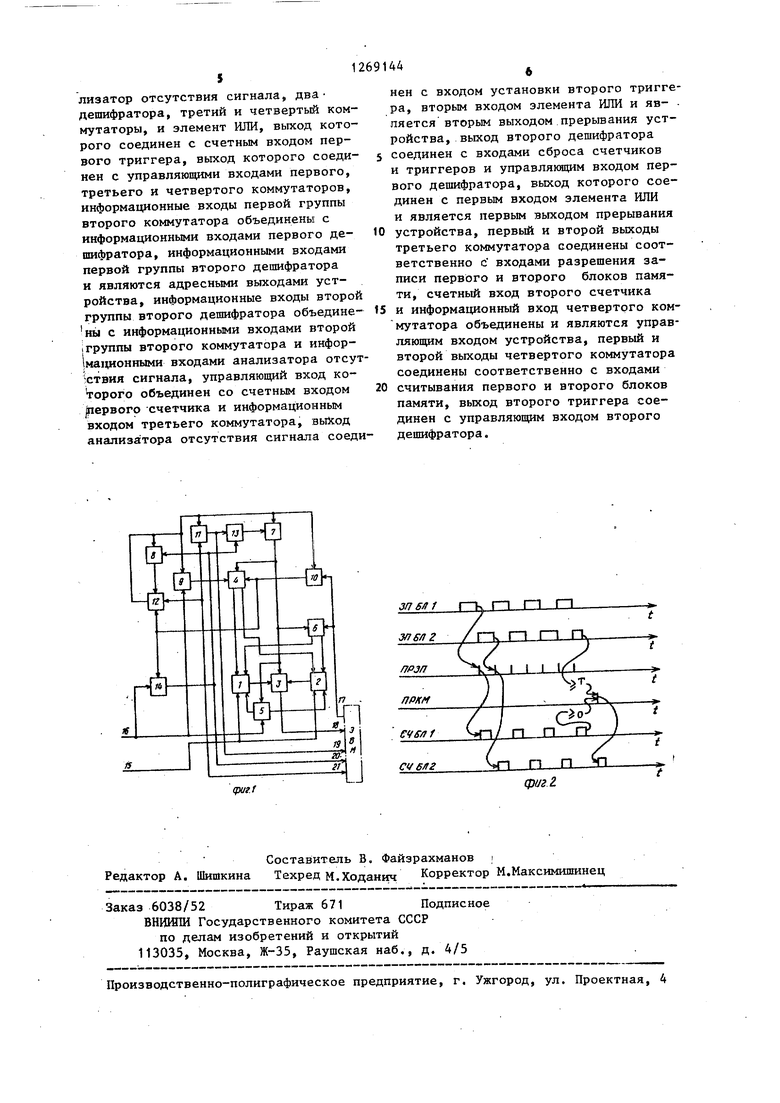

Изобретение относится к вычислительной технике и может быть испопь 1зовано в качестве устройства преобразования и буферизации данных и дл сопряжения ЭВМ с каналами связи. Цель изобретения - расширение области применения устройства за счет организации дополнительного режима работы по вводу массивов информации произвольной длины (Прерывание по концу массива). На фиг,1 представлена функционал ная схема устройства; на фиг.2 - вр менные диаграммы процессов записи, считывания и сигналов прерываний. Устройство содержит первый 1 и второй 2 блоки памяти, первьй 3, вт рой 4, третий 5 и четвертый 6 коммутаторы, первый 7 и второй 8 триггеры, первый 9 и второй 10 счетчики первый 11 и второй 12 дешифраторы, элемент ИЛИ 13, анализатор 14 отсутствия сигнала, информационные входы 15, вход 16 стробирования, уп равляющий вход 17, информационные выходы 18, первый 19 и второй 20 выходы прерывания, адресные выходы 21 . Устройство работает следующим об разом. В исходном состоянии до поступления информации на вход счетчики 9 и 10 сброшены, триггеры 7 и 8 установлены в состояние логического нуля, сигнал на выходе триггера 7 определяет начальное состояние коммутаторов, при котором коммутаторы 5 и 6 пропускают сигналы со своих входов на пер.вые выходы. Коммутатор 3 пропускает на выход сигналы с-пер вого входа, а коммутатор 4 пропуска ет на первый и второй свои выходы сигналы соответственно с первого. и второго входов. На вход 15 устройства поступает информация в виде параллельного двоичного кода. Импульсы стробиров ния с входа 16 поступают на счетный вход счетчика 9 и через коммутатор 5 на вход записи блока 1 памяти. Данные с выхода счетчика 9 через коммутатор 4 поступают на адресный вход блока 1 памяти и определяют адрес ячейки блока памяти, в которую будет записано очередное слово информации. Счетчик 9 подсчитывает количество записанных слов, разряд ность его определяется объемом бло памяти. При заполнении блока памяти счетчик 9 обнуляется,срабатьшает дешифратор 11, который формирует импульс, поступающий через элемент ИЛИ 13 на счетньй вход триггера 7, меняя его состояние. Этот же импульо поступает на первьй выход 19 прерывания устройства, сигнализируя, что устройство находится в режиме Прерывание по заполнению блока памяти. Получив этот сигнал, ЭВМ прерывает выполнение фоновой программы и начинает счич-ывать информацию из устройства. При переключении триггера 7 меняется состояние всех коммутаторов, при этом коммутаторы 5 и 6 пропускают сигналы со своих входов на вторые выходы, коммутатор 3 пропускает на выход сигналы с второго входа, а коммутатор 4 пропускает на первый и второй свои вькоды сигналы соответственно с второго и первого входов. Таким образом, на адресный вход блока 1 памяти через коммутатор 4 поступает адрес, формируемый счетчиком 10, а на вход считьшания поступают через коммутатор 6 импульсы, считьюания с входа 17. Выход блока 1памяти через коммутатор 3 подключается к информационному выходу 18 устройства, ЭВМ начинает считывать информацию из блока 1 памяти. Счетчик 10 подсчитывает количество слов, переданных из устройства в ЭВМ, данные на его выходе определяют адрес ячейки блока памяти, которая считывается из устройства в ЭВМ. Разрядность счетчика 10, как и счетчика 9, определяется объемом блока памяти. ЭВМ после приема из устройства фиксированного количества слов, равного объему блока памяти, возобновляет вьтолнение прерванной программы, а счетчик 10 автоматически обнуляется после выдачи в ЭВМ последнего слова из данного блока памяти. После,переключения триггера 7 (в том числе и во время вьщачи информации в ЭВМ) данные, поступающие в устройство, записываются в блок 2 памяти. Адрес записи поступает с выхода счетчика 9 через второй выход коммутатора 4 на адресный вход блока 2памяти. Импульсы стробирования с входа 16 через второй выход коммутатора 5 поступают на вход записи блока 2 памяти. При заполнении блока 2 памяти вторично обнуляется счетчик 9, меняется состояние триггера 7, а следовательно, и всех коммутаторов. Пр этом в ЭВМ вторично выдается сигнал прерывание по заполнению блока памяТи, Поступающие в устройство дан ные записьшаются в блок 1 памяти а ЭВМ считывает данные из блока 2 памяти и т.д. После приема в устройство послед него слова передаваемого массива ин формации срабатывает анализатор 14 отсутствия сигнала, который выдает выходе импульс при выполнении двух условий: после прихода последнего информационного импульса продшо характерное время Т, которое, наприме может определяться как максимальное из удвоенного промежутка между инфор мационными импульсами и удвоенного наибольшего времени смены состояния .ЭВМ при обработке прерывания, на выходе счетчика 10 находится нуль, что означает, что ЭВМ закончила очередно прием информации. При выполнении этих условий анализатор 14 вьщает импульс, поступающий на второй вход элемента ИЛИ 13, на установочный вход триггера 8 и на второй выход 20 прерьшания устройства. При этом импульс с выхода элемента ШШ 13 меняет состояние триггера 7, тем самым блок памяти, Б который произведена последняя запись, становится доступным для чтени Триггер 8 устанавливается в единицу снимая сигнал запрещения с управляющего входа дешифратора 12. Устройство переходит в режим работы Прерыва ние по концу массива. Получив этот сигнал с выхода 20, ЭВМ прерывает вьшолнение фоновой программы, считывает данные счетчика 9 с выхода 21 устройства, определяя объем информации, которую нужно принять, и считывает нужное количество слов с первого выхода устройства. Затем ЭВМ возобновляет выполнение прерванной программы. После вьщачи в ЭВМ последнего слова показания счетчиков 9 и 10 совпадают, на управляющем входе дешифратора 12 снят сигнал запрещения, дешифратор срабатьшает и вьщает импульс, который сбрасывает счетчики 9 и 10, триггеры 7 и 8 и поступает на управляющий вход дешифратора 11, запрещая его сраб тывание в момент обнуления счетчика 9 для предотвращения выдачи ложного сигнала Прерывание по заполнению блока памяти. Тем самым устройство приводится в исходное состояние. Запись и считьгоание происходят параллельно. Поступающая в устройство информация записьшается непрерывно то в один, то в другой блок памяти, считьшание начинается по сигналу прерывания и заканчивается по инициативе ЭВМ после выдачи в нее количества слов, равного объему блока памяти (прерывание по заполнению блока памяти), либо количества слов согласно данным счетчика 9 (прерывание по концу массива). Скорость считывания должна быть больше скорости записи. Введение режима Прерывание по концу массива позволяет вводить массивы информации произвольной длины, т.е. массивы, размерность которых не кратна размерности (объему) уферной памяти, что позволяет избежать потерь информации, при переключении блоков буферной памяти. Формула изобретения Устройство для ввода информации, содержащее два блока памяти, два счетчика, два триггера, два коммутатора, информационные входы блоков памяти объединены и являются информационными входами устройства, выходы первого и второго блоков памяти соединены соответственно с информационными входами первой и второй групп первого коммутатора, выходы которого являются информационными выходами устройства, выходы первого и второго счетчиков соединены соответственно с информационными входами первой и второй групп второго коммутатора, к управляющему входу которого подключен выход первого триггера, выходы первой и второй групп второго коммутатора соединены соответственно с адресными входаьда первого и второго блоков памяти, счетный вход первого счетчика является входом стробирования устройства, о т л и ч а ющ е е с я тем, что, с целью расширения области применения за счет организации дополнительного режима работы по вводу массивов информации произвольной длины, оно содержит анализатор отсутствия сигнала, два дешифратора, третий и четвертый коммутаторы, и элемент ИЛИ, выход которого соединен с счетным входом первого триггера, вьпсод которого соединен с управляющими входами первого, третьего и четвертого коммутаторов, информационные входы первой группы второго коммутатора объединены с информационными входами первого дешифратора, информационными входами первой группы второго дешифратора и являются адресными выходами устройства, информационные входы второй группы второго дешифратора объединены с информационными входами второй (Группы второго коммутатора и инфор1ма1Д1онными входами анализатора отсут1ствия сигнала, управляющий вход которого объединен со счетным входом fiepaoro счетчика и информационным входом третьего коммутатора, выход анализатора отсутствия сигнала соединен с входом установки второго триггера, вторым входом элемента ИЛИ и яв- пяется вторым выходом прерьюания устройства, выход второго дешифратора соединен с входами сброса счетчиков и триггеров и управлякщим входом первого дешифратора, выход которого соединен с первым входом элемента ИЛИ и является первым выходом прерывания

0 устройства, первый и второй выходы третьего коммутатора соединены соответственно с входами разрешения записи первого и второго блоков памяти, счетный вход второго счетчика S и информационный вход четвертого коммутатора объединены и являются управляющим входом устройства, первый и второй выходы четвертого коммутатора соединены соответственно с входами считывания первого и второго блоков памяти, выход второго триггера соединен с управляющим входом второго дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1287170A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для обмена информацией между абонентом и ЭВМ | 1986 |

|

SU1314346A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство для ввода информации | 1987 |

|

SU1508825A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для сопряжения вычислительной машины с внешним устройством | 1985 |

|

SU1278868A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1989 |

|

SU1647581A2 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1425692A2 |

Изобретение относится к вычислительной технике и может быть .использовано в качестве устройства преобразования и буферизации данных и для сопряжения ЭВМ с каналами связи. Цель изобретения - расширение области применения устройства за счет организации дополнительного режима работы Прерывание по концу массива, Оно содержит два блока памяти, два счетчика, четыре коммутатора, два дешифратора, два триггера, анализатор отсутствия сигнала и элемент ИЛИ. Информация, поступающая на устройство, заносится в буферные блоки памяти, а затем считывается из них в одном из двух режимов. В режиме Прерывание по заполнению блока памяти 13 ii. . л информация заносится в один из блоков памяти и одновременно считывается из другого. Счетчики вырабатывают адреса записи и считьшания. При заполнении блока памяти заносимой информацией срабатывает .первый дешифратор, на вывыход устройства поступает сигнал прерывания и происходит переключение блоков памяти относительно операций записи и чтения информации. В режиме Прерывание по концу массива возможно чтение информации из незаполненного до конца блока памяти. Переход в этот режим происходит в том случае, i когда один из блоков памяти пуст, а в другой определенное время не пос(Л тупает информация. В этом случае срабатывает анализатор отсутствия сигнала. Происходит переключение частично заполненного блока памяти с записи на считьшание. На выход устройства вьщается сигнал прерывания. После считывания всей информаю ции из блока памяти устройство возot. вращается в исходное состояние Ввесо дение режима Прерывание по концу массива позволяет организовать 4 4 ввод информации, объем которой не кратен объему буферной памяти. 2 ил.

| Устройство для ввода информации | 1982 |

|

SU1084775A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1982 |

|

SU1049893A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-04-04—Подача