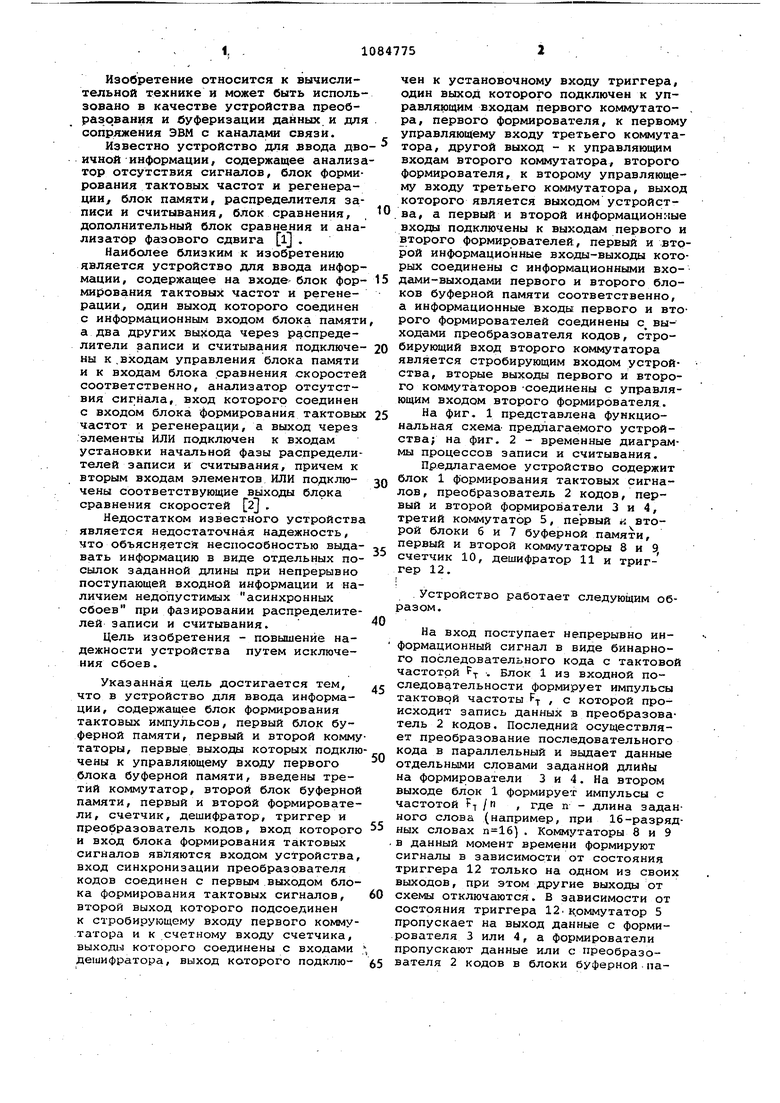

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства преобразования и буферизации данных и для сопряжения ЭВМ с каналами связи. Известно устройство для ввода дво ичной информации, содержащее анализа тор отсутствия сигналов, блок формирования тактовых частот и регенерации, блок Пс1мяти, распределителя записи и считывания, блок сравнения, дополнительный блок сравнения и анализатор фазового сдвига ij . Наиболее близким к изобретению является устройство для ввода информации, содержащее на входе блок формирования тактовых частот и регенерации, один выход которого соединен с информационным входом блока памяти а два других выхода через р спределители записи и считывания подключены к.входам управления блока памяти и к входам блока сравнения скоростей соответственно, анализатор отсутствия сигнала, вход которого соединен с входом блока формирования тактовых частот и регенераци, а выход через элементы ИЛИ подключен к входам установки начальной фазы распределителей записи и считывания, причем к вторым входам элементов ИЛИ подключены соответствующие выходы блока сравнения скоростей 2 . Недостатком известного устройства является недостаточная надежность, что объясн5 етс:я неспособностью выдавать информацию в виде отдельных посылок заданной длины при непрерывно поступающей входной информации и наличием недопустимых асинхронных сбоев при фазировании распределителей записи и считывания. Цель изобретения - повышение надежности устройства путем исключения сбоев. Указанная цель достигается тем, что в устройство для ввода информации, содержащее блок формирования тактовых импульсов, первый блок буферной памяти, первый и второй комму таторы, первые выходы которых подклю чены к управляющему входу первого блока буферной памяти, введены третий коммутатор, второй блок буферной памяти, первый и второй формирователи, счетчик, дешифратор, триггер и преобразователь кодов, вход которого и вход блока формирования тактовых сигналов являются входом устройства, вход синхронизации преобразователя кодов соединен с первым выходом блока формирования тактовых сигналов, второй выход которого подсоединен к стробирующему входу первого коммутатора и к счетному входу счетчика, выходы которого соединены с входами дешифратора, выход которого поДключен к установочному входу триггера, один выход которого подключен к управляющим входам первого коммутато- , ра, первого формирователя, к первому управляющему входу третьего коммутатора, другой выход - к управляющим входам второго коммутатора, второго формирователя, к второму управляющему входу третьего коммутатора, выход которого является выходом устройства, а первый и второй информационные входы подключены к выходам первого и второго формирователей, первый и второй информационные входы-выходы которых соединены с информационными входами-выходами первого и второго блоков буферной памяти соответственно, а информационные входы первого и второго формирователей соединены с выходами преобразователя кодов, стробирующий вход второго коммутатора является стробирующим входом устройства, вторые выходы первого и второго коммутаторов соединены с управляющим входом второго формирователя. На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы процессов записи и считывания. Предлагаемое устройство содержит блок 1 формирования тактовых сигналов, преобразователь 2 кодов, первый и второй формирователи 3 и 4, третий коммутатор 5, первый w второй блоки б и 7 буферной памяти, первый и второй коммутаторы 8 и 9 счетчик 10, дешифратор 11 и триггер 12. Устройство работает следующим образом. На вход поступает непрерывно информационный сигнал в виде бинарного последовательного кода с тактовой частотой FT . Блок 1 из входной последовательности формирует импульсы тактовой частоты FT с которой происходит запись данных в преобразователь 2 кодов. Последний осуществляет преобразование последовательного кода в параллельный и выдает данные отдельными словами заданной длийы на формирователи 3 и 4. На втором выходе блок 1 формирует импульсы с частотой FT /п , где п - длина заданного слова (например, при 16-разрядных словах ). Коммутаторы 8 и 9 в данный момент времени формируют сигналы в зависимости от состояния триггера 12 только на одном из своих выходов, при этом другие выходы от схемы отключаются. В зависимости от состояния триггера 12. коммутатор 5 пропускает на выход данные с формирователя 3 или 4, а формирователи пропускают данные или с преобразователя 2 кодов в блоки буферной памяти или с блоков буферной памяти на коммутатор 5. Пусть в данный момент времени триггер 12 находится, например, в состоянии 1. При этом данные через формирователь 3 поступают на информационные входы блока в буферной памяти в виде сформированного слова заданной длины. Сформированный блоко 1 импульс тактовой частоты слова (Т-Т/П-) поступает на коммутатор 8, который при этом на первом своем выходе формирует сигнгш управления, по которому происходит запись данных в блок 6, второй выход коммутатора 8 от схемы отключен (например, путем блокировки сигналом триггера) . При каждом формировании слова формируется тактовый импульс слова и происходит запись данных в блок б. В этот же момент времени при каждом поступлении от ЭВМ импу51ьса на вход о коммутатора 9 последний вырабатывает сигнал управления на вто ром своем выходе (первый выход отключен сигналом триггера), по котор му происходит считывание записанных ранее данных с блока 7 через формирователь 4 и колв«утатор 5 на выход устройства отдельными словами. Считывание продолжается до тех пор, пока не будет считано все содержимо блока буферной памяти. Запись вбло б буферной памяти продолжается до полного его заполнения. Счетчик 10 осуществляет счет количества записа нда слов, разрядность его определя 3/7

3/7 СУ

CV

7

CV

фз

fM j y/lfti

3/f

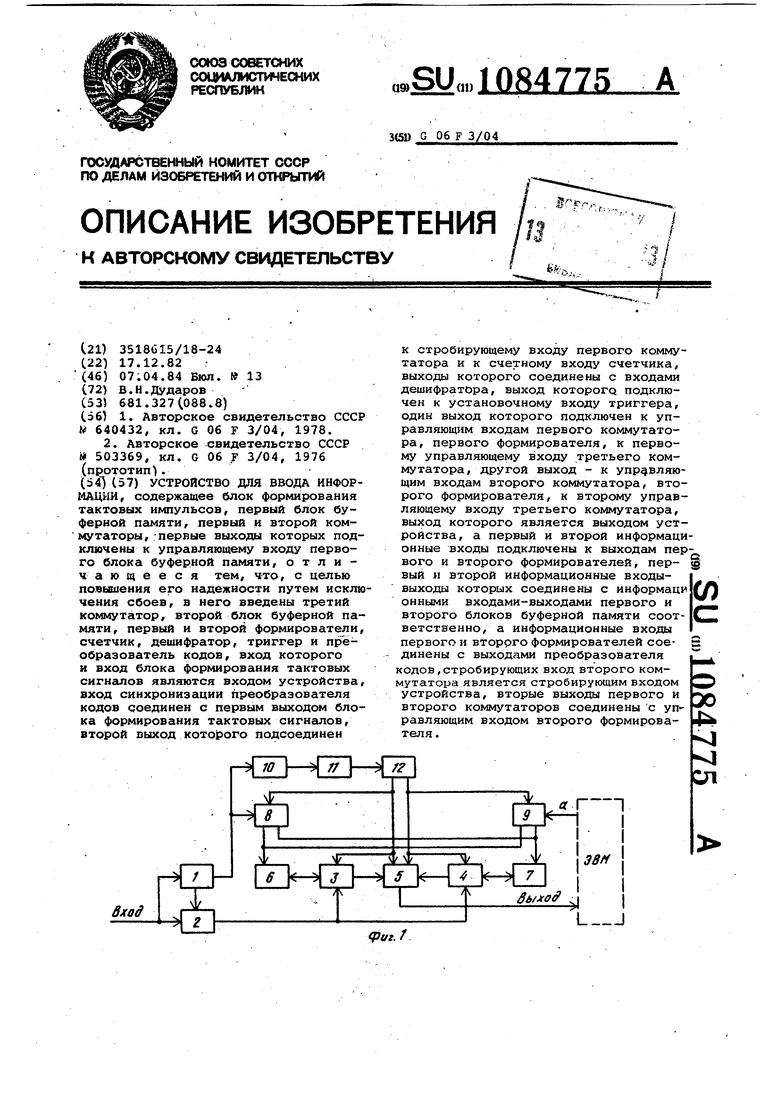

ф1/г. 2 ется объемом блока памяти. При поступлении последнего записываемого в данный блок слова счетчик 10 обнуяется, срабатывает дешифратор 11, который формирует импульс, перебрасывающий триггер в другое состояние О. Следуюдее слово уже записывается в другой блок 7 буферной памяти, а из блока 6 через формирователь 3 и коммутатор 5 считываются записанные перед этим данные на выход устройства и т.д. Процессы записи и считывания данных идут независимо один от другого. ria фиг. 2 представлены временные диаграммы записи (ЗП) и считывания (СЧ) для каждого блока буферной памяти. Скорость считывания должна быть выше скорости записи. Запись идет непрерывно то в один, то в другой блок, считывание начинается с момента переключения триггера 12, когда коммутатор 9 разрешает прием сигналов по входу о , и заканчивается раньше, чем произойдет следуквдее переключение триггера. Таким образом, полная длина отдельных посылок, выдаваемых устройством, определяется объемом блока буферной памяти (она может также задаваться разрядностью счетчика 10 и числом импульсов)/. Предлагаемое устройство имеет более высокую надежность по сравнению с базовым, так как не требует осуществления фазирования коммутаторов 8 и 9, что принципиально исключает возможность асинхронных сбоев, присущих базовому устройству.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство отображения формы электрического сигнала | 1983 |

|

SU1151820A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОР МАЦИИ, содержащее блок формирования тактовых И1ишульсов, первый блок буферной памяти, первый и второй коммутаторы, -первые выходы которых под ключены к управляющему входу первого блока буферной памяти, отличающееся тем, что, с целью повышения его надежности путем искл чения сбоев, в него введены третий коммутатор, второй блок буферной па мяти, первый и второй формирователи счетчик, дешифратор, триггер и преобразователь кодов, вход которого и вход блока формирования тактовых сигнгшов являются входом устройства вход синхронизации преобразователя кодов соединен с первым выходом бло ка формирования тактовых сигналов, второй выход KOToi oro подсоединен к стробирующему входу первого коммутатора и к счетному входу счетчика, выходы которого соединены с входами дешифратора, выход которого подключен к установочному входу триггера, один выход которого подключен к управляющим входам первого коммутатора, первого формирователя, к первому управляющему входу третьего коммутатора, другой выход - к упр вляющим входам второго коммутатора, второго формирователя, к второму управляющему входу третьего коммутатора, выход которого является выходом устройства, а первый и второй информаци онные входы подключены к выходам пер вого и второго формирователей, первый и второй информационные входывыходы которых соединены с ннформаци онными входами-выходами первого и второго блоков буферной памяти соответственно, а информационные входы первого и второго формирователей соединены с выходами преобразователя одов ,стробирующих вход второго комутатора является стробирующим входом устройства, вторые выходы первого и второго коммутаторов соединены с управляющим входом второго формирователя. п I II

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство переприема двоичных сигналов | 1977 |

|

SU640432A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для квазисинхронного ввода двоичных сигналов | 1973 |

|

SU503369A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-12-17—Подача