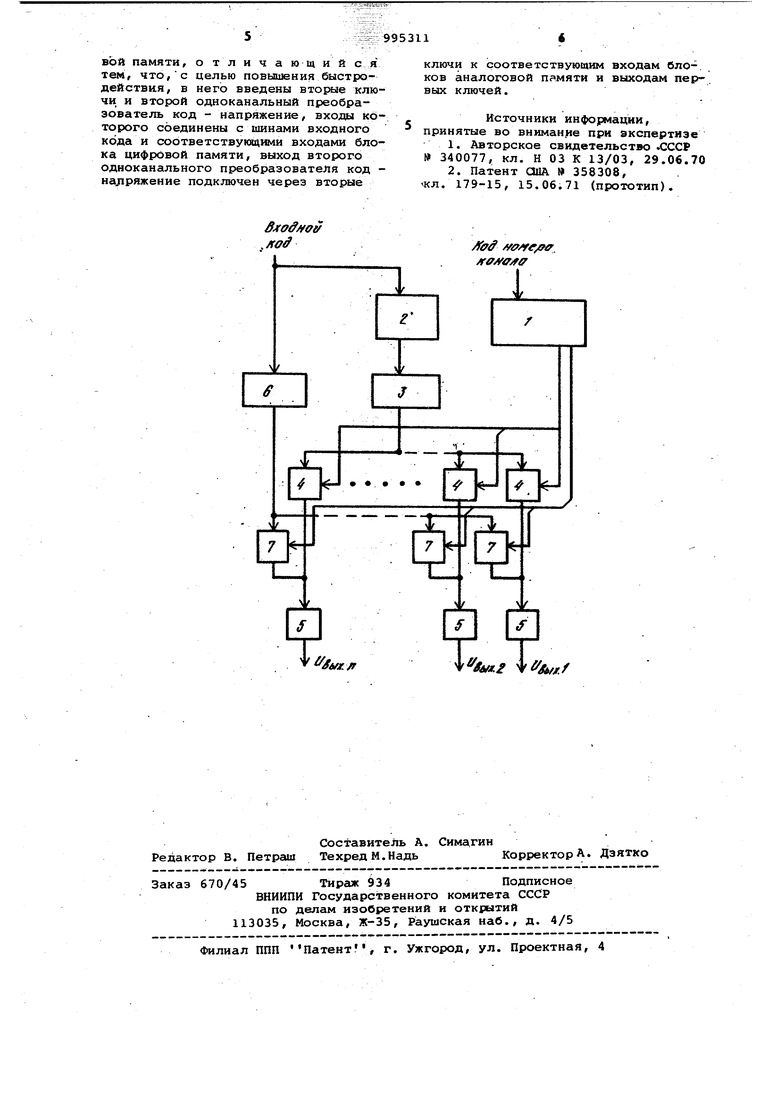

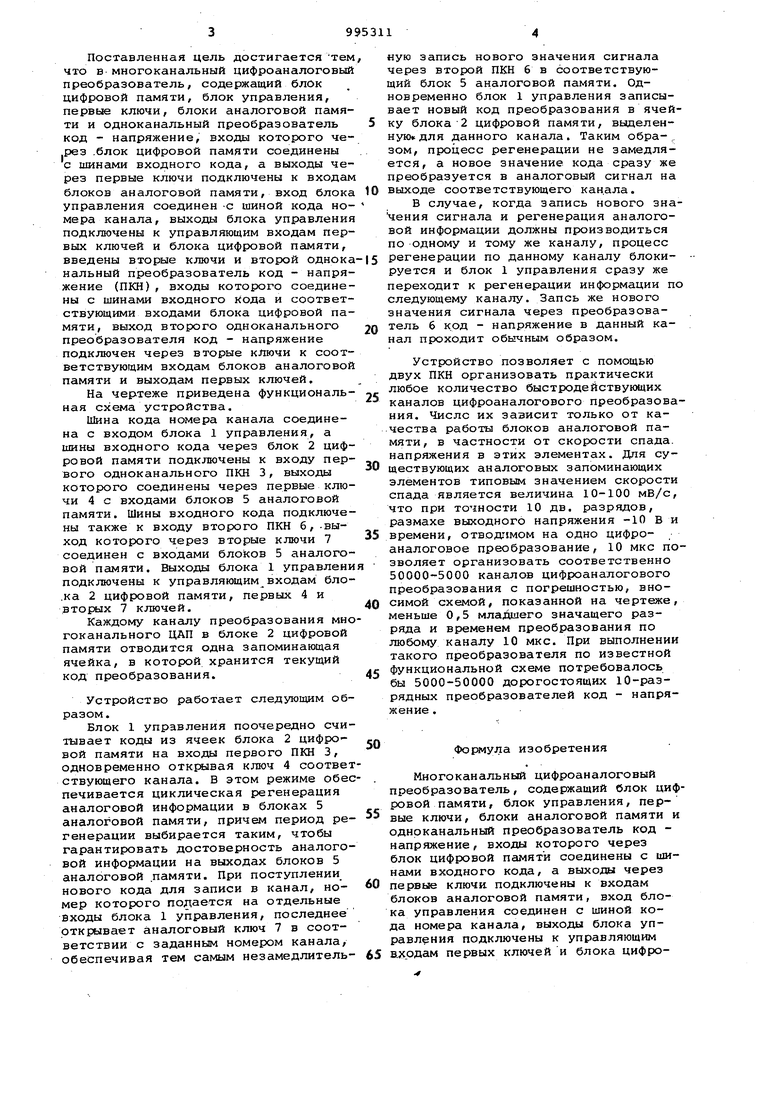

Поставленная цель достигается тем что в многоканальный цифроаналоговый преобразователь, содержащий блок цифровой памяти, блок управления, первые ключи, блоки аналоговой памяти и одноканальный преобразователь код - напряжение, входы которого через .блок цифровой памяти соединены с шинами входного кода, а выходы через первые ключи подключены к входам блоков аналоговой памяти, вход блока управления соединен -с шиной кода номера канала, выходы блока управления подключены к управляющим входам первых ключей и блока цифровой памяти, введены вторые ключи и второй однока нальный преобразователь код - напряжение (ПКН), входы которого соединены с шинами входного Кода и соответствующими входами блока цифровой памяти, выход второго одноканального преобразователя код - напряжение подключен через вторые ключи к соответствующим входам блоков аналоговой памяти и выходам первых ключей. На чертеже приведена функциональная схема устройства. Шина кода номера канала соединена с входом блока 1 управления, а шины входного кода через блок 2 цифровой памяти подключены к входу первого одноканального ПКН 3, выходы которого соединены через первые ключи 4 с входами блоков 5 аналоговой памяти. Шины входного кода подключены также к входу второго ПКН б,-выход которого через вторые ключи 7 соединен с входами блоков 5 аналоговой памяти. Выходы блока 1 управлени подключены к управлякядим входам бло.ка 2 цифровой памяти, первых 4 и вторых 7 ключей. Каждому каналу преобразования мно гоканального ЦАП в блоке 2 цифровой памяти отводится одна запоминающая ячейка, в которой хранится текущий код преобразования. Устройство работает следующим образом. Блок 1 управления поочередно считывает коды из ячеек блока 2 цифровой памяти на входы первого ПКН 3, одновременно открывая ключ 4 соответ ствующего канала, в этом режиме обес печивается циклическая регенерация аналоговой информации в блоках 5 аналоговой памяти, причем период регенерации выбирается таким, чтобы гарантировать достоверность аналоговой информации на выходах блоков 5 аналоговой .памяти. При поступлении нового кода для записи в канал, номер которого подается на отдельные Входы блока 1 управления, последнее открывает аналоговый ключ 7 в соответствии с заданным номером канала, обеспечивая тем самым незамедлительную запись нового значения сигнала через второй ПКН 6 в соответствующий блок 5 аналоговой памяти. Одновременно блок 1 управления записывает новый код преобразования в ячейку блока 2 цифровой памяти, выделенную для данного канала. Таким обра-, зом, процесс регенерации не замедляется, а новое значение кода сразу же преобразуется в аналоговый сигнал на выходе соответствующего кан.ала. В случае, когда запись нового значения сигнала и регенерация аналоговой информации должны производиться по одному и тому же каналу, процесс регенерации по данному каналу блокируется и блок 1 управления сразу же переходит к регенерации информации по следующему каналу. Запсь же нового значения сигнала через преобразователь 6 код - напряжение в данный канал проходит обычным образом. Устройство позволяет с помощью двух ПКН организовать практически любое количество быстродействующих каналов цифроаналогового преобразования. Числе их зависит только от качества работы блоков аналоговой памяти, в частности от скорости спада, напряжения в этих элементах. Для существующих аналоговых запоминающих элементов типовым значением скорости спада является величина 10-100 мВ/с, что при точности 10 дв. разрядов, размахе выходного напряжения -10 в и времени, отводммом на одно цифроаналоговое преобразование, 10 мкс позволяет организовать соответственно 50000-5000 каналов цифроаналогового преобразования с погрешностью, вносимой схемой, показанной на чертеже, меньше 0,5 младшего значащего разряда и временем преобразования по любому каналу 10 мкс. При выполнении такого преобразователя по известной функциональной схеме потребовалось бы 5000-50000 дорогостоящих 10-разрядных преобразователей код - напряжение . Формула изобретения Многоканальный цифроаналоговый преобразователь, содержащий блок цифровой памяти, блок управления, первые ключи, блоки аналоговой памяти и однрканальный преобразователь код напряжение, входы которого через блок цифровой памяти соединены с шинами входного кода, а выходы через первые ключи подключены к входам блоков аналоговой памяти, вход блока управления соединен с шиной кода номера канала, выходы блока управления подключены к управляющим в,}4одам первых ключей и блока цифровой памяти, отличающий с я тем, что,с целью повышения быстродействкя, в него введены вторые ключи, и второй одноканальный преобразователь код - напряжение, входы которого соединены с шинами входного кода и соответствующими входами блока цифровой памяти, выход второго одноканального преобразователя код напряжение подключен через вторые

ключи к соответствующим входам бло-. ков аналоговой памяти и выходам первых ключей.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство .ССС1Р 340077, кл. Н 03 К 13/03, 29.06.70

2. Патент ОНА И 358308, кл. 179-15, 15.06.71 (прототип).

/feff ,

/fOAfff ff

Juw:/

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифроаналоговый преобразователь | 1987 |

|

SU1431073A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Многоканальный цифро-аналоговый преобразователь | 1981 |

|

SU1029409A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Двухканальный цифровой осциллограф | 1989 |

|

SU1705749A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Устройство для преобразования сигналов информационно-измерительной системы | 1982 |

|

SU1062751A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Многоканальное адаптивное аналого-цифровое устройство | 1987 |

|

SU1520660A1 |

Авторы

Даты

1983-02-07—Публикация

1981-04-02—Подача