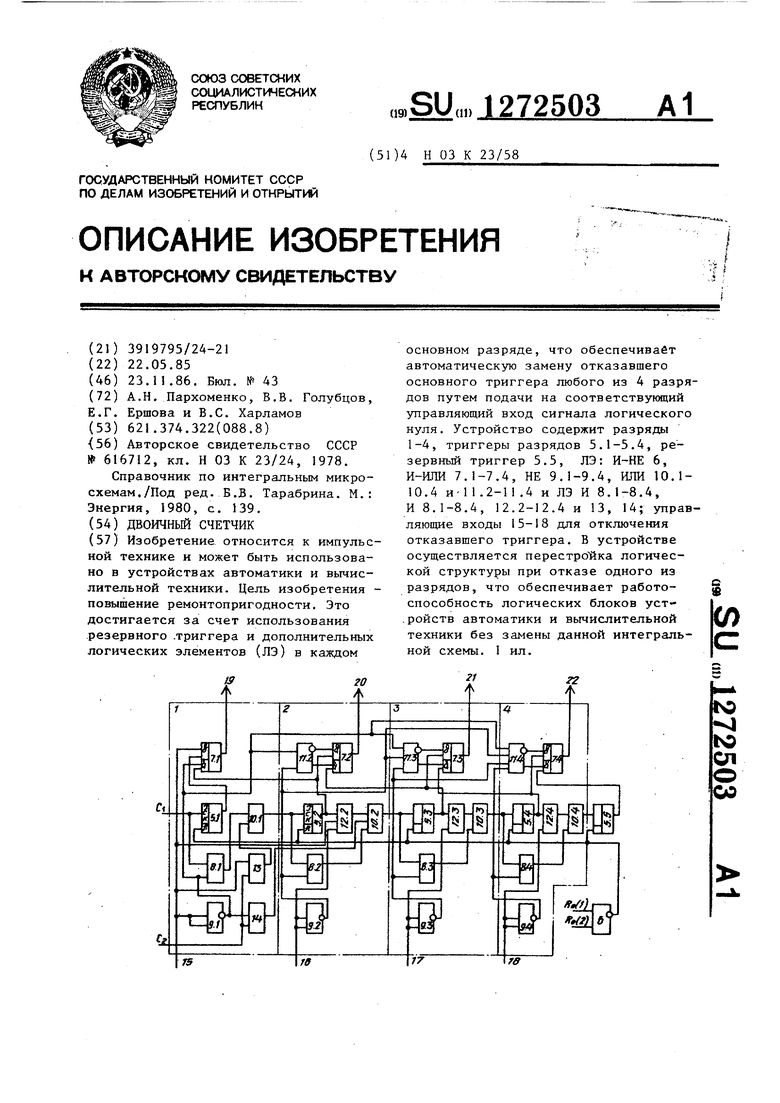

« Изобретение относится к импульсно технике и может быть использовано в устройствах автоматики и вычислительной техники. На чертеже приведена функциональмая схема предлагаемого двоичного счетчика. Цель изобретения - повьтение ремонтопригодности . Устройство содержит разряды 1-4, триггеры 5.1-5.4 разрядов, резервный триггер 5.5, элемент И-НЕ 6, элемён;ты И-ИЛИ 7.1-7.4, первые элементы И 8.1-8.4, элементы НЕ 9.1-9.4 и пер вые элементы ИЛИ 10.1-10.4, вторые элементы ИЛИ 11.2-11.4, вторые элементы И 12.2-12.4, третий 13 и четвертый 14 элементы И. Управляющие входы 15-18 предназна чены для отключения отказавшего триг гера. При работе основных триггеров 5.1-5.4 на соответствующие управляющие входы подается сигнал логической I. При отказе какого-либо триггера на соответствующий вход подается сигнал логического О. Элементы ИЛИ 7.1-7.4 предназначе на- соответствующи ны для коммутации выходы устройства значений выходов триггеров данного или последующего разряда. Первые элементы И 8.1-8.4 исполь зуются для организации обходной цепи синхроимпульсам при отказе триггера соответствующего разряда. Элементы НЕ 9.1-9.4 инвертируют соответствующие управляющие сигналы Первые элементы ИЛИ 10.1-10.4 обесп чивают прохождение синхросигнала ли бо от триггера данного разряда, либо через обходную цепь от триггера предьщущего разряда. Вторые элементы ИЛИ 11.2-11.4 предназначены для подачи сигнала о необходимости пере , коммутации выходов триггеров на последующие разряды. Третий элемент И 13 обеспечивает прохождение сигналов с второго синх ровхода на вход триггера второго разряда при тлсправком триггере перв го разряда, а четвертый элемент И 14 обеспечивает прохождение этих сигна лов на счетньш вход триггера третье го разряда при неисправном триггере первого разряда. Устройство работает следующим об разом. 3 Для установки двоичного счетчика в исходное состояние одновременно на оба установочных входа подаются - 1. Выход 19 сигналы логической соединяется с вторым синхровходом устройства. При исправном состоянии всех основных триггеров на управляющие входы 15-18 подаются сигналы логической 1. В этом случае единичными разрещающими сигналами открыты следующие элементы устройства: третий элемент И 13 первого разряда, первая группа входов элемента И-ИЛИ первого разряда, вторые элементы И второго, третьего и четвертого разрядов. Одновременно с этим закрываются для прохождения синхроимпульсов счетд следующие элементы устройства: первые элементы И каждого разряда, вторая группа входов элемента И-ИЛИ первого разряда и через вторые элементы ИЛИ вторые группы входов элементов И-ИЛИ второго, третьего и четвертого разрядов. Первые группы входов этих трех элементов открыты разрещающим сигналом с инверсного выхода соответствующих вторых элементов ИЛИ данного разряда. Подсчет импульсов, поступающих на первый синхровход устройства, производится по следующей логической ветви предлагаемого двоичного счетчика. Импульсы поступают на счетньш вход первого триггера 5.1, а состояние его выхода через открытую первую группу входов элемента 2И-ИЛИ 7.1 на первый выход счетчика и через соединение Q i-iCj, открытые третий 13 элемент И и первый элемент ИЛИ 10.1 - на счетный вход триггера 5.2. Элементы И 8.1-8.4 закрыты,и поэтому синхроимпульсы не проходят через эти обходные цепи. Значения состояния выхода триггера 5.2 (и его изменение) поступает через элементы И 12.2 и ИЛИ 10.2 на счетный вход триггера 5,3 третьего разряда, а также через открытую первую группу входов элемента И-ИЛИ 7.2 - на второй выход счетчика. Значение состояний (и их изменение) с выходов триггеров 5.3 и 5.4 передается на последующие разряды аналогичHfjiM образом. Значение состояний выхрда резервного триггера 5.5 на выход счетчика в этом случае не поступает, так как вторая группа входов элемента И-ИЛИ 7.4 закрыта. При отказе какогс1-либо основного трнг1ера раз1)яда на соответствующий вх(5д данного разряда подается нулевой потенциал и данный триггер исклю чается из режима функционирования двоичного счетчика. При отказе триггера 5.1 первого разряда, двоичный счетчик функционирует следующим оёразом. На управляющий вход t5 подается сигнал логичес кого О, которьпЧ закрывает для прохождения синхроимпульсов следующие элементы двоичного счетчика: третий элемент И 13 и первую группу входов элемента И-ИЛИ 7.1 первого разряда. Одновременно с этим сигналом с выхо да. НЕ 9.1 открывают четвертый элемент И 14, первый элемент И 8.1 и вторая группа входов элемента И-ИЛИ 7.1 первого разряда, а также через соответствующие элементы ИЛИ 11.211.4 - вторые группы входов элементов И-ИЛИ второго, третьего и четвер того разрядов. Первые группы входов этих элементов закрываются сигналами с инверсных выходов соответствующих вторых элементов ИЛИ 11.2-11.4. Импульсы счета в этом случае проходят по следующей логической ветви двоичного счетчика: с первого синхро входа устройства через первый элемен И 8.1, первьй элементИЛИ 10.1 на счетньй вход триггера 5.2 второго I разряда, т.е. обходит триггер 5.1. На первый выход счетчика состояние выхода триггера первого разряда не поступает, так как первая группа вхо дов элемента 2И-ИЛИ 7.1 закрыта. Зна чение состояния (и его изменения) выхода триггера 5.2 второго разряда также не поступает на свой второй выход устройства, а поступает через открытую вторую группу входов элемен та И-ИЛИ 7.1 на первый выход счетчика. Таким образом, триггер 5.2 второ го -разряда заменил неисправный триггер 5.1 первого разряда. Далее значение состояния (и его изменения) выхода триггера 5.2 через соединени Q I-fC , четвертый элемент И 14, первый элемент ИЛИ 10.2 поступает на счетный вход триггера 5.3 третьего разряда. Значение состояния (и его изменения) выхода триггера 5.3 третьего разряда поступает через открытую вторую группу входов элемента И-ИЛИ 7.2 на второй выход 20 (Q,j) счетчика и не поступает на выход 21 (QJ), так как первая группа входов элемента И-Ш1И 7.3 закрыта. Одновременно значения выхода триггера 5.3через элементы И 12.3 и ИЛИ 10.3 поступают на счетный вход триггера 5.4четвертого разряда, значения выходов (и изменения) которого поступают через открытую вторую группу входов элемента И-ИЛИ 7.3 на выход 21 {QJ) и не поступают через закрытую первую группу входов элемента И-ИЛИ 7.4 на выход 22 (Q.4). Значение состояний (и их изменения) выхода триггера 5.4 через элементы И 12.4 и ИЛИ 10.4 поступает на счетный вход резервного триггера 5.5, значение выходов которого через открытую вторую группу выходов элемента 2И-ИЛИ 7.4 поступают на выход 22 (Q) счетчика. Таким образом, при отказе первого триггера 5.1 и подаче нулевого потенциала на первый управляющий вход двоичного счетчика тр иггер 5.2 второго разряда начинает работать на выход 19, три1- гер 5.3 - на выход 20, триггер 5.4 на выход 21, а триггер 5.5 - на выход 22, обеспечивая работоспособность двоичного счетчика без дополнительной перекоммутации монтажных соединений на печатных платах логических блоков устройства автоматики и вычислительной техники. При отказе триггера второго разряда 5.2 нулевой потенциал подается на управляющий вход 16. Подсчет импульсов в этом случае производится следующим образом. Нулевой потенциал закрывает следующие элементы: первьп элемент И 12.2 второго разряда и через соответствующие элементы ИЛИ 11.2-11.4 первые группы входов элементов И-ИЛИ 7.2-7.4. Сигналы с прямых выходов элементов ИЛИ 11.2-11.4 открывают вторые группы входов cooтвejгcтвyющиx элементов И-ИЛИ 7.2-7.4. Кроме того, открывается обходная для синхроимпульсов цепь через элемент И 8.2. Поэтому логическая ветвь счета импульсов в этом случае следующая: счетный вход триггера 5.1 - выход триггера 5.1, через первую группу входов элемента И-ИЛИ 7.1 на выход 19, через соединение Q,iiC., на вход третьего элемента И 13, через элементы ИЛИ 10.1, И 8.2, ИЛИ 10.2 на счетный вход триггера 5.3, с выхода триггера 5.3 через элементы ИЛИ 12.3 и 10.3 Ш1И на счетный вход триг гера 5.4, с выхода триггера 5.4 через элементы И 12,4,ИЛИ 10.4 на счет ный вход резервного триггера 5.5. Обходные цепи через элементы 8.1, 8.3 и 8.4 закрыты и поэтому синхро-импульсы следуют только по указанной логической ветви предлагаемого двоичного счетчика. Значения выходов триггеров 5.3-5.5 через вторые групп входов элементов И-ИЛИ 1.2-1 k сдвигаются на один разряд влево, обеспечивая замену триггера второго разряда триггером третьего разряда, триг гера третьего разряда триггером четвертого разряда и триггера четвертого разряда триггером пятого (резервного) разряда. Замена отказавших третьего и четвертого триггеров производится аналогичным образом, как и второго разряда. Таким образом, в двоичном счетчике осуществляется перестройка логической структуры при отказе одного из разрядов, что создает возможност обеспечения работоспособности логических блоков.устройств автоматики и вычислительной техники без замены данной интегральной схемы и, ,,следовательно, повьппает ремонтопригодност двоичного счетчика. Фор. мула изобретения Двоичныйсчетчик, содержащий триггеры каждого разряда и элемент И-НЕ, первьй и второй установочные входы устройства соединены соответственно с первым и вторым входами элемента И-НЕ, выход которого подключен к R-входам триггеров.каждого разряда, первый синхровход устройства соединен со счетным входом триггера первого разряда, отличающийся тем, что, с целью повьшения ремонтопригодности, в него введе ны резервный триггер, а каждый разряд дополнительно содержит элемент И-ИЛИ, элемент НЕ, первые элементы И и ИЛИ, разряды, кроме первого, содержат вторые элементы И и ИЛИ, первый разряд дополнительно содержит третий и четвертый элементы И, пер вый синхровход устройства соединен первым входом первого элемента и пер вого разряда, второй синхровход уст ройства соединен с первыми входами третьего и четвертого элементов И первого разряда, управляющий вход первого разряда соединен соответственно с входом элемента ПК, с вторым входом третьего элемента И, с первым входом первой группы входов э.пемента И-ИЛИ данного разряда и с третьим входом второго элемента И второго разряда, выход триггера каждого первого и резервного разряда соединен с первым входом второго элемента И, а управляющие входы каждого, кроме первого, разрядов соединены соответственно с входом, элемента НЕ и с вторым входом второго элемента И данного разряда, выход первого элемента И каждого разряда соединен с соответствующим первым входом первого элемента ИЛИ данного разряда, выход третьего элемента И первого разряда соединен с вторым входом первого элемента ИЛИ данного разряда, выход четвертого элемента И первого разряда соединен с вторым входом первого элемента ИЛИ второго разряда, выход элемента НЕ первого разряда соединен с вторым входом первого и четвертого элементов И данного разряда, с первым входом второй группы входов элемента И-ИЛИ данного разряда и с первыми входами вторых элементов ИЛИ второго, третьего и четвертого разрядов, выход первого элемента ИЛИ- каждого разряда, кроме четвертого, соединен со счетным входом триггера последующего разряда и с первым входом первого элемента И последующего разряда, выход элемента НЕ второго разряда соединен соответственно с вторым входом первого элемента И данного разряда и с вторыми входами вторых элементов ИЛИ второго, третьего и четвертого разрядов, выход элемента НЕ третьего разряда соединен соответственно с вторым входом первого элемента И данного разряда и с третьими входами вторых элементов ИЛИ третьего и четвертого разрядов , выход элемента НЕ четвертого разряда соединен с вторым входом первого элемента И и с четвертым входом второго элемента И данного разряда, выход триггера первого разряда соединен с вторым входом первой группы входов элемента И-ИЛИ данного разряда, выход которого является первым выходом устройства, выход первого элемента ИЛИ четвертого разряда соединен со счетным входом резервного триггера, выход триггера каждого.

7 12725038

кроме первого и резервного, разрядаэлемента И-Ш1И данного разряда, выход соединен с вторым входом первой груп- второго элемента И второго разряда

пы входов элемента И-ИЛИ соответст- соединен с третьим входом первого

вующего разряда, а также с вторымэлемента ИЛИ данного разряда, выховходом второй группы входов элементаЁ ды вторых элементов И третьего и четИ-ИЛИ предьщущего разряда, выход ре-вертого разрядов соединены с вторыми

зервного триггера соединен с вторымвходами первых элементов ИЛИ соответвходом второй группы входов элемен-ствующего разряда, R-вход резервного

та И-ИЛИ четвертого разряда, инверс-триггера соединен с выходом элемента

иый и прямой выходы вторьпс элементов Q И-НЕ, выходы элементов И-ИЛИ второго,

ИЛИ каждого, кроме первого, разрядатретьего и четвертого разрядов являсоединены с первыми входами соответ-ются соответствующими выходами устственно первой и второй групп входовройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1688405A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Счетчик импульсов | 1985 |

|

SU1261112A1 |

| Счетчик импульсов | 1986 |

|

SU1325688A1 |

| Счетчик импульсов | 1983 |

|

SU1187263A1 |

| Счетчик импульсов | 1985 |

|

SU1274153A2 |

| Устройство для умножения | 1988 |

|

SU1501047A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения повышение ремонтопригодности. Это достигается за счет использования .резервного .триггера и дополнительных логических элементов (ЛЭ) в каждом основном разряде, что обеспечивает автоматическую замену отказавшего основного триггера любого из 4 разрядов путем подачи на соответствующий управляющий вход сигнала логического нуля. Устройство содержит разряды 1-4, триггеры разрядов 5.1-5.4, резервный триггер 5.5, ЛЭ: И-НЕ 6, И-Шта 7.1-7.4, НЕ 9.1-9.4, ИЛИ 10.110.4 и-11.2-11.4 и ЛЭ И 8.1-8.4, И 8.1-8.4, 12.2-12.4 и 13, 14; управляющие входы 15-18 для отключения отказавшего триггера. В устройстве осуществляется перестроТйка логической структуры при отказе одного из I разрядов, что обеспечивает работоспособность логических блоков уст .ройств автоматики и вычислительной техники без замены данной интегральной схемы. 1 ил. сд

| Счетное устройство | 1976 |

|

SU616712A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник по интегральным микросхемам, /Под ред | |||

| В.В | |||

| Тарабрина | |||

| М.: Энергия, 1980, с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

Авторы

Даты

1986-11-23—Публикация

1985-05-22—Подача