Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники в качестве базового элемента с повышенной надежностью функционирования.

Целью изобретения является повышение надежности устройства.

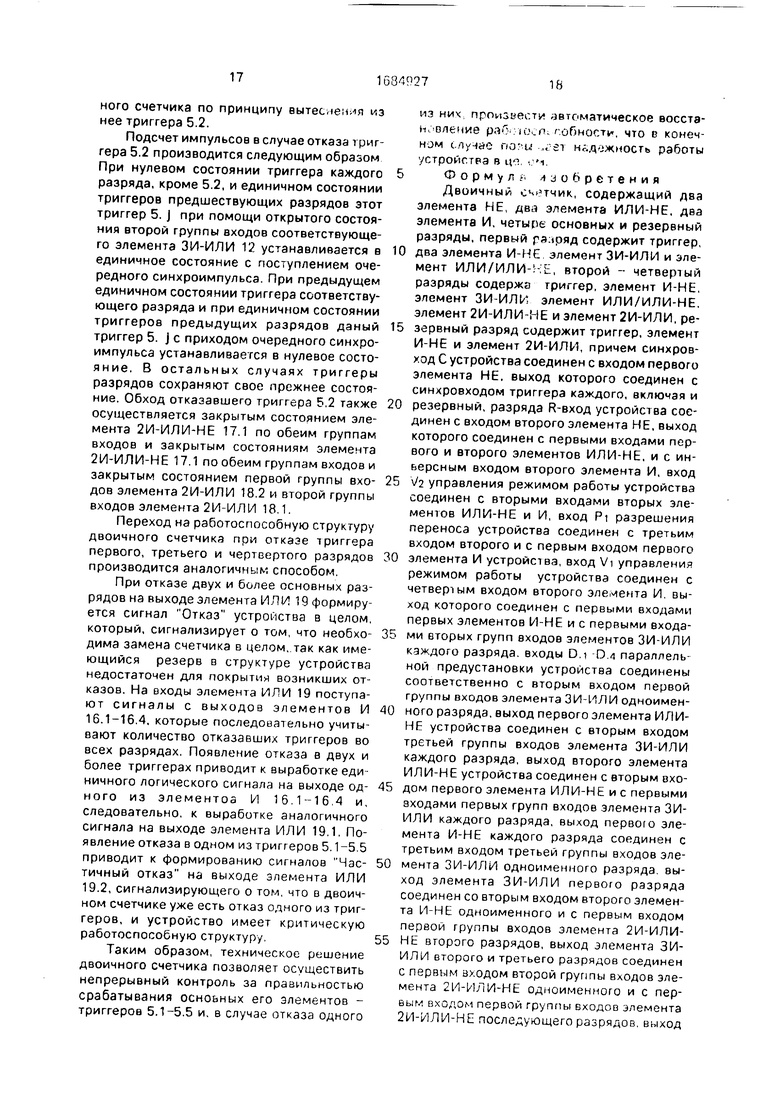

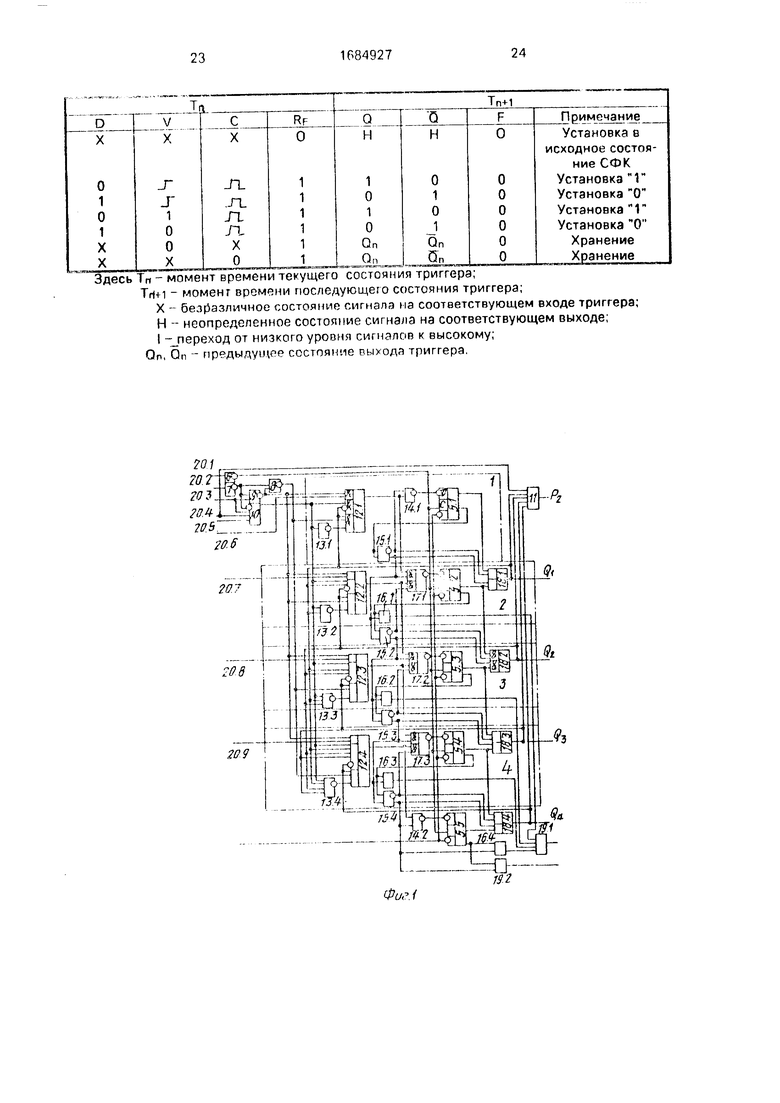

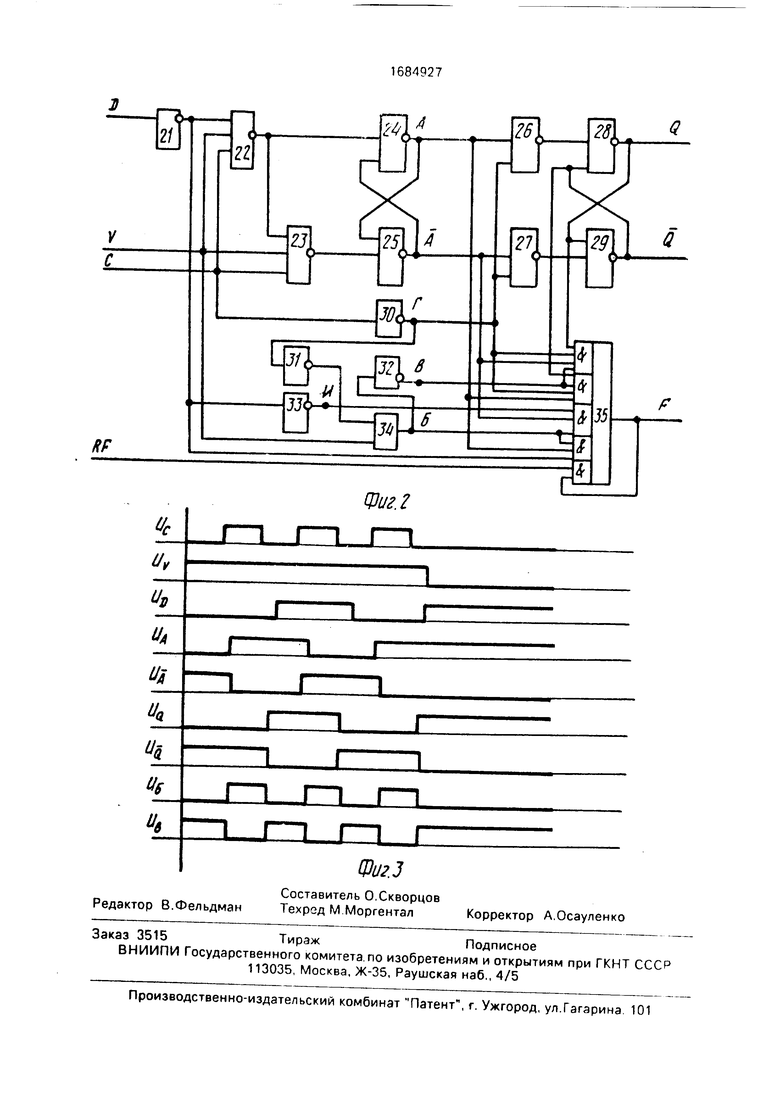

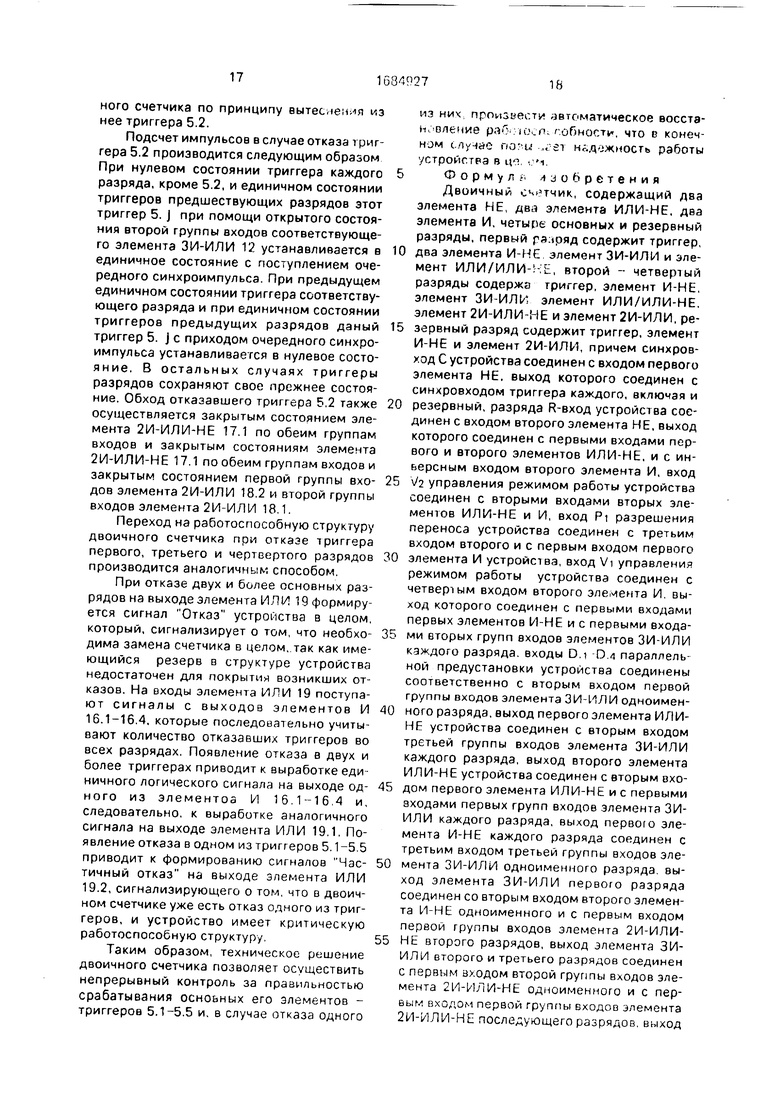

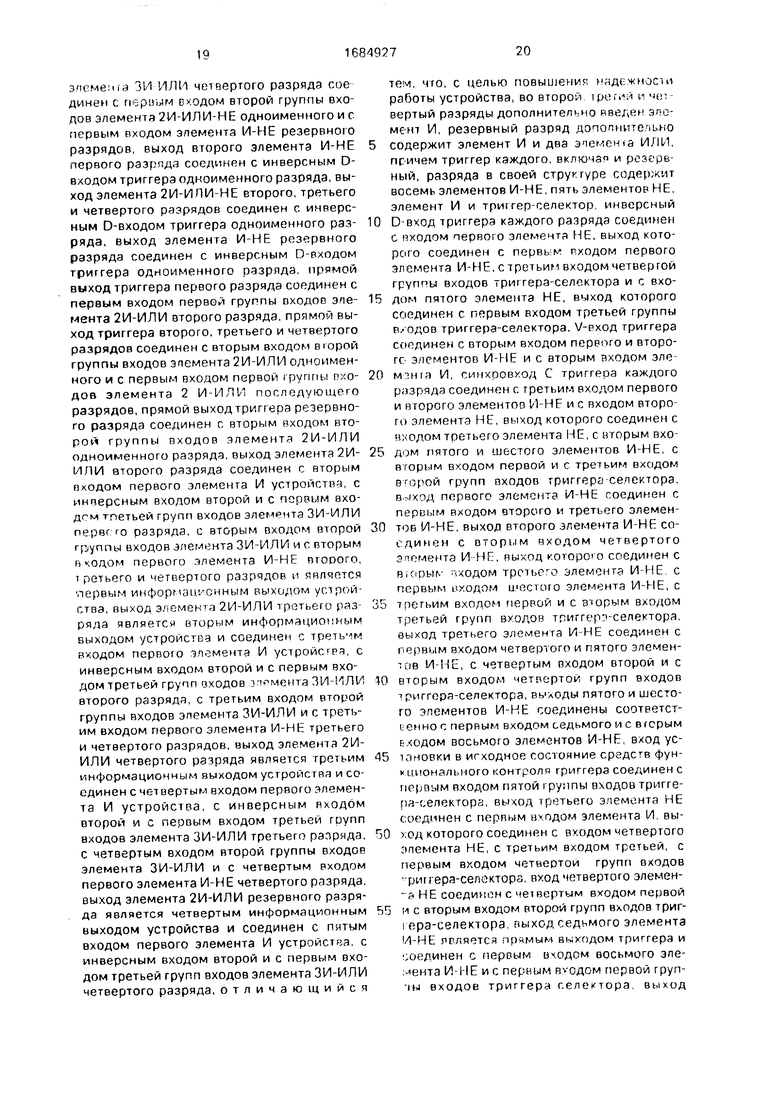

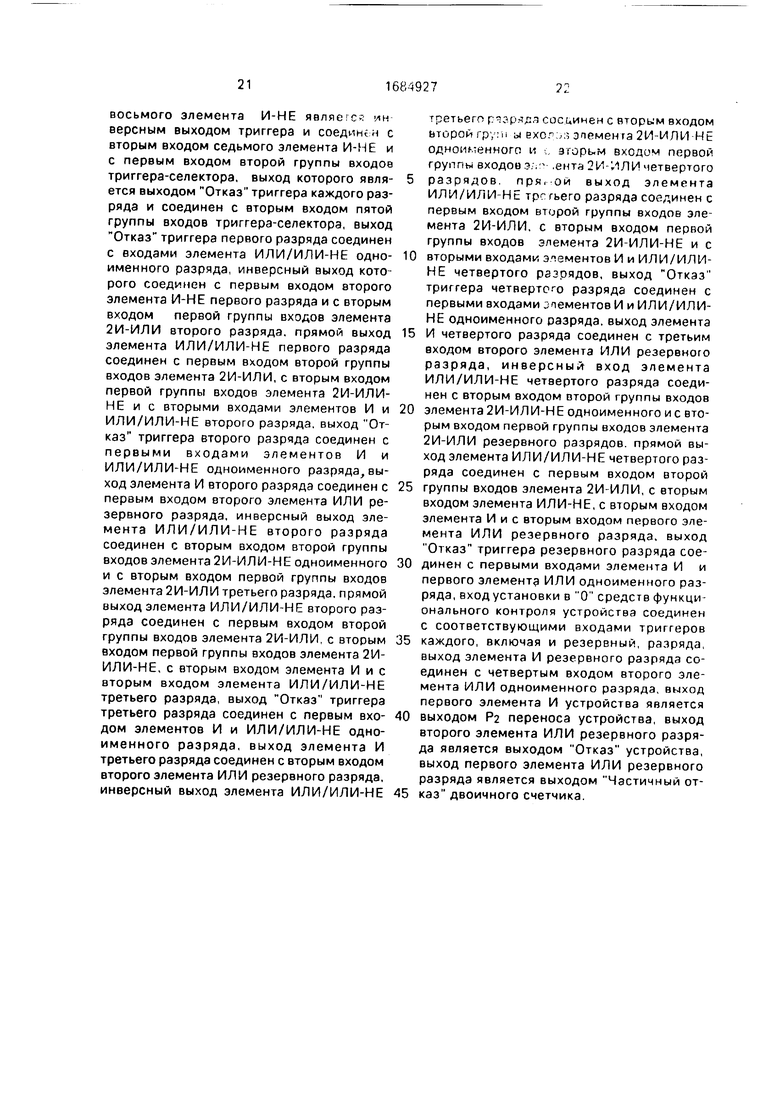

На фиг. 1 приведена логическая структура предлагаемого двоичного счетчика; на фиг.2 - функциональная схема триггера каждого разряда; на фиг.З - временная диаграмма работы триггера.

Двоичный счетчик содержит основные разряды 1-4. триггеры 5.1-55 основных и резервного разрядов, первый 6 и второй 7 элементы НЕ устройства, первый 8 и второй

9 элементы ИЛИ-НЕ устройства, первый 10 и второй 11 элементы И устройства, элементы ЗИ-ИЛИ разрядов 12.1-12.4, первые элементы И-НЕ 13.1-13.4 разрядов, вторые элементы И-НЕ 14.1-14.2 разрядов, элементы ИЛИ/ИЛИ-НЕ 15.1-15.4 разрядов, элементы И 16.1-16.4 разрядов, элементы 2 И-ИЛИ-НЕ 17.1-17.3 разрядов, элементы 2 И-ИЛИ 18.1-18.4 разрядов, первый 19.1 и второй 19.2 элементы ИЛИ резервного разряда.

Входы С 20.1 и Р 20.2 устройства соединены соответственно с входами первого 6 и второго 7 элементов НЕ устройства, выходы которых соединены соответственно с синх- ровходами триггеров 5.1-5.5 каждого разряда, с первым входом элемента ИЛИ-НЕ 8, с

О 00

N ю го VI

первым входом элемента ИЛИ-НЕ 9 и с инверсным входом элемента ИЛИ-НЕ. Вход V2 20.3 устройства соединен с вторыми входами элементов ИЛИ-НЕ 9 и И 10. Вход Pi 20.4 разрешения переноса устройства соединен с первым входом элемента И 11 и третьим входом элемента И 10, четвертый вход которого соединен с входом Vi 20.5 управления режимом работы устройства. Информационные входы D.1-D.4 20.6-20.9 устройства соединены соответственно с вторыми входами первых групп входов соответствующих им элементов ЗИ-ИЛИ 12..4.

Выход элемента ИЛИ-НЕ 9 соединен с первыми входами первых групп входов элементов ЗИ-ИЛИ 12.1-12.4 каждого разряда и с вторым входом элемента ИЛИ-НЕ 8. выход которого соединен с вторыми входами третьих групп входов элементов ЗИ-ИЛИ каждого разряда. Выход элемента И 10 соединен с первыми входами вторых групп входов элементов ЗИ-ИЛИ 12.1-12.4 и элементов И-НЕ 13.1-13.4 каждого разряда. Выходы элементов И-НЕ 13.1-13.4 соединены с третьими входами третьих групп входов соответствующих элементов ЗИ-ИЛИ 12.1-12.4, выходы которых соединены соответственно с вторым входом элемента И-НЕ 14.1 и с первым входом первой группы входов элемента 2И-ИЛИ-НЕ 17,1, с первым входом второй группы входов элемента 2И- ИЛИ-НЕ 17.1 и с первым входом первой группы входов элемента 2И-ИЛИ-НЕ 17.2, с первым входом второй группы входов элемента 2И-ИЛИ-НЕ 17.2 и с первым входом первой группы входов элемента 2И-ИЛИ- НЕ 17.3, с первым входом второй группы входов элемента 2И-ИЛИ-НЕ 17.3 и с первым входом элемента И-НЕ 14.2.

Выход элемента И-НЕ 14,1 соединен с инверсным D-входом триггегра 5.1, прямой выход которого соединен с первым входом первой группы входов элемента 2И-ИЛИ 18.1. Выход F Отказ триггера 5.1 соединен с входами элемента ИЛИ/ИЛИ-НЕ 15.1, прямой и инверсный выходы которого соединены соответственно с первым входом второй группы входов элемента 2И-ИЛИ

18.1,с вторым входом первой группы входов элемента 2И-ИЛИ-НЕ 17.1 и с вторыми входами элементов И 16.1 и ИЛИ/ИЛИ-НЕ

15.2,с первым входом элемента И-НЕ 14.1 и с вторым входом первой группы входов элемента 2И-ИЛИ 18.1.

Выход элемента 2И-ИЛИ-НЕ 17.1 соединен с инверсным D-входом триггера 5.2, прямой вход которого соединен с вторым входом второй группы входов элемента 2И- ИЛИ 16.1 и с первым входом первой группы входов элемента 2И-ИЛИ 18.2. Выход F Отказ триггера 5.2 соединен с первыми входами элементов И 16.2 и ИЛИ/ИЛИ-НЕ 15.2. Выход элемента И 16,1 соединен с первым входом элемента ИЛИ 19.1. Прямой выход

элемента ИЛИ/ИЛИ-НЕ 15.2 соединен с первым входом второй группы входов элемента 2И-ИЛИ 18.2, с вторым входом первой группы входов элемента 2И-ИЛИ-НЕ 17.2 и с вторыми входами элементов И 16.2

0 и ИЛИ/ИЛИ-НЕ 15.3. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15.2 соединен с вторым входом второй группы входов элемента 2И-ИЛИ-НЕ 17.1 и с вторым входом первой группы входов элемента 2И-ИЛИ 18.2.

5Выход элемента 2И-ИЛИ-НЕ 17.2 соединен с инверсным D-входом триггера 5.3. прямой выход которого соединен с вторым входом второй группы входов элемента 2И- ИЛИ-НЕ 18.2 и с первым входом первой

0 группы входов элемента 2И-ИЛИ 18.3. Выход F Отказ триггера 5.3 соединен с первыми входами элементов И 16.2 и ИЛИ/ИЛИ-НЕ 15.3. Выход элемента И 16.3 соединен с вторым входом элемента

5 ИЛИ 19.1. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15.3 соединен с вторым входом второй группы входов элемента 2И- ИЛИ-НЕ 17.2 и с вторым входом первой группы входов элемента 2И-ИЛИ 18.3. Пря0 мой выход элемента ИЛИ/ИЛИ-НЕ 15,3 соединен с первым входом второй группы входов элемента 2И-ИЛИ 18.3, с вторым входом первой группы входов элемента 2И- ИЛИ-НЕ 17.3 и с вторыми входами элемен5 тов И 16.3 и ИЛИ/ИЛИ-НЕ 15.4.

Выход элемента 2И-ИЛИ-НЕ 17.3 соединен с инверсным D-входом триггера 5.4, прямой выход которого соединен с вторым входом второй группы входов элемента 2И0 ИЛИ 18.3 и с первым входом первой группы входов элемента 2И-ИЛИ 18.4. Выход F Отказ триггера 5.4 соединен с первыми входами элементов И 16.3 и ИЛИ/ИЛИ-НЕ 15.4. Выход элемента И 16.3 соединен с третьим

5 входом элемента ИЛИ 19.1. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15.4 соединен с вторым входом второй группы входов элемента 2И-ИЛИ-НЕ 17.3 и с вторым входом первой группы входов элемента 2И-ИЛИ

0 18.4. Прямой выход элемента ИЛИ/ИЛИ-НЕ 15.4 соединен с первым входом второй группы входов элемента 2И-ИЛИ 18.4, с вторым входом элемента И-НЕ 14,2 и с вторыми входами элементов И 16.4 и ИЛИ 19.2,

5Выход элемента И-НЕ 14.2 соединен с

инверсным D-входом триггера 5,5. прямой выход которого соединен с вторым входом второй группы входов элемента 2И-ИЛИ 18,4. Выход F Отказ триггера 5,5 соединен с первыми входами элементов И 16 4 и ИЛИ

19.2. Выход элемента И 16.4 соединен с четвертым входом элемента ИЛИ 14 1, выход которого является выходом Отказ устройства. Выход элемента ИЛИ 19.2 является выходом Частичный отказ устройства.

Выход элемента 2И-ИЛИ 18.1 является первым информационным выходом Qi устройства и соединен с вторым входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛ И 12.1, с вторыми входами вторых групп входов элементов ЗИ-ИЛИ 12,2-12.4 и с вторыми входами элементов И-НЕ 13.2-13.4.

Выход элемента 2И-ИЛИ 18.2 является вторым информационным выходом Q2 устройства и соединен с третьим входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.2, с третьими входами вторых групп входов элементов ЗИ-ИЛИ

12.3и 12.4 и с третьими входами элементов И-НЕ 13.3 и 13.4.

Выход элемента 2И-ИЛИ 18.3 является третьим информационным выходом Оз устройства и соединен с четвертым входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.3. с четвертым входом второй группы входов элемента ЗИ-ИЛИ

12.4и с четвертым входом элемента И-НЕ 13.4.

Выход элемента 2И-ИЛИ 18.4 является четвертым информационным выходом CU устройства и соединен с пятым входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.4. Выход элемента И 11 является выходом Р2 переноса устройства.

Триггер каждого разряда (см. фиг.2) содержит первый элемент НЕ 21. элементы И-НЕ 22-29, второй 30, третий 31, четвертый 32 элементы НЕ, элемент И 33, пятый 34 элемент НЕ и триггер-селектор 35.

Вход D триггера каждого разряда соединен с входом элемента НЕ 21, выход которого соединен с входом элемента И-НЕ 22, второй и третий входы которого соединены соответственно с входами V и С триггера, которые дополнительно соединены с входом элемента И-НЕ 23 и с входом элемента И 33. с входом элемента И-НЕ 23 и с входом элемента НЕ 30.

Выход элемента НЕ 21 соединен с входом элемента НЕ 34 и с входом четвертой группы входов триггера-селектора 35 Выход элемента И-НЕ 22 соединен с входом

элемента И-НЕ 24 и с входом элемента И-НЕ 23, выход которого соединен с входом эле- м«.,1тэ И НЕ 2П ВЫУОР, элемента НЕ 30 соединен с вторыми ,1ми элементов И-НЕ 26 и 27, с первой и второй групп входов триггера- чектора и с входом элемента НЕ 31 которою соединен с входом элемента 11 33. Выход элемента И 33 соединен с входами третьей и четвертой

групп входов триггера-селектора 35 и с входом элемента НЕ 32. выход которого соединен с входами первой и второй групп входов триггера-селекгоиа 35. Выход элемента НЕ 34 соединен с входом третьей группы входов триггера-селемора 35. первый вход пятой группы входов которого соединен с входом PF установки в исходное состояние средств функционального контроля триггера.

Выход элемента И-НЕ 24 соединен с

входом элементов И-НЕ 25 и 26 и с входами второй и четвертой групп входов триггера- селектора 35. Выход элемента И-НЕ 25 соединен с входом элементов И-НЕ 24 и 27 и с

входами первой и третьей групп входов триггера-селектора 35. Выходы элементов И-НЕ 26 и 27 соединены соответственно с входами элементов И-НЕ 28 и 29.

Выход элемента И-НЕ 28 является прямым выходом триггера и соединен с входом элемента И-НЕ 29 и с входом первой группы входов триггера-селектора 35. Выход элемента И-НЕ 29 является инверсным выходом триггера и соединен с входом элемента

И-НЕ 28 и с входом второй группы входов триггера-селектора 35. выход которого является выходом Отказ триггера и соединен с вторым входом пятой группы входов триггера-селектора 35.

Триггер-селектор может быть реализован, например, на элементе И-ИЛИ с пятью группами входов И, из которых четыре являются группами входов установки в единицу, а первый, второй входы пятой группы входов И элемента И-ИЛИ соединены соответственно со входом установки нуля триггера-селектора и с входом элемента И-ИЛИ, выход которого является выходом триггераселектора 35.

В процессе своего функционирования триггер каждого разряда контролируется встроенными средствами функционального контроля, обеспечивая при этом более достоверную информацию на выходах каждого триггера.

Рассмотрим функциональное назначение и принцип работы триггера каждого разряда

Элементы И-НЕ 22-25 образуют схему основного триггера, а элементы И-НЕ 26-29 - схему вспомогательного триггера.

Элемент НЕ 30 предназначен для организации двухтактного режима работы триггера при наличии одного синхровхода - С. Кроме того, на выходе элемента НЕ 30 вырабатывается сигнал сравнения сигналов на противоположных плечах (выходах) основного и вспомог ельного триггеров (см. фиг.2, точка А и Q, точка А и Q) в режиме хранения информации.

Элемент НЕ 32 формирует функции V:C через время 4ТСр срабатывания элементов НЕ 30 и 31, элемента И 33, а также самого элемента НЕ 32 с момента поступления положительного фронта синхроимпульса на С- входе триггера, который является сигналом сравнения для первой и второй групп входов триггера-селектора 35, контролирующего правильность срабатывания логических элементов второй ступени (вспомогательно го триггера) триггера.

Элементы НЕ 21, 31 и 34 осуществляют инвертирование сигналов на С и D-входах триггера соответственно, необходимых для формирования соответствующих аргументов функционала контроля.

Элемент И 33 осуществляет формирование функции V- С через время ЗТСр срабатывания элементов НЕ 30 и 31, а также самого элемента И 33 с момента появления отрицательного фронта синхроимпульса на С-вхо- де триггера и формирует на своем выходе сигнал сравнения для третьей и четвертой групп входов триггера-селектора 35, контролирующего в этом случае правильность срабатывания логических элементов первой ступени (основного триггера) триггера каждого разряда.

Триггер-селектор 35 осуществляет на своих группах входов контроль правильности срабатывания всех логических элементов структуры триггера. В случае нарушения логики функционирования (отказ какого-либо логического элемента структуры триггера) на выходе триггера-селектора 35 формируется сигнал Отказ, который посредством своей обратной связи через пятую группу входов осуществляет так называемый эффект самозахвата, т.е. устанавливается в устойчивое состояние логической единицы.

В общем случае на входах триггера-селектора 35 реализуется функционал отказа, который можно представить следующим аналитическим выражением:

F (V С) D A- V(V -С) -D A V(V С)

А QV(V С) А Q,

(1)

где V - единичное состояние сигнала на входе триггера;

С - единичное состояние сигнала на синхровходе триггера;

D - единичное состояние сигнала на D- входе триггера;

А, А - единичное и нулевое состояние сигналов сответственно в точках А и А на фиг,2;

Q, Q - состояние сигнала на прямом и инверсном выходах триггера.

Триггер каждого разряда работает следующим образом.

После включения питания на Rp-вход триггера (см. фиг.2) подается нулевой уро- вень сигнала для установки в исходное состояние средств функционального контроля, так как в силу случайного характера переходных процессов во время включения питания триггер-селектор 35 может установиться в единичное состояние, соответствующее формированию сигнала Отказ триггера в целом.

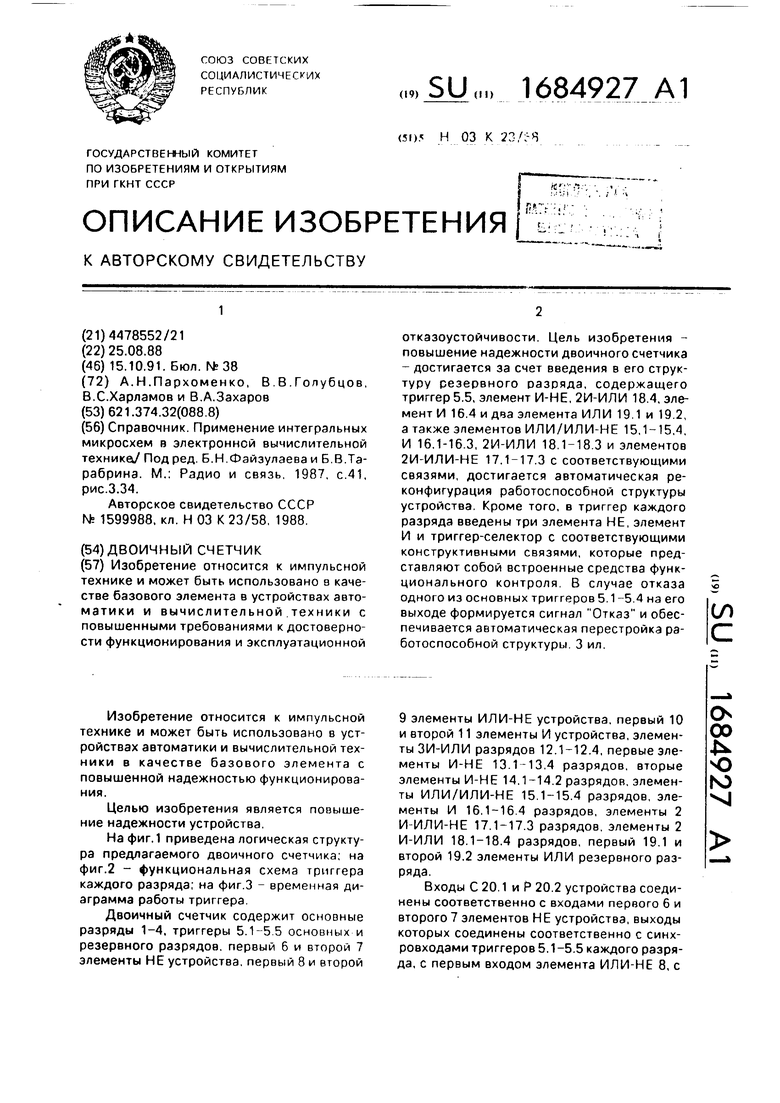

Далее при исправном состоянии всех логических элементов работа триггера каж- дого разряда подчиняется (соответствует) закону функционирования, приведенному в сокращ иной табл. переходов триггера каждого разряда.

В процессе своего функционирования первая ступень триггера подчиняется закону, представленному следующим аналитическим выражением:

40

(V С) D А 1 V (V С) D А 1, (2)

где V - состояние сигнала на V-входе триггера;

С - единичное состояние сигнала на синхровходе триггера;

D, D - единичное и нулевое соответственно состояния сигналов на D-входе триггера;

А, А - единичное и нулевое соответст- венно состояния сигналов в точках А и А на фиг,2 триггера.

За выполнением условий выражения (2) следят третья и четвертая группы входов триггера-селектора 35.

В процессе своего функционирования вторая ступень (вспомогательный триггер) триггера каждого разряда подчиняется закону, который можно представить следующим аналитическим выражением:

(V С) А Q (V С) A -Q- 1. (3)

где V С - единичное состояние .ч r.i выходе лемента НЕ 32;

Q, Q - состояния сигналов на прямом и инверсном соответственно выходах триггера каждого разряда.

За выполнением условий выражения (3) следят первая и вторая группы входов триггера-селектора 35

Функционал отказа любого из погиче- ских элементов первой ступени (основного триггера), реализованных в техническом решении триггера каждого разряда можно представить следующим аналитическим вы- рэжением:

F (V -С) D A- V(V С) D А (4)

В случае нарушения условий функииониро- вания, представленных в выражении (2), на выходе триггера-селектора 35 уже в момент срабатывания элементов первой ступени вырабатывается сигнал Отказ триггера каждого разряда

Функционал отказа любою из логических элементов втооой ступени (вспомогательного триггера), реализованный в техническом решении триггера каждого разряда, можно прсдгтавить выражением

F (V -С) А Q V(V С) А О (5)

В случае нарушение условий Функционирования, представленных в выражении (3) нэ выходе триггерэ-селектооа 35 также аырл батывается сигнал Отказ триггера кэждо го разряда.

Рассмотрим последовательность срабатывания всех элементов логической структуры предлагаемого тоиггерэ в его трех основных режима функционирования: хранение, установка 1 и установка О.

В режиме Установка 1 (табл 1, п 4) по D-входу с поступлением положительного фронта синхросигнала на С-вход триггера на выходе элемента И-НЕ 22 через время ТСр срабатывания эпемента И-НЕ 22 установится сигнал логического нуля Следовэ- тельно, через время 2ТСр срабатывание с момента поступления положительного фронта сигнал нэ С-вход на выходах второго и третьего элементов И-НЕ 23 и 24 установятся сигналы логической единицы и через время ЗТСр срабатывания на выходе четвертого элемента И-НЕ 25 - сигнзп логического нуля. Таким образом, через время 3Ttp в точке А (см. фиг 1) будет установлено состояние логической единицы, з в . А ;о ,).е то i.-ir-v.-HO нуч Контроль пра

Ч.1 , .. ;).Г.:,1. НИ ОЛе1/ М1ТГ В пСрНОЙ t ,- t р 1 r.J ), . «;/;(, С 4: Чр««Л,а ОС/ ССГРЛ- - -с/ г тррРц . , чьненич с выхода зле v; иг,. I/I J3 кг: .; псяялис гея также ч.-рез ЗТ-р tp ib-j занич элементов НЕ 30

31и ормо о э/ е -мтз И 33. Если п ходе комсогч будет пыполнено условие (2), то третья и ч твестя входов триггера електорз 35 не , с i я т на выход его сигнал логической eiT mitbi При нарушении ,итМг1 , П рованч элементами первой ступени, т выполнится условие (4), нл выходе триггера селектора 35 вырабатывается сиг (ал ло и (ескои единицы,который через пятую группу входов устанавливает григгер-сепектор 35 в устойчивое состояние лгнической единицы, сигнализируя об отказе первой ступени триггера любого из раз- рчдлп.

С приходом на С-вхсд триггера отрица тельно о фронта синхроимпульса состояние первой ступени передается во вторую ступень, те пятый элемент И НЕ 26 установится в состояние логически о нуля з шесюй элемент И НЕ 27 останется в состоянии тническои единицы ча сзоем выходе Следовательно, чере время ЗТ-р срабатывания с момента поступленич отрицательного фронта синхроимпульса на седьмого элемента И НЕ 23 установится сигнал логической единицы а через время 4Т, р из выходе элемента И-НЕ 29 сигнал ло ичсского мула Контроль правильности срабатывания логических элементов второй производи1ся стробом сравнения, коюрый псявпчется нэ выходе элемента НЕ

32через ВОРМЯ 411 срабатыванич с момен- ;а появления отрица1ельно1О фронта на синхоо ходе триггера При выполнении ус ловий (3) на триггера-селектора 35 сигнал Отказ не сформируется В противном случае, т е при выполнении условия (5), на его вылоае будет сформирован сигнал Отказ одного или нескольких лотческих э,1 мснтов второй ступени триггера

В режиме Установка 0 (табп 1 п 5) по .0 в оду с приходом попожительног о фронта синхросчгнолэ на вьисдеэлеменга И-НЕ 22 уст- ночитсм сигнал логической единицы, а на выходе элемента И-НЕ 23 - сигнал логического нуля, который через время 2Тср солпап. вэния с момента появления поло- /М1Г льного фронта синхроимпульса приведет формированию на выходе элемента И-НЕ 24 сигно та ло-ической единицы Через о рем ч 2 на вы .G,.;J элемента И-НЕ 24 будет сфсрмиозг-лн сиги, л /.огического нуля Кон- TpoiL, трГ1-п ьности срабатывания логических элементов первой ступени будет проведен на входах третьей и четвертой групп входов триггера-селектора 35 сигналом сравнения с выхода элемента И 33, который будет сформирован через время ЗТСр срабатывания элементов НЕ 30 и 31, а также самого элемента И 33. При выполнении условий (2) сигнал Отказ на выходе триггера-селектора 35 не появится, в противном случае он будет сформирован, сигнализируя об отказе одного или нескольких логических элементов первой ступени триггера.

Функционирование и контроль правильности срабатывания логических элементов второй ступени производится следующим образом. При появлении на синхровходе триггера отрицательного фронта синхросигнала состояние основного триггера (первой ступени) будет передано во вторую ступень по следующей логической ветви: через 2ТСр на выходе элемента И-НЕ 27 будет сформирован сигнал логического нуля. Через время ЗТСр на выходе элемента И-НЕ 29 - сигнал логической единицы и через время 4ТСр на выходе элемента И- НЕ 28 - сигнал логического нуля. Контроль правильности срабатывания будет произведен сигналом сравнения с выхода элемента НЕ 32, который будет сформирован также через время 4Тср срабатывания элементов НЕ 30, 31, И 33 и самого элемента НЕ 32. При выполнении условий (3) сигнал Отказ на выходе триггера-селектора 35 сформирован не будет, В противном случае, т.е. при выполнении условий (5), сигнал Отказ формируется на выходе триггера-селектора 35, сигнализируя об отказе одного или нескольких логических элементов второй ступени триггера.

В режиме хранения (табл.1, п,7), т.е. при наличии нулевого потенциала на синхровходе триггера, с выходов элементов И-НЕ 22 и 23 на входы элементов И-НЕ 24 и 25 поступают сигналы логической единицы, подтверждая предыдущее состояние триггера первой ступени. С выходов элементов И-НЕ 26 и 27 на входы элементов И-НЕ 28 и 29 также поступают сигналы логической единицы, подтверждая предыдущее состояние триггера второй ступени.

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом. Через время ТСр срабатывания элемента НЕ 30 производится сравнение состояний в точке А с состоянием сигнала на прямом выходе триггера и в точке А с состоянием сигнала на инверсном выходе триггера. Такое же сравнение производится через время 4ТСр с момента появления сигнала логического нуля на синхровходе триггера стробом сравнения с выхода элемента НЕ 32.

Функционирование и контроль правильности срабатывания логических элементов структуры триггера каждого разряда в остальных режимах его функционирования (табл., п.п.2,3 и 7) производится аналогичным образом.

Таким образом, в процессе подсчета

0 импульсов триггер каждого разряда непрерывно контролируется на правильность срабатывания и, в случае отказа формирует на своем выходе Отказ, сигнал высокого логического уровня.

5Двоичный счетчик, содержащий в каждом разряде вышеописанный триггер, рабо- TcieT следующим образом.

Для установки двоичного счетчика в исходное состояние на вход RF устройства

0 подают сигнал нулевого логического уровня и затем на вход R устройства подается также сигнал нулевого логического уровня, а на синхровход С устройства - импульс. При этом на выходе элемента ИЛИ-НЕ 8 выраба5 тывается сигнал нулевого логического уров- ня, который закрывает третьи группы входов элементов ЗИ-ИЛИ 12.1-12.4, первые и вторые группы входов которых также закрыты следующими сигналами: первые

0 группы входов закрыты нулевым логическим уровнем сигнала с выхода элемента ИЛИ-К 9, так как на входе V2 устройства -сигнал логической единицы, а вторые группы входов - нулевым сигналом с выхода

5 элемента И 10, так как на его инверсном входе присутствует сигнал логической единицы с выхода элемента НЕ 7. Таким образом, на выходах элементов ЗИ-ИЛИ 12,1-12.4 формируется сигнал логического

0 н/ля, что приводит к формированию на выходах элементов И-НЕ 14.1 и 14.2, 2И-ИЛИ- НЕ 17.1-17.3 сигналов логической единицы. Следовательно, с приходом синхроимпульса с С-входа устройства через элемент НЕ 6

5 триггеры 5.1-5,4 установятся в состояние логического нуля.

При исправном состоянии всех основных триггеров 5,1-5.4 на их F-выходах присутствует сигнал логического нуля. В этом

0 случае сигналами с инверсных выходов элементов ИЛИ/ИЛИ-НЕ 15.1-15.4 открыты следующие логические элементы устройства: элемент И-НЕ 14,1 и первая группа входов элемента 2И-ИЛИ 18.1, вторая группа

5 входов элемента 2И-ИЛИ-НЕ 17.1 и первая группа входов элемента 2И-ИЛИ 18.2, вторая группа входов элемента 2И-ИЛИ-НЕ 17.2 и первая группа входов элемента 2И- ИЛИ 18.3, вторая группа входов элемента 2И-ИЛИ-НЕ 17,3 и первая группа входов

элемента 2И-ИЛИ 18.4 Одновременно с этим закрываются следующие лс/i v iv элементы устройства: первая группа ь .щл) элементов 2И-ИЛИ-НЕ 17 1- 17.3, вк,рые группы входов элементов 2И-ИЛИ 16 1 18.4, элементы И 16.1-16.4 и элементы ИЛИ/ИЛИ-НЕ 15.1-15.4.

Рассмотрим два основных режима функционирования двоичного счетчика: установка его предвари rem ная отличное от нуля состояние и подсчет импуьсов

Установка двоичного счетчика в состояние, равное информации на входах D.1-D 4. производится следующим образом На вход V2 устройства подав ся сигнал логическо- го нуля, на вход L. устройства - синхроимпульс отрицательней полярности, на вход R - сигнал логической единицы, на выходы Pi и Vi - сигналы логического нуля и на выходы О.Г-D а, - информация о пред- варительной установке двоичного счетчика

В этом случае открывается первые группы входов элементов ЗИ-ИЛИ 12 1-12.4 и на их выходах формируются сигналы, идентичные сигналам на соответствущих входах D.1-D.4 устройств Эги сигналы через элементы И-НЕ 14.1 21/1-И ПИ-HE 17.1- 17.3 поступают на инверсные D-входы триггеров 5.1 -5 4, которые с приходом син- хроимпульса устанавлио&ются в состояния, равные состояниям на соответствующих входах D.1.-D.4 устройства Значения состояний триггеров 5.1-54 через первые группы входов элементов 2И-ИЛИ 181 184 посту- пают на разрядные выходы Q -Q л, устройства. Выход триггера 5 Ь в этом случае отключен закрытой второй группой входов элемента 2И-ИЛИ 184

Подсчет импульсов поступающих на синхровход С устройства производится по следующей логической ветви предлагаемого двоичного счетчика На выходах R, V2, Pi, Vi при этом присутствуют сигналы логической единицы, а на вход С устройства посту- пают синхроимпульсы

С входа С устройства импульсы поступают через элемент НЕ 6 на синхровходы триггеров 5.1-5.4, которые с приходом каждого синхроимпульса изменяют свое состо- яние в зависимости от предыдущего своего состояния и состояния триггеров предыдущих разрядов.

Рассмотрим пример подсчета синхроимпульсов с предварительной установкой двоичного счетчика в состояние lGr i те перед режимом в двоичный счетчик, были занесены единичные состояния в триггеры 5.1 и 5.4. В этом случае едини состояния с выходов элементов 2I1-L Л И 18 1 и 18 4

открывают следующие элементы счетчика1 третьи группы входов элементен 311 /.111 12 1 и 12 4 (вторые группу г ;; Э) и ve элементов закрыты этими -r i л а ми i i их инверсным вход тм вторые1 пы ьхс дов элементов ЗИ И Л И 12 2 и 12 i j зтормм входам

Триггеры разряде в изменят свои сгс яния (или сохранят предыдущие состою1 . - следующим образом

С приходом синхроимпульса триггер S 1 установится в состояние О, так как всг ри группы элемента ЗИ-ИЛИ 12 1 будут ты (первач группа входов закрыта нуле чь, -1 сигналом с вывода элемента ИЛИ-НЕ 9 ут - рая группа входов единичным сигна ICM с выхода элемента 2И И HI IS 1 на ее ,ер сный вход и третья rpv rina п.ог, ну и т м сигналом с выхода элемента И КГ м Г

С приходом синхроимпульса rj IT , --р, 0 установится в единичос состояние г ik элементе ЗИ-ИЛИ 12 2 откр и л t rpvn па входов с выхода элемента И 10 г df-,, vn p элемента 2И-ИЛИ 18 1 и нупоным п ,т г i -, алом с выхода элемента 2И ИЛИ 14 : ,i инверсный вход Следоватептно i дичич ный уровень сигнала чгиез ITV f-т. ru ( г пу входов элемента ЗИ ИМИ 12 1 и -о группу входов элемента 211 . 1 1 где он инвертируется noci/fi jT ij; epj ный D-вход триггера 5 2 кот рьи-. с грихо- дом синхроимпульга VCT H шлнпз .я в единичное состояние

Триггер 53с приуодом -:ин poи. г, , ьст остается в своем пррч.црм и1, Р с м ттон нии по следую1 им ПРИЧИНЙЧ Ггг пы элемента ЗИ И ПИ Г 3 первая группа входов нулевым v. иг Нолог г -зЫходп элемента ИЛИ-НЕ 9 ргорг.ч ip, ы нулевым сигналом E- -IXO J v т 2И- ИЛИ 18 2 и треть i pvrma n«d/ ( сигналом с выхода гмеыа 2/ И

d3

Следовательно на РЫ-ОД Oic-.fv.Td ЗИ ИЛИ 12 3 будет сформирован г и; mi л о -ич°- ского нуля, который через рторчю группу входов элемента 2И-ИЛИ i 7 Г плрмк дит прежнее нулевое гог гямис триг .ра 53

Триггер 5 4 с приходом гин г оимпульса остается в своем прежнем единичном состоянии по следующим причин В элементе ЗИ-ИЛИ 12.4 в этом сл ае открыта трет.,ч группа входов с вылод н эп м-нтов 2И- ИЛИ 18 4, ИЛИ-ИЕ 8 и Г-Н 1 4 HP: по -е- му триггер 5 4 с при«,одом син «.р.лт.Му пчса останется в пре/ки м единичном с ю -и

Таким образом, с прилиди-л псового синхроимпульса двоичный счетчик примет состояние 101.0, т е изменит свое состоя

ние на V. С приходом второго синхроимпульса предлагаемый двоичный счетчик примет состояние 1011 по следущему алгоритму работы.

Триггер 5.1 установится в единичное со- 5 стояние, так как открыта вторая группа входов элемента ЗИ-ИЛИ 12.1 сигналами с выхода элемента И 10 и с выхода элемента 2И-ИЛИ 18.1 (нулевой сигнал на инверсный вход),Ю

Триггер 5.2 остается в единичном состоянии, так как в этом случае открыта третья группа входов элемента ЗИ-ИЛИ 12.2 сигна- лами с выходов элементов 2И-ИЛИ 18.2, ИЛИ-НЕ 8 и И-Ht 13,2 соответственно,15

Триггер 5.3 остается в нулевое состоянии, так как все три группы входов элементов ЗИ-ИЛИ- 12.3 закрыты сигналами с выходов элементов ИЛИ НЕ 9. 2И-ИЛИ 18.1 и 18.3 соответственно.20

Триггер 5.4 остается в единичном состоянии, так как открыта третья группа входов элемента ЗИ-ИЛИ 12.4 сигналами с выходов элементов 2И-ИЛИ 18.4, ИЛИ-HF 8 и И-НЕ 13.4 соответственно.25

Подсчет третьего, четвертого и т.п. импульсов производится аналогичным образом. При достижении двоичным счетчиком состояния, равного 1111, на его выходе Ра формируется единица переноса, что позво- 30 ляет образовать из нескольких предлагаемых двоичных счетчиков двоичный счетчик большей разрядности.

При отказе какого-либо одного из основных триггеров 5,1-54 на его выходе F 35 появляется сигнал логической единицы, который, поступая на сответствующий элемент ИЛИ/ИЛИ-НЕ 15.1-15.4, приводит к смене сигналов на выходах данного и послеующих элементов ИЛИ/ИЛИ-НЕ, что, в свою 40 очередь, приводит к перестройке (автоматической реконфигурации) работоспособной структуры предлагаемого счетчика. При отказе одного из основных триггеров на выходе элемента ИЛИ 19.2 также формируется 45 сигнал логической единицы, что приводит к формированию сигнала Частичный отказ на соответствующем выходе двоичного счетчика.

Рассмотрим пример, когда отказал 50 триггер 5.2 второго разряда. В этом случае на выходе F триггера 5.2 формируется сигнал логической единицы, что приводит к формированию на инверсных выходах элементов ИЛИ/ИЛИ-НЕ 15.2-15.4 сигналов 55 логического нуля и сигналов логической единицы на их прямых выходах. Так как на прямом выходе элемента ИЛИ/ИЛИ-НЕ 15.4 также сформирован сигнал логической единицы, то на выходе элемента ИЛИ 19.2

появляется сигнал Частичный оп тз П результате смены сигналов на выходах элементов ИЛИ/ИЛИ-НЕ открываются следующие логические элементы счетчика: первые группы входов элементов 2И-ИЛИ-НЕ 17.2 и 17.3, элемент И НЕ 14.2 и вторые группы входов элементов 2И-ИЛИ 18.2-18.4. Одновременно с этим закрываются следующие логические элементы двоичного счетчика: элемент 2И-ИЛИ-НЕ 17.1 по двум группам входов ((Я группа входов сигналом с прямого выхода элемента ИЛИ/ИЛИ-НЕ 15.1 а вторая - сигналом с инверсного выхода элемента ИЛИ/ИЛИ-НЕ i5.2). вторые группы входов элементов 2И- ИЛИ-НЕ 17.2 и 17.3 и первые группы входов элементов 2И-ИЛИ 18.2-18.4.

В режиме зйнесения параллельного кода информации продусганова с входов D. i-D.4 устройства двоичный счетчик в этом случае работает следующим образом.

Сигнал с входа D i устройства через открытую первую группу входои элемента ЗИ- ИЛИ 12.1, элемента И-НЕ 14.1 поступает на инверсный D-вход триггера 5.1. Сигнал с входа D.2 устройства через открытые первую группу входов элемента ЗИ-ИЛИ 12.1 и первую группу входов элемента 2И-ИЛИ-НЕ 17.2 поступает на инверсный D-вход триггера 5.3. Сигнал с входа О.з устройства через открытые первую ipynny входов элемента ЗИ-ИЛИ 12.3 и первую группу входов элемента 21/1-ИЛИ-НЕ 17.3 поступает на инверсный D-вход триггера 5.4 Сигнал с входа D.A устройства через открытую первую группу входов элемента ЗИ-ИЛИ 12.4 и элемент И-НЕ 14.2 поступает на инверсный D-вход триггера 5.5. С приходом на вход С устройства синхроимпульса отрицательной полярности триггеры 5 1, 5.3- 5.5 устанавливаются в состояния, соответствующие состояниям на входах D.rD,,; устройства. Сигнал с прямого выхода триггера 5.1 через открытую первую группу входов элемента 2ИЧ4ЛИ 18.2 поступает на разрядный выход Q.1 устройства. Сигнал с прямого выхода триггера 5.3 через открытую вторую группу входов элемента 2И-ИЛИ 18.2 поступает на разрядный выход Q,2 устройства. Сигналы с прямых выходов триггеров 2И-ИПИ 18.3 и 18.4 на разрядные выходы О.з и Q.A устройства соответственно Выход триггера 5.2 заблокирован закрытой второй группой входов элемента 2И-ИЛИ 18.1 и первой группой входов элемента 2И-ИЛИ 18,2.

Таким образом, в результате формирования сигнала из выходе трип ера 5.2 Отказ происходи1- автоматическая перестройка работоспособной структуры двоичного счетчика по принципу вытеснения из нее триггера 5.2.

Подсчет импульсов в случае отказа риг- гера 5.2 производится следующим образом При нулевом состоянии триггера каждого разряда, кроме 5.2, и единичном состоянии триггеров предшествующих разрядов этот триггер 5. J при помощи открытого состояния второй группы входов соответствующего элемента ЗИ-ИЛИ 12 устанавливается в единичное состояние с поступлением очередного синхроимпульса. При предыдущем единичном состоянии триггера соответствующего разряда и при единичном состоянии триггеров предыдущих разрядов даный триггер 5. j с приходом очередного синхроимпульса устанавливается в нулевое состояние. В остальных случаях триггеры разрядов сохраняют свое прежнее состояние. Обход отказавшего триггера 5.2 также осуществляется закрытым состоянием элемента 2И-ИЛИ-НЕ 17.1 по обеим группам входов и закрытым состояниям элемента 2И-ИЛИ-НЕ 17.1 по обеим группам входов и закрытым состоянием первой группы входов элемента 2И-ИЛИ 18.2 и второй группы входов элемента 2И-ИЛИ 18.1.

Переход на работоспособную структуру двоичного счетчика при отказе триггера первого, третьего и чертвертого разрядов производится аналогичным способом.

При отказе двух и более основных разрядов на выходе элемента ИЛИ 19 формируется сигнал Отказ устройства в целом, который, сигнализирует о том, что необходима замена счетчика в целом, так как имеющийся резерв в структуре устройства недостаточен для покрытия возникших отказов. На входы элемента ИЛИ 19 поступают сигналы с выходов элементов И 16.1-16.4. которые последовательно учитывают количество отказавших триггеров во всех разрядах. Появление отказа в двух и более триггерах приводит к выработке единичного логического сигнала на выходе одного из элементоа И 16.1-16,4 и, следовательно, к выработке аналогичного сигнала на выходе элемента ИЛИ 19.1, Появление отказа в одном из триггеров 5.1-5.5 приводит к формированию сигналов Частичный отказ на выходе элемента ИЛИ 19.2, сигнализирующего о том, что в двоичном счетчике уже есть отказ одного из триггеров, и устройство имеет критическую работоспособную структуру,

Таким образом, техническое решение двоичного счетчика позволяет осуществить непрерывный контроль за правильностью срабатывания основных его элементов - триггеров 5.1-5.5 и. в случае отказа одного

из них произвести автоматическое восста- Ис-вление рл. ю,.л, гобности, что в конечном 1.лунао no-u ,tSi нлдожмость работы устройства в ц« см Формул - 4уо6ретения

Двоичный счетчик, содержащий два элемента НЕ, два элемента ИЛИ-НЕ, два элемента И, четыре основных и резервный разряды, первый рд.фяд содержит триггер,

0 два элемента И-НЕ элемент ЗИ-ИЛИ и элемент ИЛИ/ИЛИ- -. Е, второй - четвертый разряды содержа триггер, элемент И-НЕ, элемент ЗИ-ИЛИ элемент ИЛИ/ИЛИ-НЕ. элемент 2И-ИЛИ-МЕ и элемент 2И-ИЛИ, ре5 зервный разряд содержит триггер, элемент И-НЕ и элемент 2И-ИЛИ, причем синхров- ход С устройства соединен с входом первого элемента НЕ. выход которого соединен с синхровходом триггера каждого, включая и

0 резервный, разряда R-вход устройства соединен с входом второго элемента НЕ, выход которого соединен с первыми входами первого и второго элементов ИЛИ-НЕ. и с инверсным входом второго элемента И, вход

5 /2 управления режимом работы устройства соединен с вторыми входами вторых элементов ИЛИ-НЕ и И, вход PI разрешения переноса устройства соединен с третьим входом второго и с первым входом первого

0 элемента И устройства, вход Vi управления режимом работы устройства соединен с четвертым входом второго элемента И. выход которого соединен с первыми входами первых элементов И-НЕ и с первыми входа5 ми вторых групп входов элементов ЗИ-ИЛИ каждого разряда, входы D.i -D параллельной предустановки устройства соединены соответственно с вторым входом первой группы входов элемента ЗИ-ИЛИ одноимен0 ного разряда, выход первого элемента ИЛИ- НЕ устройства соединен с вторым входом третьей группы входов элемента ЗИ-ИЛИ каждого разряда, выход второго элемента ИЛИ-НЕ устройства соединен с вторым вхо5 дом первого элемента ИЛИ-НЕ и с первыми входами первых групп входов элемента ЗИ- ИЛИ каждого разряда, выход первого элемента И-НЕ каждого разряда соединен с третьим входом третьей группы входов эле0 мента ЗИ-ИЛИ одноименного разряда, выход элемента ЗИ-ИЛИ первого разряда соединен со вторым входом второго элемента И-НЕ одноименного и с первым входом первой группы входов элемента 2И-ИЛИ5 НЕ второго разрядов, выход элемента ЗИ- ИЛИ второго и третьего разрядов соединен с первым входом второй группы входов элемента 2И-ИЛИ-НЕ одноименного и с первым входом первой группы входов элемента 2И-ИЛИ-НЕ последующего разрядов, выход

элсмечкэ ЗИ ИЛИ четвертого разряда сое динен с парным сводом второй группы входов элемента 2И-ИЛИ-НЕ одноименного и с первым входом элемента И-НЕ резервною разрядов, выход второго элемента И-НЕ первого разряда соединен с инверсным D- входом триггера одноименного разряда, выход элемента 2И-ИЛИ-НЕ второго, третьего и четвертого разрядов соединен с инверсным D-входом триггера одноименного раз- ряда, выход элемента И-НЕ резервного разряда соединен с инверсным D-входом триггера одноименного оазрлда, прямой выход триггера первого разряда соединен с первым входом первой группы входов эпе- мента 2И-ИЛИ второго разряда, прямой выход триггера второго, третьего и четвертого разрядов соединен с вторым входом в юрой группы входов элемента 2И-ИЛИ одноименного и с первым входом первой i руппы пхо- дов элемента 2 И-ИЛИ последующего разрядов, прямой выходтриггеоа резервного разряда соединен с вторым входом второй группы входов элемента 2И-ИЛИ одноименного разряда, выход элемента 2И- ИЛИ второго разряда соединен с вторым входом первого элемента И устройства, с инперсным входом второй и с первым вхо- дгм тлетьей групп входов элемента ЗИ-ИЛИ neper го разряда, с вторым входом второй группы входов элемента ЗИ-ИЛИ и с вторым h кодом первого элемента И-НЕ второго, третьего и четвертого разрядов и является первым информационным выходом устрой ства, выход элемента 2И-ИЛИ третьего раз ряда является вторым информационным выходом устройства и соединен с третьем входом первого элемента И устроисгра, с инверсным входом второй и с первым входом третьей групп входов з т мента ЗИ-ИЛИ второго разряда, с третьим входом второй группы входов элемента ЗИ-ИЛИ и с третьим входом первого элемента И-НЕ третьего и четвертого разрядов, выход элемента 2И- ИЛИ четвертого разряда является третьим информационным выходом устройства и соединен с четвертым входом первого элемента И устройства, с инверсным входом второй и с первым входом третьей гоупп входов элемента ЗИ-ИЛИ третьего разряда, с четвертым входом второй группы входов элемента ЗИ-ИЛИ и с четвертым входом первого элемента И-НЕ четвертого разряда, выход элемента 2И-ИЛИ резервного разряда является четвертым информационным выходом устройства и соединен с пятым входом первого элемента И устройства, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ четвертого разряда, отличающийся

тем, что, с целью повышение надежности работы устройства, во второй и ч« вертый разряды дополнительно введем мент И, резервный разряд дополнительно содержит элемент И и два эпемеюа ИЛИ, причем триггер каждого, включа и резерв ный, разряда в своей структуре содержит восемь элементов И-НЕ, пять элементов НЕ, элемент И и триггер-селектор инверсный D-вход триггера каждого разряда соединен с РХОДОМ первого элемента НЕ, выход которого соединен с первь м г/одом первого элемента И-НЕ, с третьим входом четвертой группы входов триггера-селектора и с входом пятого элемента НЕ, выход которого соединен с первым входом третьей группы в/одов триггера-селектора, V-РХОД триггера соединен с вторым входом первого и второ- гг элементов И-НЕ и с вторым входом эле м- нга И, СИНХООВУОД С триггеоа каждого разряда соединен с третьим входом первого и второго элементов И-НЕ и с входом второго элемента НЕ, выход которого соединен с «ходом третьего элемента НЕ, с нторым входом пятого и шестого элементов И-НЕ, с вторым входом первой и с третьим входом второй групп входов триггера сепектора вчход первого элемента И-НЕ соединен с первым входом второго и третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с вторым входом четвертого эпрмента И НГ, выход коюро о соединен с B.opbiN ходом третьего элемента И НЕ с первым иходом шестого элемента И-НЕ, с третьим входом первой и с вторым влодом третьей групп входов триггера-селектора выход третьего элемента И-НЕ соединен с первым входом четвертого и пятого элементов И-НЕ, с четвертым входом второй и с вторым входом четвертой групп входов 1 риггера-селектора, вь лоды пятого и шестого элементов И-НЕ соединены соответст- сенно с первым входом седьмого и с вгсрым F одом восьмого элементов И-HF вход установки в исходное состояние средств фун- «ционалыного контроля триггера соединен с первым входом пятой группы входов тригге- оа-селекгорз, выход третьего эпемента НЕ соединен с первым вводом элемента И вы- од которого соединен с входом четвертого элемента НЕ, с третьим входом третьей, с первым входом четвертой групп входов риг г ера-селектора вход четвертого элемен- г- НЕ соединен с четвертым входом первой м с вторым входом второй групп входов триг- I ера-селектора выход седьмого элемента И-НЕ ягляется прямым выходом триггера и чоединен с первым входом восьмого эле- лента И-l IE и с первым в одом первой груп- чы входов триггера селектора выход

восьмого элемента И-НЕ являе с-: ин версным выходом триггера и соединен с вторым входом седьмого элемента И-НЕ и с первым входом второй группы входов триггера-селектора, выход которого является выходом Отказ триггера каждого разряда и соединен с вторым входом пятой группы входов триггера-селектора, выход Отказ триггера первого разряда соединен с входами элемента ИЛИ/ИЛИ-НЕ одноименного разряда, инверсный выход которого соединен с первым входом второго элемента И-НЕ первого разряда и с вторым входом первой группы входов элемента 2И-ИЛИ второго разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ первого разряда соединен с первым входом второй группы входов элемента 2И-ИЛИ, с вторым входом первой группы входов элемента 2И-ИЛИ- НЕ и с вторыми входами элементов И и ИЛИ/ИЛИ-НЕ второго разряда, выход Отказ триггера второго разряда соединен с первыми входами элементов И и ИЛИ/ИЛИ-НЕ одноименного разряда, выход элемента И второго разряда соединен с первым входом второго элемента ИЛИ резервного разряда, инверсный выход элемента ИЛИ/ИЛИ-НЕ второго разряда соединен с вторым входом второй группы входов элемента 2И-ИЛИ-НЕ одноименного и с вторым входом первой группы входов элемента 2И-ИЛИ третьего разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ второго разряда соединен с первым входом второй группы входов элемента 2И-ИЛИ, с вторым входом первой группы входов элемента 2И- ИЛИ-НЕ, с вторым входом элемента И и с вторым входом элемента ИЛИ/ИЛИ-НЕ третьего разряда, выход Отказ триггера третьего разряда соединен с первым входом элементов И и ИЛИ/ИЛИ-НЕ одноименного разряда, выход элемента И третьего разряда соединен с вторым входом второго элемента ИЛИ резервного разряда, инверсный выход элемента ИЛИ/ИЛИ-НЕ

третьего .,ся сосцинен с вторым входом второй гр1,: ы ехог ,-.5 эпеменга 2И-ИЛИ НЕ одноименного и эгорым входом первой группы входов э..0 .ента 2И-ИЛИ четвертого разрядов, пря, ой выход элемента ИЛИ/ИЛИ-НЕ третьего разряда соединен с первым входом второй группы входов элемента 2И-ИЛИ, с вторым входом первой группы входов элемента 2И-ИЛИ-НЕ и с

вторыми входами элементов И и ИЛИ/ИЛИ- НЕ четвертого разрядов, выход Отказ триггера четвертого разряда соединен с первыми входами эпементов И и ИЛИ/ИЛИ- НЕ одноименного разряда, выход элемента

И четвертого разряда соединен с третьим входом второго элемента ИЛИ резервного разряда, инверсный вход элемента ИЛИ/ИЛИ-НЕ четвертого разряда соединен с вторым входом второй группы входов

элемента 2И-ИЛ И-НЕ одноименного и с вторым входом первой группы входов элемента 2И-ИЛИ резервного разрядов, прямой выход элемента ИЛИ/ИЛИ-НЕ четвертого разряда соединен с первым входом второй

группы входов элемента 2И-ИЛИ, с вторым входом элемента ИЛИ-НЕ, с вторым входом элемента И и с вторым входом первого элемента ИЛИ резервного разряда, выход Отказ триггера резервного разряда соединен с первыми входами элемента И и первого элемента ИЛИ одноименного разряда, вход установки в О средств функционального контроля устройства соединен с соответствующими входами триггеров

каждого, включая и резервный, разряда, выход элемента И резервного разряда соединен с четвертым входом второго элемента ИЛИ одноименного разряда, выход первого элемента И устройства является

выходом Р2 переноса устройства, выход второго элемента ИЛИ резервного разряда является выходом Отказ устройства, выход первого элемента ИЛИ резервного разряда является выходом Частичный отказ двоичного счетчика.

Здесь Тп - момент времени текущего состояния триггера;

Тн+1 - момент времени последующею состояния триггера,

X - безразличное состояние сигнала на соответствующем входе триггера; Н -- неопределенное состояние сигнала на соответствующем выходе, I переход от низкого уровня сигналов к высокому, On, On - предыдущее состояние выхода триггера

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоичный счетчик | 1985 |

|

SU1272503A1 |

Изобретение относится к импульсной технике и может быть использовано в качестве базового элемента в устройствах автоматики и вычислительной техники с повышенными требованиями к достоверности функционирования и эксплуатационной отказоустойчивости. Цель изобретения - повышение надежности двоичного счетчика - достигается за счет введения в его структуру резервного разряда, содержащего триггер 5.5, элемент И-НЕ, 2И-ИЛИ 18.4, элемент И 16.4 и два элемента ИЛИ 19.1 и 19.2, а также элементов ИЛИ/ИЛИ-НЕ 15,1-15,4, И 16.1-16.3, 2И-ИЛИ 18.1-18.3 и элементов 2И-ИЛИ-НЕ 17.1-17.3 с соответствующими связями, достигается автоматическая реконфигурация работоспособной структуры устройства. Кроме того, в триггер каждого разряда введены три элемента НЕ, элемент И и триггер-селектор с соответствующими конструктивными связями, которые представляют собой встроенные средства функционального контроля. В случае отказа одного из основных триггеров 5.1-5.4 на его выходе формируется сигнал Отказ и обеспечивается автоматическая перестройка работоспособной структуры. 3 ил. to С

209

| Справочник | |||

| Применение интегральных микросхем в электронной вычислительной техникеУ Под ред | |||

| Б.Н.Файзулаева и Б.В.Та- рабрина | |||

| М.: Радио и связь, 1987, с.41, рис.3.34 | |||

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-15—Публикация

1988-08-25—Подача