Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники в качестве одного из базовых элементов устройств с повышенной

достоверностью функционирования и функциональной надежностью.

Целью изобретения является повышение достоверности функционирования устройства путем обеспечения постоян

31

ного контроля за правильностью срабатывания разрядов счетчика и повышени быстродействия восстановления работоспособности путем автоматизации этог процесса,

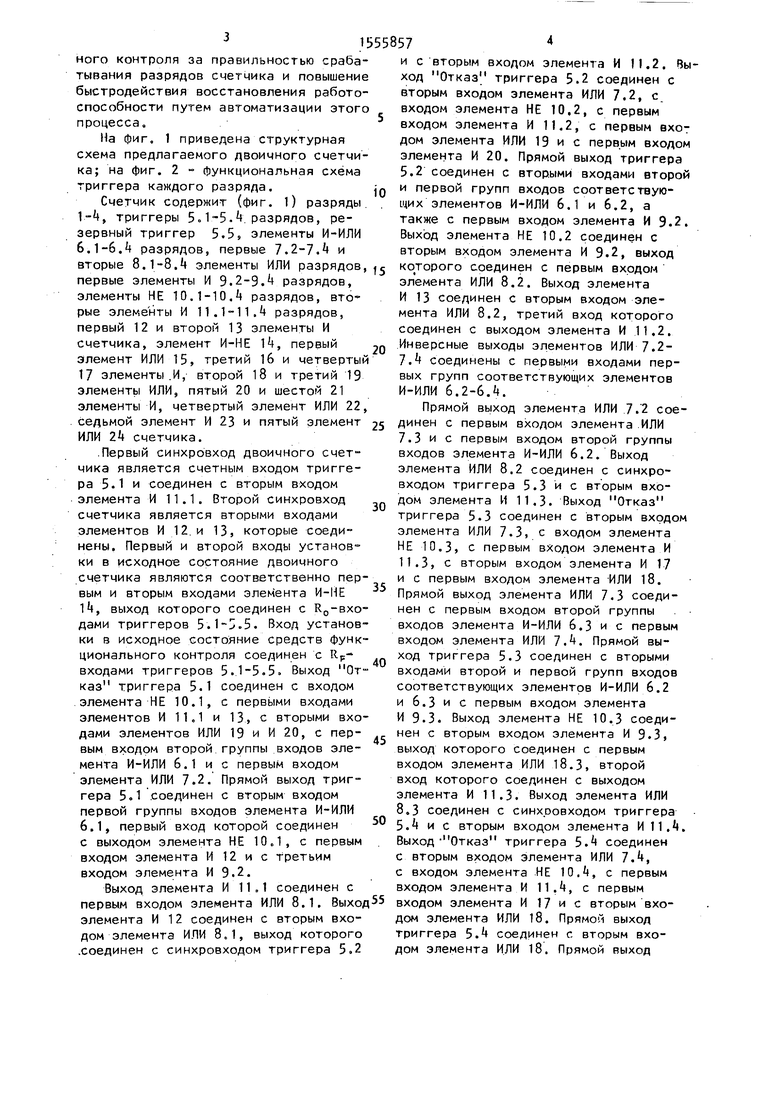

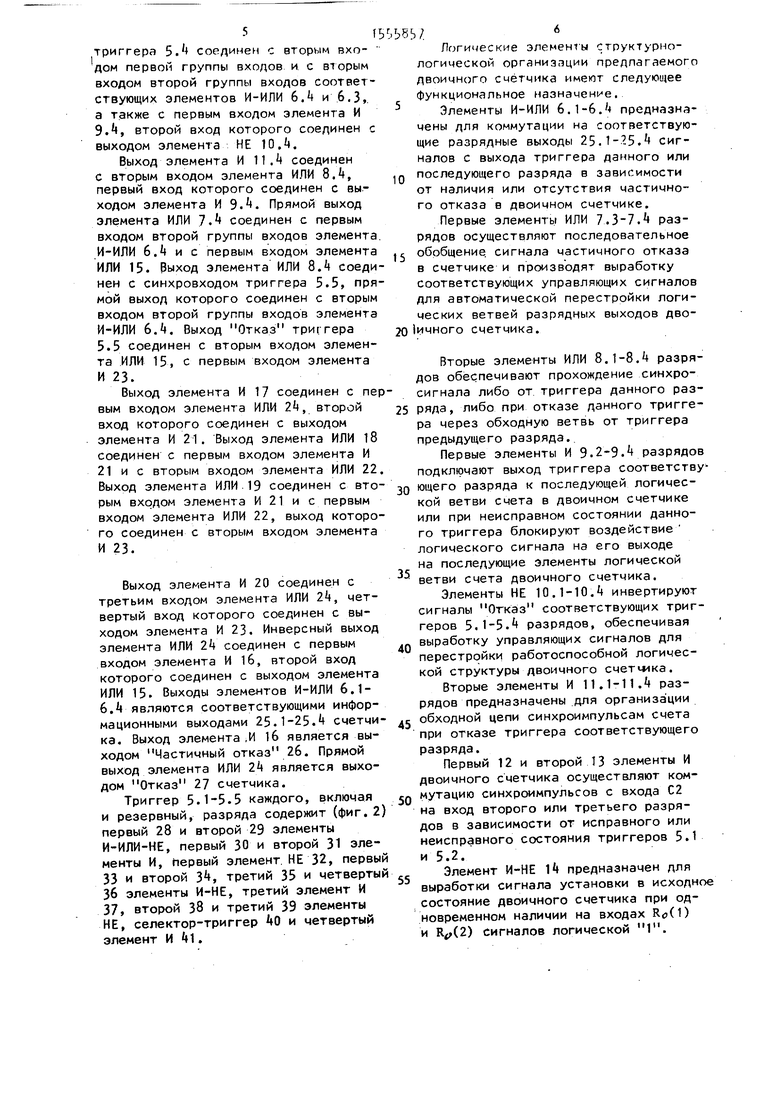

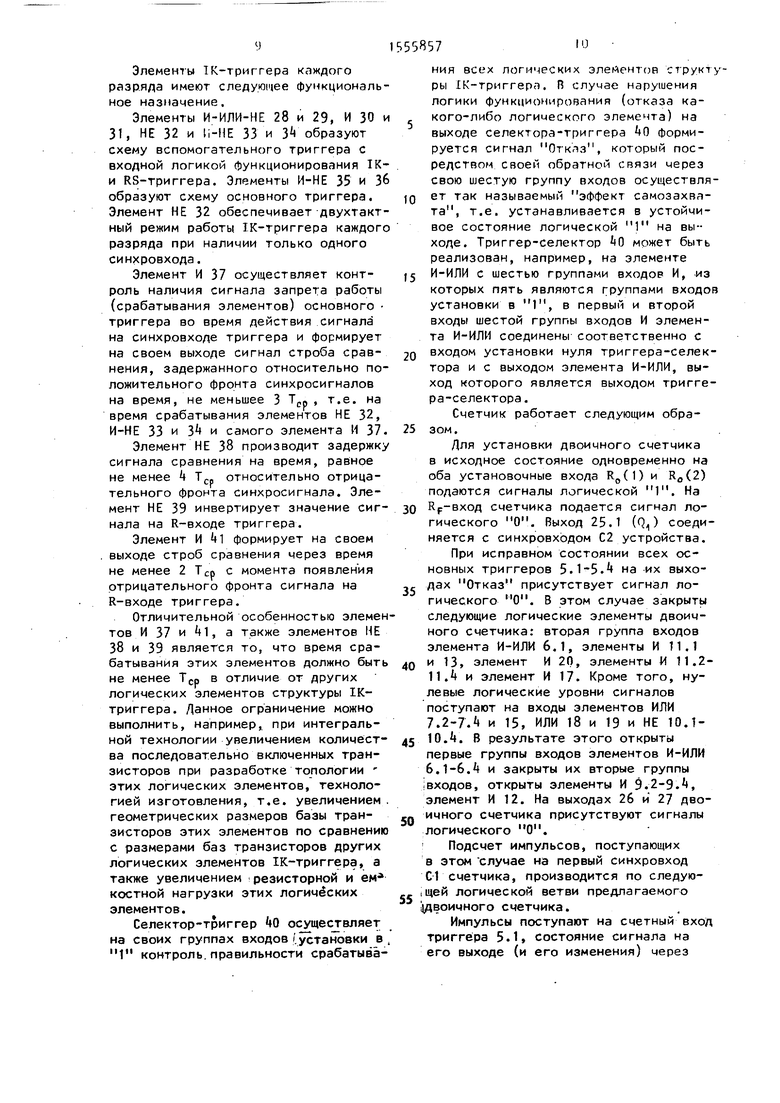

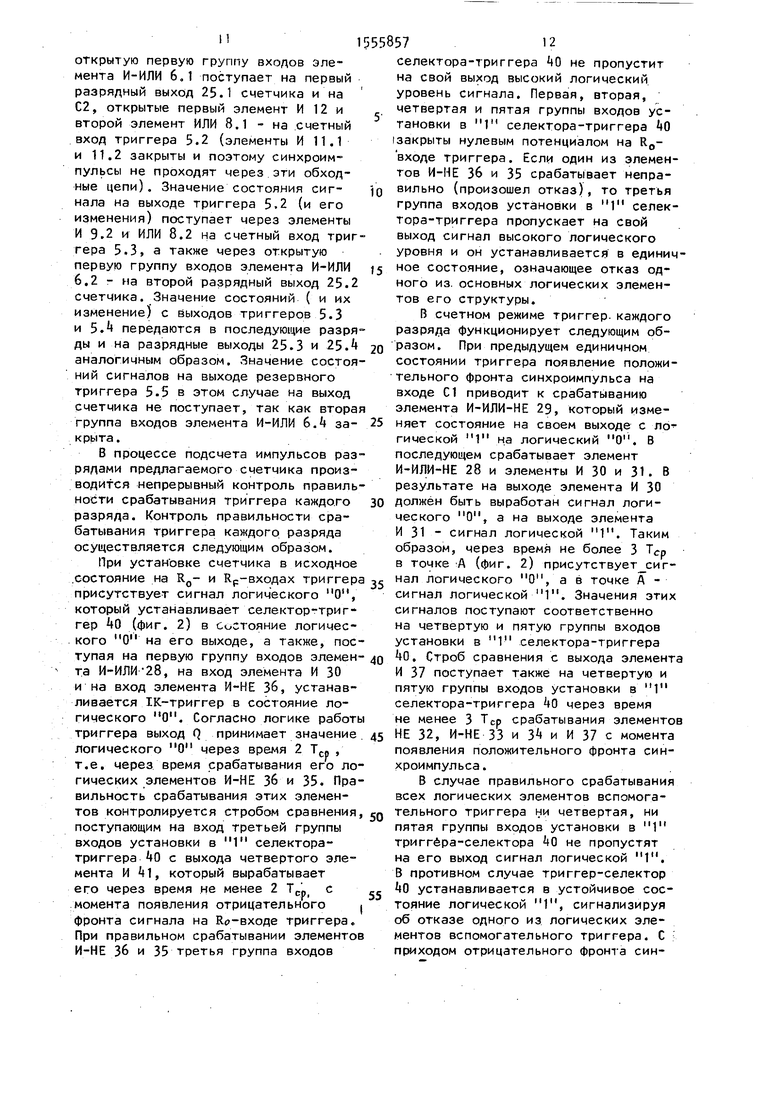

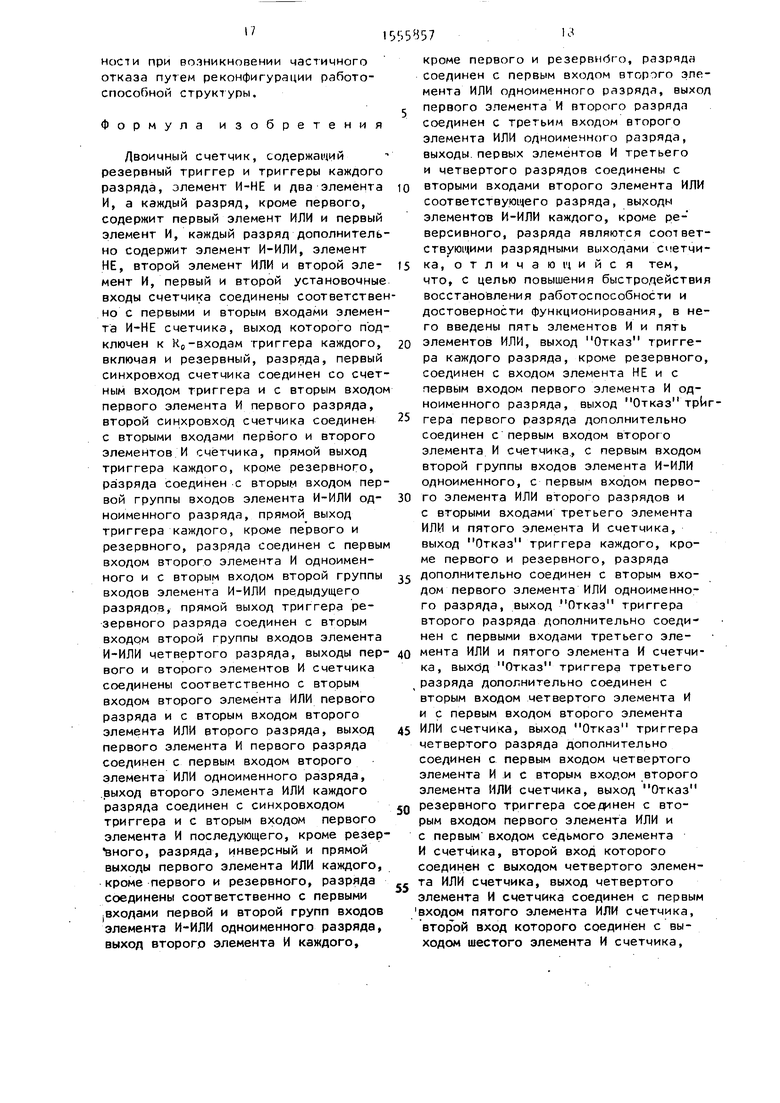

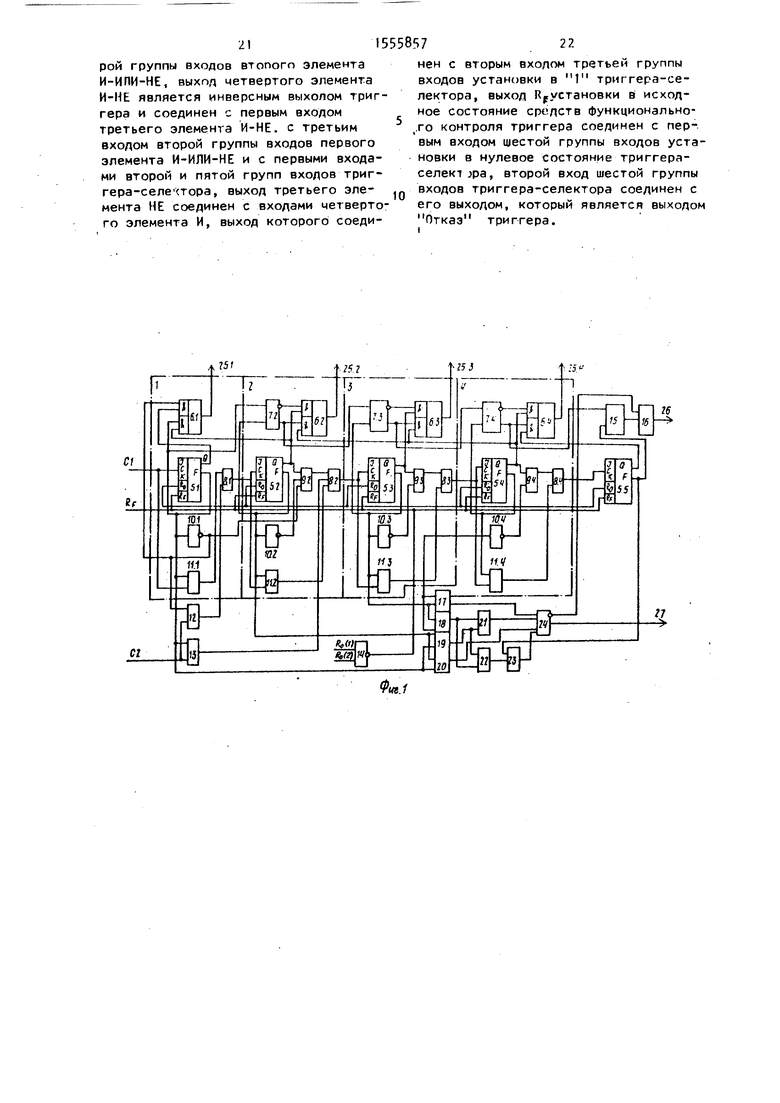

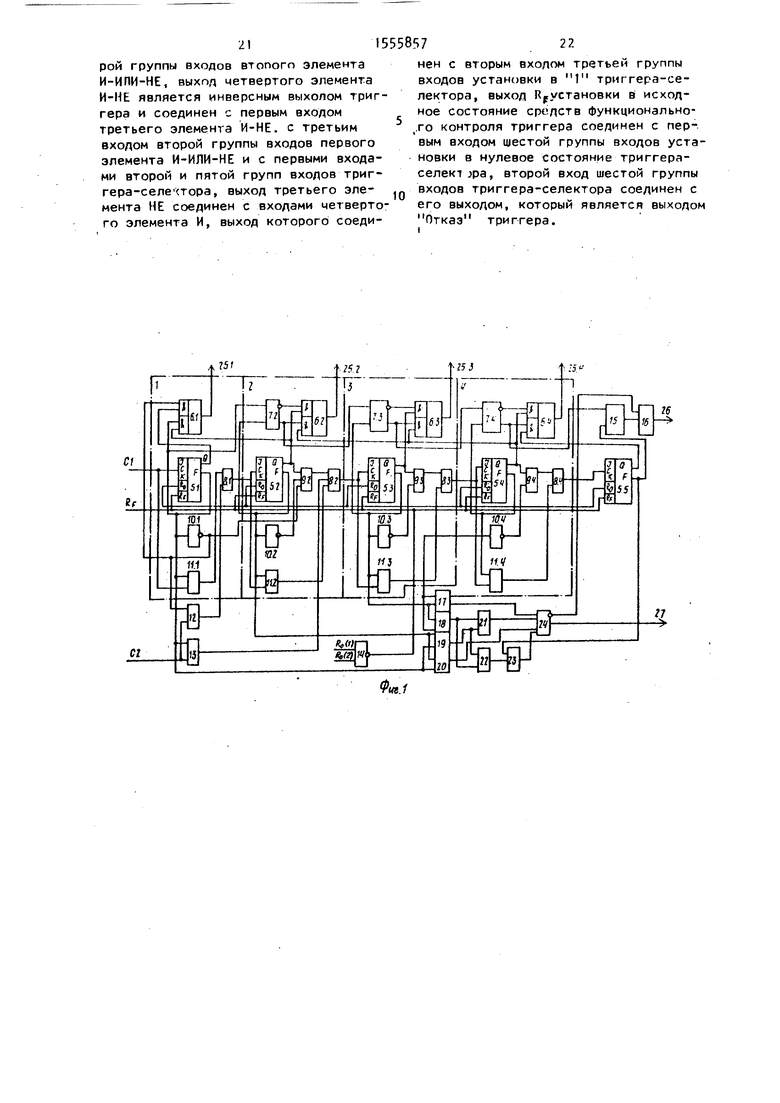

На фиг. 1 приведена структурная схема предлагаемого двоичного счетчика; на фиг. 2 - функциональная схема триггера каждого разряда.

Счетчик содержит (фиг. 1) разряды 1-, триггеры 5.1-5.1 разрядов, резервный триггер 5.5, элементы И-ИЛИ 6.1-6.4 разрядов, первые 7.2-7. и вторые 8.1-8.Ц элементы ИЛИ разрядов первые элементы И 9.2-9.4 разрядов, элементы НЕ 10.1-10,А разрядов, вторые элементы И 11.1-11.1 разрядов, первый 12 и второй 13 элементы И счетчика, элемент И-НЕ 14, первый элемент ИЛИ 15, третий 16 и четверты 17 элементы .И, второй 18 и третий 19 элементы ИЛИ, пятый 20 и шестой 21 элементы И, четвертый элемент ИЛИ 22 седьмой элемент И 23 и пятый элемент ИЛИ 2 счетчика.

Первый синхровход двоичного счетчика является счетным входом триггера 5.1 и соединен с вторым входом элемента И 11.1. Второй синхровход счетчика является вторыми входами элементов И 12 и 13, которые соединены. Первый и второй входы установки в исходное состояние двоичного счетчика являются соответственно первым и вторым входами элемента И-НЕ , выход которого соединен с RO-BXO дами триггеров 5.1-.5. Вход установки в исходное состояние средств функционального контроля соединен с RF- входами триггеров 5.1-5.5. Выход Отказ триггера 5.1 соединен с входом элемента НЕ 10.1, с первыми входами элементов И 11.1 и 13, с вторыми входами элементов ИЛИ 19 и И 20, с первым входом второй группы входов элемента И-ИЛИ 6.1 и с первым входом элемента ИЛИ 7.2. Прямой выход триггера 5.1 соединен с вторым входом первой группы входов элемента И-ИЛИ 6.1, первый вход которой соединен с выходом элемента НЕ 10.1, с первым

входом элемента И 12 и с третьим входом элемента И 9.2. Выход элемента И 11

1 соединен с

первым входом элемента ИЛИ 8.1. Выхо элемента И 12 соединен с вторым входом элемента ИЛИ 8.1, выход которого .соединен с синхровходом триггера 5.2

п 5

вторым ц,

входом элемента И 11.2. Вы0

5

5

0

5 входом элемента

и с

ход Отказ триггера 5.2 соединен с вторым входом элемента ИЛИ 7.2, с входом элемента НЕ 10,2, с первым входом элемента И 11.2, с первым входом элемента ИЛИ 19 и с первым входом элемента И 20. Прямой выход триггера

5.2соединен с вторыми входами второй и первой групп входов соответствующих элементов И-ИЛИ 6.1 и 6.2, а также с первым входом элемента И 9.2. Выход элемента НЕ 10.2 соединен с вторым входом элемента И 9.2, выход которого соединен с первым входом элемента ИЛИ 8.2. Выход элемента

И 13 соединен с вторым входом элемента ИЛИ 8.2, третий вход которого соединен с выходом элемента И 11.2. Инверсные выходы элементов ИЛИ 7.2- 7.4 соединены с первыми входами первых групп соответствующих элементов И-ИЛИ 6.2-6.1.

Прямой выход элемента ИЛИ 7.2 соединен с первым входом элемента ИЛИ

7.3и с первым входом второй группы входов элемента И-ИЛИ 6.2. Выход элемента ИЛИ 8.2 соединен с синхровходом триггера 5.3 и с вторым входом элемента И 11.3. Выход Отказ триггера 5.3 соединен с вторым входом элемента ИЛИ 7.3, с входом элемента НЕ 10.3, с первым входом элемента И 11.3, с вторым входом элемента И 17

и с первым входом элемента ИЛИ 18. Прямой выход элемента ИЛИ 7.3 соединен с первым входом второй группы входов элемента И-ИЛИ 6.3 и с первым входом элемента ИЛИ 7.4. Прямой выход триггера 5.3 соединен с вторыми входами второй и первой групп входов соответствующих элементов И-ИЛИ 6.2 и 6.3 и с первым входом элемента И 9.3. Выход элемента НЕ 10.3 соединен с вторым входом элемента И 9.3, выход которого соединен с первым входом элемента ИЛИ 18.3, второй вход которого соединен с выходом элемента И 11.3. Выход элемента ИЛИ 8.3 соединен с синхровходом триггера 5.1 и с вторым входом элемента И 11.1. Выход Отказ триггера 5.4 соединен с вторым входом элемента ИЛИ 7.1, с входом элемента НЕ 10.1, с первым входом элемента И 11.4, с первым

И 17 и с вторым входом элемента ИЛИ 18. Прямой выход триггера 5.4 соединен с. вторым входом элемента ИЛИ 18. Прямой выход

51

триггера 5,k соединен с вторым входом первой группы входов и с вторым входом второй группы входов соответствующих элементов И-ИЛИ 6.4 и 6.3, а также с первым входом элемента И 9.4, второй вход которого соединен с выходом элемента НЕ 10.4.

Выход элемента И 11.4 соединен с вторым входом элемента ИЛИ 8., первый вход которого соединен с выходом элемента И 9.. Прямой выход элемента ИЛИ 7.4 соединен с первым входом второй группы входов элемента И-ИЛИ 6.4 и с первым входом элемента ИЛИ 15. Выход элемента ИЛИ 8.4 соединен с синхровходом триггера 5.5, прямой выход которого соединен с вторым входом второй группы входов элемента И-ИЛИ 6.. Выход Отказ триггера 5.5 соединен с вторым входом элемента ИЛИ 15, с первым входом элемента И 23.

Выход элемента И 17 соединен с первым входом элемента ИЛИ 2k, второй вход которого соединен с выходом элемента И 21. Выход элемента ИЛИ 18 соединен с первым входом элемента И 21 и с вторым входом элемента ИЛИ 22 Выход элемента ИЛИ 19 соединен с вторым входом элемента И 21 и с первым входом элемента ИЛИ 22, выход которого соединен с вторым входом элемента И 23.

Выход элемента И 20 соединен с третьим входом элемента ИЛИ 2k, четвертый вход которого соединен с выходом элемента И 23. Инверсный выход элемента ИЛИ 2k соединен с первым входом элемента И 16, второй вход которого соединен с выходом элемента ИЛИ 15. Выходы элементов И-ИЛИ 6.1- 6.k являются соответствующими информационными выходами 25.1-25.4 счетчика. Выход элемента ,И 16 является выходом Частичный отказ 26. Прямой выход элемента ИЛИ 2k является выходом Отказ 27 счетчика.

Триггер 5.1-5.5 каждого, включая и резервный, разряда содержит (фиг. 2) первый 28 и второй 29 элементы И-ИЛИ-НЕ, первый 30 и второй 31 элементы И, первый элемент НЕ 32, первый 33 и второй 3k, третий 35 и четвертый 36 элементы И-НЕ, третий элемент И 37, второй 38 и третий 39 элементы НЕ, селектор-триггер 40 и четвертый элемент И k1.

ЬВЬ/6

Логические элементы структурно- логической организации предлагаемого двоичного счетчика имеют следующее функциональное назначение.

Элементы И-ИЛИ 6.1-6. + предназначены для коммутации на соответствующие разрядные выходы 25.1-25. сигналов с выхода триггера данного или

Q последующего разряда в зависимости от наличия или отсутствия частичного отказа в двоичном счетчике.

Первые элементы ИЛИ 7.3-7.4 разрядов осуществляют последовательное

5 обобщение сигнала частичного отказа в счетчике и производят выработку соответствующих управляющих сигналов для автоматической перестройки логических ветвей разрядных выходов дво0 1ичного счетчика.

Вторые элементы ИЛИ 8.1-8.4 разрядов обеспечивают прохождение синхросигнала либо от триггера данного раз5 ряда, либо при отказе данного триггера через обходную ветвь от триггера предыдущего разряда.

Первые элементы И 9.2-9.4 разрядов подключают выход триггера соответству

о ющего разряда к последующей логической ветви счета в двоичном счетчике или при неисправном состоянии данного триггера блокируют воздействие логического сигнала на его выходе на последующие элементы логической ветви счета двоичного счетчика.

Элементы НЕ 10.1-10.4 инвертируют сигналы Отказ соответствующих триггеров 5.1-5.4 разрядов, обеспечивая выработку управляющих сигналов для перестройки работоспособной логической структуры двоичного счетчика.

Вторые элементы И 11.1-11.4 разрядов предназначены для организации

г обходной цепи синхроимпульсам счета при отказе триггера соответствующего разряда.

Первый 12 и второй 13 элементы И двоичного счетчика осуществляют ком0 мУтаЦИ|° синхроимпульсов с входа С2 на вход второго или третьего разрядов в зависимости от исправного или неисправного состояния триггеров 5.1 и 5.2.

Элемент И-НЕ 14 предназначен для выработки сигнала установки в исходное состояние двоичного счетчика при одновременном наличии на входах R(1) и R(2) сигналов логической 1.

5

Первый элемент ИЛИ 15 и третий элемент И 16 двоичного счетчика предназначены для формирования сигнала Частичный отказ, который при своем первоначальном появлении сигнализирует о возникновении отказа и необходимости повторения операции.

Элементы И 17, 20, 21 и 23 ИЛИ 18, 19 22 и 2k являются функциональной группой выработки сигнала Отказ двоичного счетчика при появлении двух и более частичных отказов в его логической структуре, т.е. в случае, когда наличного резерва не хва- тает для покрытия возникших отказов. Сигнал ..Отказ используется обслуживающим персоналом как диагностирующее сообщение о необходимости замены двоичного счетчика без предвари- тельного анализа всей структуры устройства автоматики, вычислительной техники средствами тестирования и диагностики либо как сигнал на проведение реконфигурации работоспособной структуры адаптивного устройства с целью покрытия аппаратного ущерба резервом более высокого уровня.

I-вход триггера каждого разряда (Соединен с третьим входом второй группы входов элемента И-ИЛИ-НЕ 28, К -вхол триггера соединен с вторым входом первой и с первым входом второй группы входов элемента И-ИЛИ-НЕ 28, с входом элемента НЕ 39, с первым входом элемента И 30 и с первым входом элемента И-НЕ 36. Синхровход триггера каждого разряда соединен с четвертым входом второй группы входов элемента И-ИЛИ-НЕ 28, с входом элемента НЕ 32 и с первым входом первой группы входов элемента И-ИЛИ- НЕ 29. К-вход триггера соединен с вторым входом первой группы входов элемента И-ИЛИ-НЕ 29. S-вход тригге- ра соединен с четвертым входом перво и с первым входом второй групп входо элемента .И-ИЛИ-НЕ 29, с третьим входом элемента И 31 и с третьим входом элемента И-НЕ 35.

Выход элемента И-ИЛИ-НЕ 28 соединен с вторым входом элемента И 31 и с вторым входом второй группы входов элемента И-ИЛИ-НЕ 29, выход которого соединен с вторым входом элемента И 30 и с первым входом первой группы входов элемента И-ИЛИ-НЕ 28. Выхо элемента НЕ 32 соединен с вторым входом элемента И-НЕ 33, с первым

o s 0 5

Q

0

5

50

55

входом элемента И-НЕ 3 и с вторыми входами первой и второй групп входов установки 1 селектора-триггера 0. Выход элемента И 30 соединен с первым входом элемента И-НЕ 33 и с третьими входами второй и четвертой групп входов установки в 1 селектора-триггера №. Выход элемента И 31 соединен с вторым входом элемента И-НЕ 3, с третьими входами первой и пятой групп входов установки селектора- триггера 0. Выход элемента И-НЕ 33 соединен с вторым входом элемента И-НЕ 35, с первым входом элемента И 37 и с первым входом элемента И 31.

Выход элемента И-НЕ З соединен с вторым входом элемента И-НЕ 36, с вторым входом элемента И 37 и с третьим входом элемента И 30. Выход элемента И 37 соединен с входом элемента НЕ 38 и с вторыми входами четвертой и пятой групп входов установки в 1 (Селектора-триггера 40. Выход элемента НЕ 38 соединен с четвертыми входами первой и второй групп входов установки 1 селектора-триггера tO. Выход элемента НЕ 39 соединен с первым и вторым входами элемента И 1, выход которого соединен с вторым входом третьей группы входов установки в 1 селектора-триггера АО. Вход RF триггера каждого разряда соединен с первым входом шестой группы входов установки в исходное состояние селектора-триггера 40. Вход R0 триггера дополнительно соединен с пятыми входами первой и второй и с четвертыми входами четвертой и пятой групп входов установки в 1 селектора-триггера 40.

Выход элемента И-НЕ 35 является прямым выходом триггера и соединен с третьим входом элемента И-НЕ 36, с третьим входом первой группы входов элемента И-ИЛИ-НЕ 29 и с первыми входами первой, третьей и четвертой групп входов установки в 1 селектора-триггера 40. Выход элемента И-ИЕ 36 является икверсным выходом триггера и соединен с первым входом элемента И-НЕ 35, с вторым входом второй группы входов элемента И-ИЛИ-НЕ 28 и с первыми входами второй и пятой групп входов установки в 1 селектора-триггера 0, выход которого является выходом Отказ триггера и соединен с вторым входом своей шестой группы входов.

Элементы IK-триггера каждого разряда имеют следукицее функциональное назначение.

Элементы И-ИЛИ-НЕ 28 и 29, И 30 и 31, НЕ 32 и И-НЕ 33 и З1 образуют схему вспомогательного триггера с входной логикой функционирования IK- и RS-триггера. Элементы И-НЕ 35 и 36 образуют схему основного триггера. Элемент НЕ 32 обеспечивает двухтактный режим работы IK-триггера каждого разряда при наличии только одного синхровхода.

Элемент И 37 осуществляет контроль наличия сигнала запрета работы (срабатывания элементов) основного триггера во время действия сигнала на синхровходе триггера и формирует на своем выходе сигнал строба сравнения, задержанного относительно положительного фронта синхросигналов на время, не меньшее 3 Тс. , т.е. на время срабатывания элементов НЕ 32, И-НЕ 33 и 3 и самого элемента И 37.

Элемент НЕ 38 производит задержку сигнала сравнения на время, равное не менее 4 Тср относительно отрицательного фронта синхросигнала. Элемент НЕ 39 инвертирует значение си(- нала на R-входе триггера.

Элемент И 41 формирует на своем выходе строб сравнения через время не менее 2 Тср с момента появления отрицательного фронта сигнала на R-входе триггера.

Отличительной особенностью элементов И 37 и k1, а также элементов НЕ 38 и 39 является то, что время срабатывания этих элементов должно быть не менее ТСр в отличие от других логических элементов структуры IK- триггера. Данное ограничение можно выполнить, например, при интегральной технологии увеличением количества последовательно включенных транзисторов при разработке топологии - этих логических элементов, технологией изготовления, т.е. увеличением . геометрических размеров базы транзисторов этих элементов по сравнению с размерами баз транзисторов других логических элементов IK-триггера, а также увеличением резисторной и ем костной нагрузки этих логических элементов.

Селектор-триггер 0 осуществляет на своих группах входов(установки в, 1 контроль, правильности срабатыва0

5

0

5

0

5

0

5

0

5

ния всех логических элементов структуры IK-триггерп. R случае нарушения логики функционирования (отказа какого-либо логического элемента) на выходе селектора-триггера 40 формируется сигнал Отклз, который посредством своей обратной связи через свою шестую группу входов осуществляет так называемый эффект самозахвата, т.е. устанавливается в устойчивое состояние логической 1 на выходе. Триггер-селектор (О может быть реализован, например, на элементе И-ИЛИ с шестью группами входов И, из которых пять являются группами входов установки в 1, в первый и второй входы шестой группы входов И элемента И-ИЛИ соединены соответственно с входом установки нуля триггера-селектора и с выходом элемента И-ИЛИ, выход которого является выходом триггера-селектора.

Счетчик работает следующим образом.

Для установки двоичного счетчика в исходное состояние одновременно на оба установочные входа R0(O и R0(2) подаются сигналы логической 1. На Rp-вход счетчика подается сигнал логического О. Выход 25.1 (Q,,) соединяется с синхровходом С2 устройства. При исправном состоянии всех основных триггеров 5.1-5. на их выходах Отказ присутствует сигнал логического О. В этом случае закрыты следующие логические элементы двоичного счетчика: вторая группа входов элемента И-ИЛИ 6.1, элементы И 11.1 и 13, элемент И 20, элементы И 11.2- 11.1 и элемент И 17. Кроме того, нулевые логические уровни сигналов поступают на входы элементов ИЛИ 7.2-7.А и 15, ИЛИ 18 и 19 и НЕ 10.1- 10.k. В результате этого открыты первые группы входов элементов И-ИЛИ 6.1-6.А и закрыты их вторые группы входов, открыты элементы И 9.2-9., элемент И 12. На выходах 26 и 27 двоичного счетчика присутствуют сигналы логического О.

Подсчет импульсов, поступающих в этом случае на первый синхровход С1 счетчика, производится по следую- . щей логической ветви предлагаемого двоичного счетчика.

Импульсы поступают на счетный вход триггера 5.1 состояние сигнала на его выходе (и его изменения) через

io

открытую первую группу входов элемента И-ИЛИ 6.1 поступает на первый разрядный выход 25.1 счетчика и на С2, открытые первый элемент И 12 и второй элемент ИЛИ 8.1 - на счетный вход триггера 5.2 (элементы И 11.1 и 11.2 закрыты и поэтому синхроимпульсы не проходят через эти обходные цепи). Значение состояния сигнала на выходе триггера 5.2 (и его изменения) поступает через элементы И 9.2 и ИЛИ 8.2 на счетный вход триг гера 5.3, а также через открытую первую группу входов элемента И-ИЛИ 6.2 - на второй разрядный выход 25.2 счетчика. Значение состояний ( и их изменение) с выходов триггеров 5.3 и 5. передаются в последующие разря ды и на разрядные выходы 25.3 и 25.4 20 аналогичным образом. Значение состояний сигналов на выходе резервного триггера 5.5 в этом случае на выход счетчика не поступает, так как вторая

селектора-триггера 40 не пропустит на свой выход высокий логический уровень сигнала. Первая, вторая, четвертая и пятая группы входов установки в 1 селектора-триггера 40 закрыты нулевым потенциалом на R0- входе триггера. Если один из элементов И-МЕ 36 и 35 срабатывает неправильно (произошел отказ), то третья группа входов установки в 1 селектора-триггера пропускает на свой выход сигнал высокого логического уровня и он устанавливается в единичное состояние, означающее отказ одного из основных логических элементов его структуры.

В счетном режиме триггер каждого разряда функционирует следующим образом. При предыдущем единичном состоянии триггера появление положительного фронта синхроимпульса на входе С1 приводит к срабатыванию элемента И-ИЛИ-НЕ 29, который изме15

группа входов элемента И-ИЛИ 6.4 за- 25 няет состояние на своем выходе с локрыта.

В процессе подсчета импульсов разрядами предлагаемого счетчика производится непрерывный контроль правильности срабатывания триггера каждого разряда. Контроль правильности срабатывания триггера каждого разряда осуществляется следующим образом.

При установке счетчика в исходное

гической 1 на логический О. В последующем срабатывает элемент И-ИЛИ-НЕ 28 и элементы И 30 и 31. В результате на выходе элемента И 30 30 должен быть выработан сигнал логического О, а на выходе элемента И 31 - сигнал логической 1. Таким образом, через время не более 3 Тер в точке А (фиг. 2) присутствует CHI-

состояние на R0- и КР-входах триггера нал логического О, а в точке А II.. J Ju 1 1 . i л

присутствует сигнал логического О1 который устанавливает селектор-триггер 40 (фиг. 2) в Состояние логического О на его выходе, а также, поссигнал логической 1

Значения этих сигналов поступают соответственно на четвертую и пятую группы входов установки в 1 селектора-триггера

тупая на первую группу входов элемен- 40 0« Строб сравнения с выхода элемента

та И-ИЛИ 28, на вход элемента И 30 и на вход элемента И-НЕ 36, устанавливается IK-триггер в состояние логического О. Согласно логике работы триггера выход Q принимает значение Д5 логического О через время 2 Тс. , т.е. через время срабатывания его логических элементов И-НЕ 36 и 35. Правильность срабатывания этих элеменИ 37 поступает также на четвертую и пятую группы входов установки в 1 селектора-триггера 40 через время не менее 3 Тср срабатывания элементов НЕ 32, И-НЕ 33 и 34 и И 37 с момента появления положительного фронта синхроимпульса .

В случае правильного срабатывания всех логических элементов вспомогаio

20

55585712

селектора-триггера 40 не пропустит на свой выход высокий логический уровень сигнала. Первая, вторая, четвертая и пятая группы входов установки в 1 селектора-триггера 40 закрыты нулевым потенциалом на R0- входе триггера. Если один из элементов И-МЕ 36 и 35 срабатывает неправильно (произошел отказ), то третья группа входов установки в 1 селектора-триггера пропускает на свой выход сигнал высокого логического уровня и он устанавливается в единичное состояние, означающее отказ одного из основных логических элементов его структуры.

В счетном режиме триггер каждого разряда функционирует следующим образом. При предыдущем единичном состоянии триггера появление положительного фронта синхроимпульса на входе С1 приводит к срабатыванию элемента И-ИЛИ-НЕ 29, который изме15

гической 1 на логический О. В последующем срабатывает элемент И-ИЛИ-НЕ 28 и элементы И 30 и 31. В результате на выходе элемента И 30 должен быть выработан сигнал логического О, а на выходе элемента И 31 - сигнал логической 1. Таким образом, через время не более 3 Тер в точке А (фиг. 2) присутствует CHI-

нал логического О, а в точке А u 1 1 . i л

сигнал логической 1

Значения этих сигналов поступают соответственно на четвертую и пятую группы входов установки в 1 селектора-триггера

И 37 поступает также на четвертую и пятую группы входов установки в 1 селектора-триггера 40 через время не менее 3 Тср срабатывания элементов НЕ 32, И-НЕ 33 и 34 и И 37 с момента появления положительного фронта синхроимпульса .

В случае правильного срабатывания всех логических элементов вспомога

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоичный счетчик | 1985 |

|

SU1272503A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1688405A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

Двоичный счетчик может быть использован в автоматике и вычислительной технике в качестве базового элемента в устройствах с повышенными достоверностью функционирования и эксплуатационной отказоустойчивостью. Цель изобретения - повышение достоверности функционирования счетчика путем обеспечения постоянного контроля за правильностью срабатывания его разрядов и повышение быстродействия восстановления работоспособности путем автоматизации этого процесса. Двоичный счетчик за счет введения в его структурно-логическую организацию пяти элементов И и пяти элементов ИЛИ с соответствующими конструктивными связями формирует на своих выходах сигналы "Частичный отказ" и "Отказ", сигнализируя о достоверности своего функционирования. Триггер каждого разряда имеет средства встроенного функционального контроля, обеспечивающие непрерывный контроль за правильностью их срабатывания. В случае отказа одного из основных элементов триггера на его выходе формируется сигнал "Отказ", который является управляющим сигналом для реконфигурации работоспособной структуры предлагаемого двоичного счетчика. Реконфигурация обеспечивает замену отказавшего триггера на резервный триггер. Счетчик содержит четыре разряда, четыре триггера разрядов, резервный триггер, четыре элемента И-ИЛИ, двенадцать элементов ИЛИ, четырнадцать элементов И, четыре элемента НЕ. Триггер каждого разряда содержит два элемента И-ИЛИ-НЕ, четыре элемента И-НЕ, три элемента НЕ, четыре элемента И, а также триггер-селектор. В счетчике проводится автоматическое восстановление его работоспособности путем реконфигурации работоспособной структуры, что повышает быстродействие процесса восстановления работоспособности. 2 ил.

тов контролируется стробом сравнения, JQ тельного триггера ни четвертая,

пятая группы входов установки в триггера-селектора 40 не пропус на его выход сигнал логической В противном случае триггер-селе ДО устанавливается в устойчивое тояние логической 1, сигнализ об отказе одного из логических ментов вспомогательного триггер приходом отрицательного фронта

поступающим на вход третьей группы входов установки в 1 селектора- триггера 40 с выхода четвертого элемента И 41, который вырабатывает его через время не менее 2 ,.„ с момента появления отрицательного j фронта сигнала на Ro-входе триггера. При правильном срабатывании элементов И-НЕ 36 и 35 третья группа входов

ни

тельного триггера ни четвертая,

пятая группы входов установки в 1 триггера-селектора 40 не пропустят на его выход сигнал логической 1. В противном случае триггер-селектор ДО устанавливается в устойчивое состояние логической 1, сигнализируя об отказе одного из логических элементов вспомогательного триггера. С приходом отрицательного фронта син131555857

роимпульса на С-вход триггера чеез время 2 ТСр на выходах элементов -НЕ 33 и 3 появляются следующие игналы: на выходе элемента И-НЕ 33 соос за го чи ло ря на ты ты на ны О ро си в хв зо от эт ти но го от

сигнал логической 1, а на выходе элемента И-НЕ 3 - сигнал логического О. В результате этого через время 3 ТСр элемент И 37 закрывается и на его выходе устанавливается сигнал логического О. Через время Т, с момента появления отрицательного фронта синхроимпульса на выходе элемента НЕ 38 появляется сигнал строба сравнения, который поступает на первую и вторую группы входов установки в 1 селектора-триггера АО, который сравнивает на этих группах входов состояния сигналов на выходах элементов И 30 ч И-НЕ 36, а также на выходах элементов И 31 и И-НЕ 35 соответ- ственно. При правильном срабатывании всех логических элементов структуры триггера состояния сигналов на указанных выходах противоположные и, следовательно, ни первая, ни вторая группы входов установки в 1 триггера-селектора 0 не пропускают на его выход сигнал высокого логического уровня. В противном случае триггер- селектор АО устанавливается в состояние логической 1, сигнализируя об отказе одного или нескольких логических элементов основного триггера. Функционирование триггера и контроль правильности срабатывания логических элементов структуры IK-триггера каждого разряда при предыдущем его нулевом состоянии производятся аналогичным образом.

Общий вид условий формирования сигнала Отказ IK-триггера каждого разряда можно представить следующим .аналитическим выражением:

-5AQRS V CAQRS V RQ V CAQRS V CAQRS, де F С,

45

- функционал отказа IK- триггера каждого разряда; С - соответственно единичное 50 или нулевое состояние сигнала на С-входе IK- триггера каждого разряда; А, А - единичное и нулевое значения сигнала соответственно в точке А или точ- ке А триггера;

ll - нулевое значение сигнала на R-входе триггера;

55

14

0

5

0

5

0

5

0

5

0

5

Q, Q значение сигнала на прямом и инверсном выходах триггера.

В процессе подсчета синхроимпульсов средствами встроенного контроля осуществляется постоянный контроль за правильностью срабатывания каждого триггера структуры двоичного счетчика. В случае отказа какого-либо логического элемента триггера разряда на его выходе F появляется CHI- нал логической 1. При этом элементы ИЛИ 15, 18, 19, 22 и 2А и элементы И 16, 17, 20, 21 и 23 формируют на выходе 26 счетчика сигнал Частичный отказ или на выходе 27 - сигнал Отказ. При числе отказавших триггеров формируется сигнал Отказ, т.е. сигнал о том, что наличного резерва в структуре двоичного счетчика не хватает для покрытия возникших отказов и счетчик подлежит замене. При отказе какого-либо одного триггера этот отказ покрывается путем автоматической реконфигурации работоспособной структуры предлагаемого двоичного счетчика по принципу вытеснения отказавшего триггера.

Рассмотрим работу предлагаемого двоичного счетчика при отказе триггера второго разряда. На выходе F гера 5.2 появляется сигнал логической 1. Этот сигнал поступает на следующие логические элементы двоичного счетчика: ИЛИ 7.2, НЕ 10.2, И 11.2, ИЛИ 19 и И 20. В резульате этого производится смена состояний сигналов на выходах элементов ИЛИ 7.2-7., НЕ 10.2 ИЛИ 19 и ИЛИ 15, а элементы 11.3 16 и 20 открываются высокими логическими уровнями сигналов. Кроме того, вследствие изменения сигналов на выходах элементов ИЛИ 7.2-7. закрываются первые группы входов и открываются вторые группы входов элементов И-ИЛИ 6.2-6.А, Единичное состояние сигнала с выхода элемента ИЛИ 19 поступает на вход элемента ,И 21 и через элемент ИЛИ 22 -. на вход элемента И 23. Однако элемент И 21 закрыт нулевым уровнем сигнала с выхода элемента ИЛИ 18, а элемент И 23 - нулевым уровнем сигнала с выхода Отказ триггера 5.5.

Таким образом, на всех входах элемента ИЛИ 2k присутствуют сигналы логического О и на выходе 27 уст

15

ройства сигнал Отказ отсутствует. Одновременно с этим на выходе элемента И 16 вырабатывается высокий логический уровень сигнала (на его второй вход поступает высокий логический уровень сигнзла с инверсного выхода элемента ИЛИ 2), что приводит к появлению сигнала Частный отказ на выходе 26 двоичного счетчика. Сигнал Частный отказ двоичного счетчика означает при своем первом появлении, что операцию для ее достоверного выполнения необходимо повторить. За время, необходимое для повторного запус- ка этой команды (операции), предлагаемый двоичный счетчик производит автоматическое восстановление работоспособности путем вытеснения отказавшего триггера 5.2 триггером 5.3, триггера 5.3 триггером 5.4 и триггера 5.4 триггером 5.5.

Автоматическое восстановление работоспособности предлагаемого двоичного счетчика производится следующим образом. Так как открываются вторые группы входов элементов И-ИЛИ 6.2- 6.4, то на разрядные выходы устройства 25.2-25.4 в этом случае поступают значения состояний на выходах тригге- ров 5.3-5.5 последующих разрядов, т.е. на вход 25.2 поступает значение сигнала на выходе триггера 5.3, на выход 25.3 с триггера 5. и на выход 25.4 - с триггера 5.5. Элемент И 9.2 закрывается нулевым уровнем сигнала с выхода элемента НЕ 10.2, предотвращая тем самым влияние логического сигнала с выхода неисправного триггера 5.2 на последующие логические элементы структуры двоичного счетчика. Элемент И 11.2 открывается, организуя обходную цепь для синхроимпульсов счета, поступающих С выхода первого разряда на третий разряд, обходя при этом неисправный триггер 5.2 второго разряда.

Подсчет импульсов в этом случае производится по следующей логической ветви двоичного счетчика: с входа С1 на счетный4 вход триггера 5.1, с выхода триггера 5.1 - на выход 25.1 счетчика через открытую первую группу входов элемента И-ИЛИ 6.1, с выхода 25.1 через соединение 25.1 С2,

открытые, элемент И 12 и элемент ИЛИ 8.1, элемент И 11.2 и элемент ИЛИ 8.2 - на счетный вход триггера 5.3, значение состояния сигнала с выхода

1

10

20

25

15

30

555857|0

триггера 5.3 (и его изменение) поступает через элементы И 9.3 и ИЛИ 8.3 на счетный вход триггера 5.4, а также через открытую вторую группу входов элементе И-ИЛИ 6.2 на разрядный выход 25.2, значение состояний (и их изменения) сигналов с выходов триггеров 5.4 и 5.5 на разрядные выходы 25.3 и 25.4 производится аналогичным образом. Значение состояния сигнала на выходе триггера 5Л через элементы И 9. и ИЛИ 8.4 передается на счетный вход триггера 5.5.

При отказе триггера 5.1 автоматическое восстановление работоспособности двоичного счетчика производится путем замещения триггера 5.1 триггером 5.2, триггера 5.2 триггером 5.3, триггера 5.3 триггером 5. и триггера 5.4 триггером 5.5, т.е. производится полная сдвижка триггеров 5.2-5.5 влево относительно разрядных выходов внутри логической структуры предлагаемого двоичного счетчика. Автоматическая реконфигурация работоспособной структуры двоичного счетчика производится таким же образом, что и при отказе триггера 5.2.

В случае отказа двух и более триггеров 5.1-5.5 на выходе 27 предлагаемого двоичного счетчика формируется сигнал Отказ. Это производится следующим образом. Когда отказывают триггеры 5.1 и 5.3, то единичные логические уровни сигналов с выходов F соответствующих триггеров 5.1 и 5.3 (фиг. 1) поступают через элементы ИЛИ 18 и 19 соответственно на оба входа элемента И 21, который формирует на своем выходе также высокий логический уровень сигнала. Следовательно, сигнал с выхода элемента И 21 поступает на вход элемента ИЛИ 24, который также формирует на своем выходе высокий логический уровень CHI- нала. Высокий логический уровень сигнала с прямого выхода элемента ИЛИ 24 поступает на выход 27 счетчика, что означает Отказ устройства в целом, т.е. наличного резерва в предлагаемом счетчике не хватает для покрытия возникших отказов.

Таким образом, обеспечивается повышенная достоверность функционирования за счет непрерывного контроля правильности срабатывания триггеров каждого разряда, а также обеспечивается восстановление работоспособ35

40

45

50

55

ности при возникновении частичного отказа путем реконфигурации работоспособной структуры.

Формула изобретения

Двоичный счетчик, содержащий резервный триггер и триггеры каждого разряда, элемент М-НЕ и два элемента И, а каждый разряд, кроме первого, содержит первый элемент ИЛИ и первый элемент И, каждый разряд дополнительно содержит элемент И-ИЛИ, элемент НЕ, второй элемент ИЛИ и второй элемент И, первый и второй установочные входы счетчика соединены соответствен но с первыми и вторым входами элемента И-НЕ счетчика, выход которого подключен к К0-входам триггера каждого, включая и резервный, разряда, первый синхровход счетчика соединен со счетным входом триггера и с вторым входом первого элемента И первого разряда, второй синхровход счетчика соединен с вторыми входами первого и второго элементов И счетчика, прямой выход триггера каждого, кроме резервного, разряда соединен с вторым входом первой группы входов элемента И-ИЛИ одноименного разряда, прямой выход триггера каждого, кроме первого и резервного, разряда соединен с первым входом второго элемента И одноименного и с вторым входом второй группы входов элемента И-ИЛИ предыдущего разрядов, прямой выход триггера резервного разряда соединен с вторым входом второй группы входов элемента И-ИЛИ четвертого разряда, выходы первого и второго элементов И счетчика соединены соответственно с вторым входом второго элемента ИЛИ первого разряда и с вторым входом второго элемента ИЛИ второго разряда, выход первого элемента И первого разряда соединен с первым входом второго элемента ИЛИ одноименного разряда, выход второго элемента ИЛИ каждого разряда соединен с синхровходом триггера и с вторым входом первого элемента И последующего, кроме резервного, разряда, инверсный и прямой выходы первого элемента ИЛИ каждого, кроме первого и резервного, разряда соединены соответственно с первыми уходами первой и второй групп входов элемента И-ИЛИ одноименного разряда, выход второго элемента И каждого,

кроме первого и резервного, разряда соединен с первым входом второго элемента ИЛИ одноименного разряда, выход г первого элемента И второго разряда соединен с третьим входом второго элемента ИЛИ одноименного разряда, выходы первых элементов И третьего и четвертого разрядов соединены с вторыми входами второго элемента ИЛИ соответствующего разряда, выходы элементов И-ИЛИ каждого, кроме реверсивного, разряда являются соответ- ствукицими разрядными выходами с етчи- 5 ка, отличающийся тем,

что, с целью повышения быстродействия восстановления работоспособности и достоверности функционирования, в него введены пять элементов И и пять о элементов ИЛИ, выход Отказ триггера каждого разряда, кроме резервного, соединен с входом элемента НЕ и с первым входом первого элемента И одноименного разряда, выход Отказ триг- 5 гера первого разряда дополнительно соединен с первым входом второго элемента И счетчика, с первым входом второй группы входов элемента И-ИЛИ одноименного, с первым входом перво- 0 го элемента ИЛИ второго разрядов и с вторыми входами третьего элемента ИЛИ и пятого элемента И счетчика, выход Отказ триггера каждого, кроме первого и резервного, разряда 5 дополнительно соединен с вторым входом первого элемента ИЛИ одноименного разряда, выход Отказ триггера второго разряда дополнительно соединен с первыми входами третьего эле- 0 мента ИЛИ и пятого элемента И счетчика, выход Отказ триггера третьего разряда дополнительно соединен с вторым входом четвертого элемента И и с первым входом второго элемента 5 ИЛИ счетчика, выход Отказ триггера четвертого разряда дополнительно соединен с первым входом четвертого элемента И и с вторым входом второго элемента ИЛИ счетчика, выход Отказ Q резервного триггера соединен с вторым входом первого элемента ИЛИ и с первым входом седьмого элемента И счетчика, второй вход которого соединен с выходом четвертого элемен- та ИЛИ счетчика, выход четвертого элемента И счетчика соединен с первым входом пятого элемента ИЛИ счетчика, второй вход которого соединен с выходом шестого элемента И счетчика,

выхол пятого элемента И соединен с третьим входом пятого элемента ИЛИ счетчика, четвертый вход которого соединен с выходом седьмого элемента И счетчика, выход второго элемента ИЛИ соединен с первым входом шестого элемента И и с вторым входом четвертого элемента ИЛИ счетчик, выход третьего элемента ИЛИ счетчика соединен с вторым входом шестого элемента И и с первым входом четвертого элемента ИЛИ счетчика, выход элемента НЕ первого разряда соединен с первым входом первого элемента И счетчика, с первым входом первой группы входов элемента И-ИЛИ одноименного разряда и с третьим входом второго элемента И второго разряда, выход элемента НЕ каждого, кроме первого и резервного, разряда соединен с вторым входом второго элемента И одноименного разряда, прямой выход первого элемента ИЛИ каждого, кроме первого и четвертого, разряда соединен с первым входом первого элемента ИЛИ последующего разряда, выход первого элемента ИЛИ четвертого разряда соединен с первым входом первого элемента ИЛИ счетчика, вход установки в исходное состояние средств функционального контроля соединен с Rp-входом триггера каждого, включая и резервный, разряда, выход первого элемента ИЛИ счетчика соединен с вторым входом третьего элемента И счетчика, первый вход которого соединен с инверсным выходом пятого элемента ИЛИ счетчика, прямой выход которого является выходом Отказ счетчика, выход третьего элемента И является выходом Частичный отказ счетчика, а каждый триггер содержит два элемента И-ИЛИ-НЕ, четыре элемента И-НЕ, четыре элемента И, три элемента НЕ и триггер-селектор, причем I-вход триггера соединен с третьим входом второй группы входов первого элемента И-ИЛИ-НЕ, синхровход триггера соединен с четвертым входом второй группы входов первого, с первым входом первой группы входов второ- го элементов И-ИЛИ-НЕ и с входом первого элемента НЕ, выход которого соединен с вторым входом первого и с первым входом второго элементов И-НЕ, а также с вторыми входами первой и второй групп входов установки в J триггера-селектора, Кгвход триггера соединен с вторым входом первой и с

первым входом второй групп входов первого элемента И-ИЛИ-НЕ, с входом третьего элемента НЕ, с первым входом

первого элемента И, с первым входом четвертого элемента И-НЕ и с пятыми входами первой и второй, с четвертыми (входами четвертой и пятой групп входов установки в 1 триггера-селектоРа, К-вход триггера соединен с вторым входом первой группы входов второго элемента И-ИЛИ-НЕ, S-вход триггера соединен с четвертым входом первой группы входов и с первым входом вто5 рой группы входов второго элемента И-ИЛИ-НЕ, а также с третьим входом второго элемента И и с третьим входом третьего элемента И-НЕ, выход первого элемента И-ИЛИ-НЕ соединен с втоQ рым входом второго элемента И и с вторым входом второй группы входов второго элемента И-ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента И и с первым входом

5 первой группы входов первого элемента И-ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента И-НЕ, с третьим входом четвертой и с третьим входом второй групп

о входов установки в 1 триггера-селектора, выход второго элемента И соединен с вторым входом второго элемента И-НЕ, с третьим входом первой группы входов и с третьим входом пятой группы входов установки в 1 триггера-селектора, выход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, с перёым входом третьего элемента И и с перп вым входом второго элемента И, выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, с вторым входом третьего элемента И и с третьим входом первого элемента

с И, выход третьего элемента И соединен с входом второго элемент НЕ, с вторым входом четвертой группы входов и с вторым входом пятой группы входов установки в 1 триггера-селектора, выход второго элемента НЕ соелинен с четвертыми входами первой и второй групп -входов установки в 1 триггера-селектора, выход третьего элемента И-НЕ является прямым выходом триг- геоа и соединен с третьим входом чет- верто го элемента И-НЕ, с первыми входами первой, третьей и четвертой групп входов установки в 1 триггера-селектора и с третьим входом вто0

рой группы входов ВТОРОГО элемента И-ИПИ-НЕ, выход четвертого элемента И-НЕ является инверсным выхолом триггера и соединен с первым входом третьего элемента И-НЕ. с третьим входом второй группы входов первого элемента И-ИЛИ-НЕ и с первыми входами второй и пятой групп входов триг- гера-селечтора, выход третьего эле- мента НЕ соединен с входами четвертого элемента И, выход которого соеди 5Г

нен с вторым входом третьей группы входов установки в 1 триггера-селектора, выход установки в исходное состояние средств функционально- (.го контроля триггера соединен с первым входом шестой группы входов установки в нулевое состояние триггера- селект jpa, второй вход шестой группы входов триггера-селектора соединен с его выходом, который является выходом Отказ триггера.

Ко

Q&ll

| Справочник по интегральным микросхемам | |||

| / Под ред | |||

| Б.В | |||

| Тарабрина | |||

| М | |||

| : Энергия, 1980, с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

| Двоичный счетчик | 1985 |

|

SU1272503A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-07—Публикация

1988-06-27—Подача