1

Изобретение относится к запоминающим устройствам и может быть использовано в качестве буферного запоминающего устройства в системах сбора, регистрации и обработки многоканаль- ной измерительной информации.

Цель изобретения - повьшение надежности устройства и расширение области его применения путем обеспечения избирательной записи данных в на копитель.

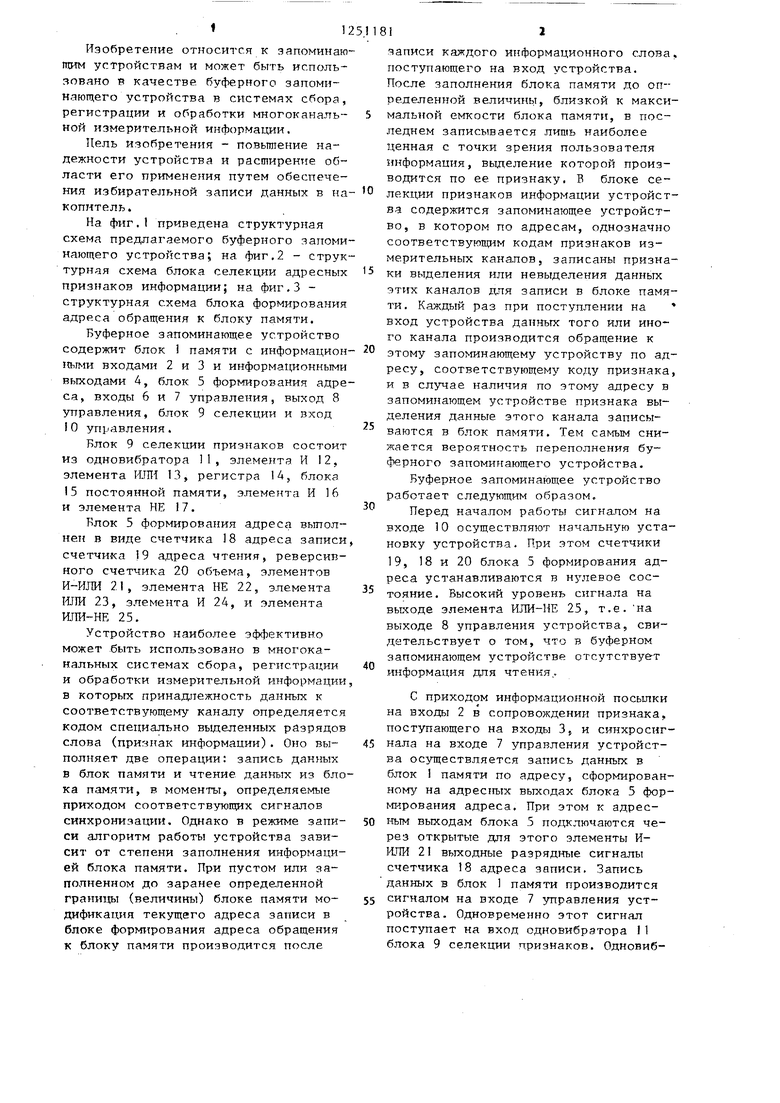

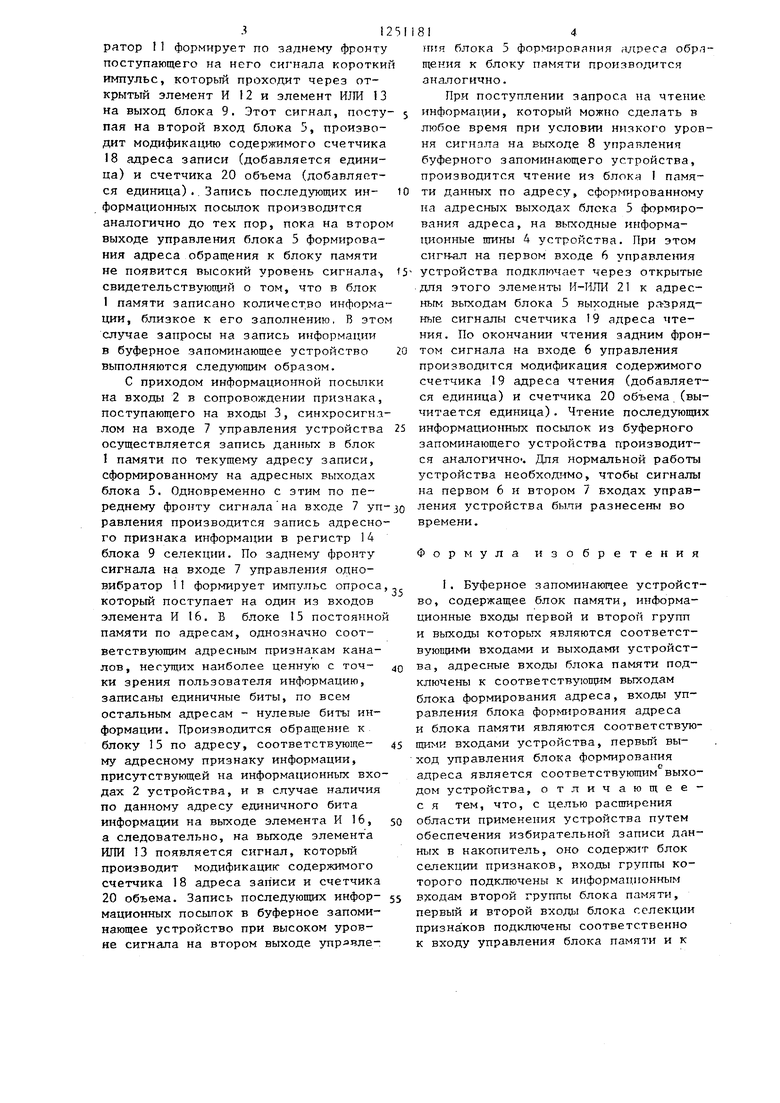

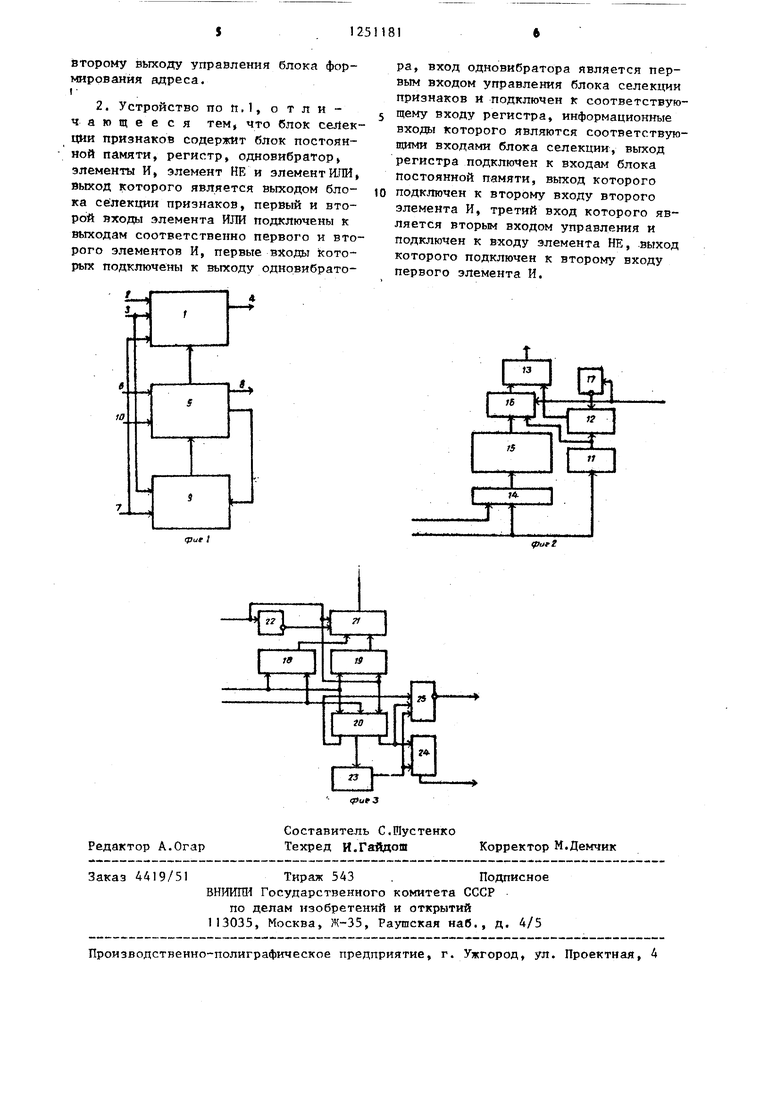

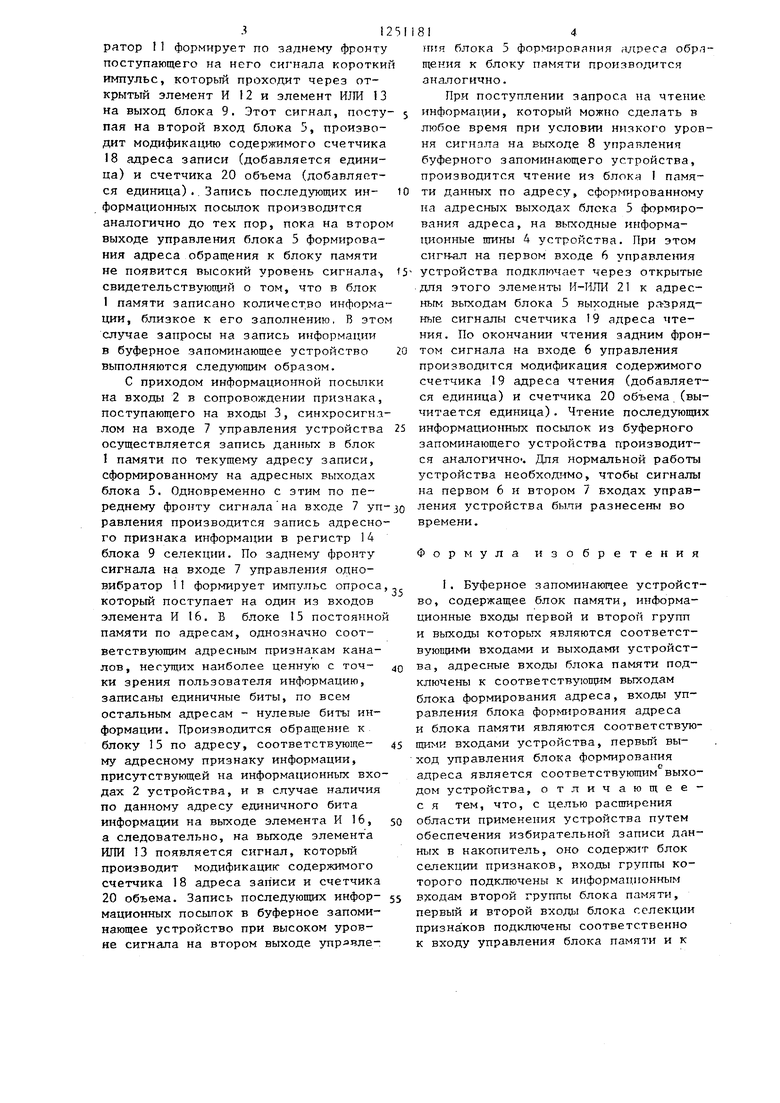

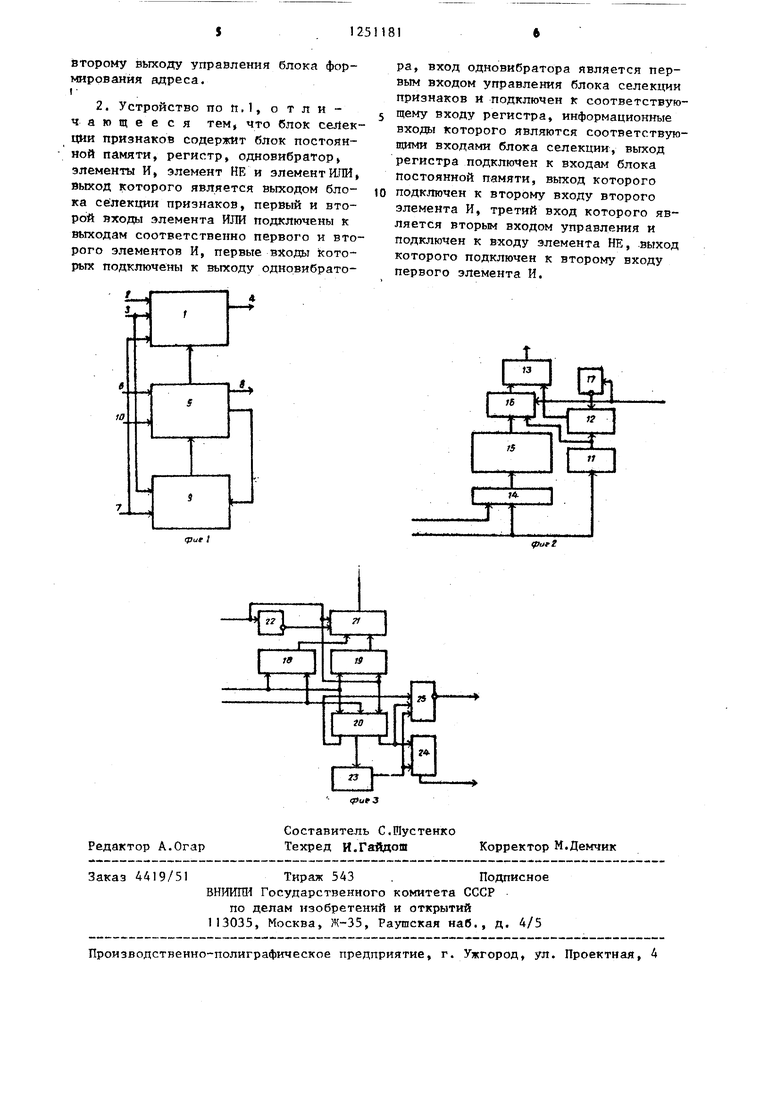

На фиг.1 приведена структурная схема предлагаемого буферного запоминающего устройства; на фиг.2 - структурная схема блока селекции адресных признаков информации; на фиг,3 - структурная схема блока формирования адреса обращения к блоку памяти,

Буферно.е запоминающее устройство содержит блок i памяти с информацион нь;ми входами 2 и 3 и информационными выходами 4, блок 5 формирования адреса, входы 6 и 7 управления, выход 8 управления, блок 9 селекции и вход I О управления.

Блок 9 селекции признаков состоит из одновибратора 11, элемента И 12. элемента Iimi 13, регистра 14, блока 5 постоянной памяти, элемента И 16 и элемента НЕ 17.

Блок 5 формирования адреса выполнен в виде счетчика 18 адреса записи счетчика 19 адреса чтения, реверсивного счетчика 20 объема, элементов И-ИЛИ 2, элемента НЕ 22, элемента ИЛИ 23, элемента И 24, и элемента ИЛИ-НЕ 25.

Устройство наиболее эфсЬективно может .быть использовано в многоканальных системах сбора, регистрации и обработки измерительной информации в которых принадлежность данных к соответствующему каналу определяется кодом специально выделенных разрядов слова (признак информации). Оно выполняет две операции: запись данных в блок памяти и чтение данных из блока памяти, в моменты, определяемые приходом соответствующих сигналов синхронизации. Однако в режиме записи алгоритм работы устройства зависит от степени заполнения информацией блока памяти. При пустом или заполненном до заранее определенной границы (величины) блоке памяти модификация текущего адреса записи в блоке формирования адреса обращения к блоку памяти производится после

5

1:

5

0

0

5

0

5

0

5

П2

записи каждого информационного слова, поступающего на вход устройства. После заполнения блока памяти до определенной величины, близкой к максимальной емкости блока памяти, в последнем записывается лишь наиболее ценная с точки зрения пользователя информация, выделение которой производится по ее признаку. В блоке селекции признаков информации устройства содержится запоминающее устройство, в котором по адресам, однозначно соответствующим кодам признаков измерительных каналов 5 записаны признаки выделения или невыделения данньтх этих каналов для записи в блоке памяти. Каждый раз при поступлении на вход устройства данных того или иного канала производится обращение к этому запоминающему устройству по адресу, соответствующему коду признака, и в случае наличия по этому адресу в запоминающем устройстве признака выделения данные этого канала записываются в блок памяти. Тем самым снижается вероятность переполнения буферного запоминающего устройства.

Буферное запоминающее устройство работает следующим образом.

Перед началом работы сигнапом на входе 10 осуществляют начальную установку устройства. При этом счетчики 19, 18 и 20 блока 5 формирования адреса устанавливаются в нулевое состояние. Высокий уровень сигнала на выходе элемента ИЛИ-НЕ 25, т.е. на выходе В управления устройства, свидетельствует о том, что в буферном запоминающем устройстве отсутствует информация для чтения..

С приходом информационной посылки на входы 2 в сопровождении признака, поступающего на входы 3, и синхросигнала на входе 7 управления устройства осуществляется запись данных в блок памяти по адресу, сформированному на адресных выходах блока 5 формирования адреса. При этом к адрес- нътм выходам блока 5 подключаются через открытые для этого элементы И- ШШ 21 выходные разрядные сигналы счетчика 18 адреса записи. Запись данных в блок 1 памяти производится сигналом на входе 7 управления устройства. Одновременно этот сигнал поступает на вход одновибратора I1 блока 9 селекции признаков, Одновиб3

ратор I 1 формирует по заднему фронту поступающего на него сит нала коротки и myльc, который проходит через открытый элемент И 12 и элемент ИЛИ 13 на выход блока 9. Этот сигнал, посту пая на второй вход блока 5, производит модификацию содержимого счетчика 18 адреса записи (добавляется единица) и счетчика 20 объема (добавляется единица).. Запись последующих ин- формационных посылок производится аналогично до тех пор, пока на второ выходе управления блока 5 формирования адреса обращения к блоку памяти не появится высокий уровень сигнала-, свидетельствующий о том, что в блок 1 памяти записано количество информации, близкое к его заполнению, В это случае запросы на запись информации в буферное запоминающее устройство выполняются следующим образом.

С приходом информационной посылки на входы 2 в сопровождении признака, поступающего на входы 3, синхросигналом на входе 7 управления устройства осзпцествляется запись данных в блок 1 памяти по текущему адресу записи, сформированному на адресных выходах блока 5. Одновременно с зтим по переднему фронту сигнала на входе 7 управления производится запись адресного признака информации в регистр 14 блока 9 селекции. По заднему фронту сигнала на входе 7 управления одно- вибратор П формирует импульс опроса, который поступает на один из входов элемента И 16, В блоке 15 постоянной памяти по адресам, однозначно соответствующим адресным признакам каналов, несущих наиболее ценную с точ- ки зрения пользователя информацию, записаны единичные биты, по всем остальным адресам - нулевые биты информации. Производится обращение к блоку 15 по адресу, соответствующе- му адресному признаку информации, присутствующей на информационных входах 2 устройства, и в случае наличия по данному адресу единичного бита информации на выходе элемента И 16, а следовательно, на выходе элемента ИЛИ 13 появляется сигнал, который производит модификацию содержимого счетчика 18 адреса записи и счетчика 20 объема. Запись последующих инфор- мационных посыпок в буферное запоминающее устройство при высоком уровне сигнала на втором выходе управле

251

й - 5 Юм Т5 м20

25зо , о 45 $055

35

1814

ния блока 5 фop Q-Ipoвaния адреса обращения к блоку памяти производится ана ггогично.

При поступлении запроса на чтение информации, который можтю сделать в любое время при условии низкого уровня сигнала на выходе 8 управления буферного запоминающего устройства, производится чтение из блока I памяти по адресу, сфортф о ванному на адресных выходах блока 5 формирования адреса, на выходные информационные шины 4 устройства. При этом на первом входе 6 управле1шя устройства подключает через открытые для этого элементы И-И.ТО 21 к адресным выходам блока 5 выходные разрядные сигналы счетчика 19 адреса чтения. По окончании чтения задним фронтом сигнала на входе 6 управления производится модификация содержимого счетчика 19 адреса чтения (добавляется единица) и счетчика 20 объема.(вычитается единица), Чтение последующих информационных посылок из буферного запоминающего устройства производится аналогично-. Для Ормальной работы ycTpoficTBa необходимо, чтобы сигналы на первом 6 и втором 7 входах управления устройства были разнесены во времени.

Формула изобретения

1, Буферное запоминающее устройство, содержащее блок памяти, информационные входы первой и второй групп и выходы которых являются соответст- вуюпрнмн входами и выходами устройства, адресные входы блока памяти подключены к соответствующим выходам блока формирования адреса, входы управления блока фop D poвaния адреса и блока памяти являются соответствующими входами ycTpoficTBa, первьш выход управления блока формирования

с

адреса является соответствующим выходом устройства, отличающее- с я тем, что, с целью расширения области применения устройства путем обеспечения избирательной записи данных в накопитель, оно содержит блок селекции признаков, входы группы которого подключены к информационным входам второй группы блока памяти, первый и второй входы блока селекции признаков подключены соответственно к входу управления блока памяти и к

второму выходу управления блока формирования адреса.

I

2. Устройство по п,1, отличающееся тем, что блок cejteK- ции признаков содержит блок постоянной памяти, регистр, одновибратор, элементы И, элемент НЕ и элемент ИЛИ, йыход которого является выходом блока селекции признаков, первый и второй входы элемента ИЛИ подключены к выходам соответственно первого и второго элементов И, первые входы которых подключены к выходу одновибрато

pa, вход одновибратора является первым входом управления блока селекции признаков и подключен к соответствующему входу регистра, информационные входы которого являются соответствующими входами блока селекции, выход регистра подключен к входам блока постоянной памяти, выход которого подключен к второму входу второго элемента И, третий вход которого является вторым входом управления и подключен к входу элемента НЕ, .выход которого подключен к второму входу первого элемента И.

фиг t

Редактор А.Огар

tffueS

Составитель С.Шустенко Техред И.ГайДош

4419/51

Тираж 543 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений н открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

pufg

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1120407A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

Изобретение отиосится к запоминающим устройствам и мoжet быть использовано в качестве буферногб запоминающего устройства в системах сбора, регистрации и обработки многоканальной измерительной информации. Целью изобретения является повьшение надежности устройства а также расширение области его применения .путем обеспечения избирательной записи данных в накопитель. Устройство содержит блок памяти, блок формирования адреса, блок селекции. Блок селекции содержит однойибратор, элементы И, ИЛИ, НЕ, регистр, блок постоянной памяти. Блок формирования адреса содержит счетчик адреса записи, счетчик адреса чтения, реверсивный счетчик объема, элементы И-ИЛИ, НЕ, ИЛИ, И, ИПИ-НЕ. 1 з.п.ф-лы, 3 ил. а ш

| Буферное запоминающее устройство | 1982 |

|

SU1048515A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ГИДРАВЛИЧЕСКИЙ ДВИГАТЕЛЬ | 1941 |

|

SU63357A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-04—Подача