1 1

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для селекции информационных каналов в многоканальных системах сбора, регистра дии и обработки информации.

Целью изобретения является упрощение устройства путем оптимизации алгоритма работы.

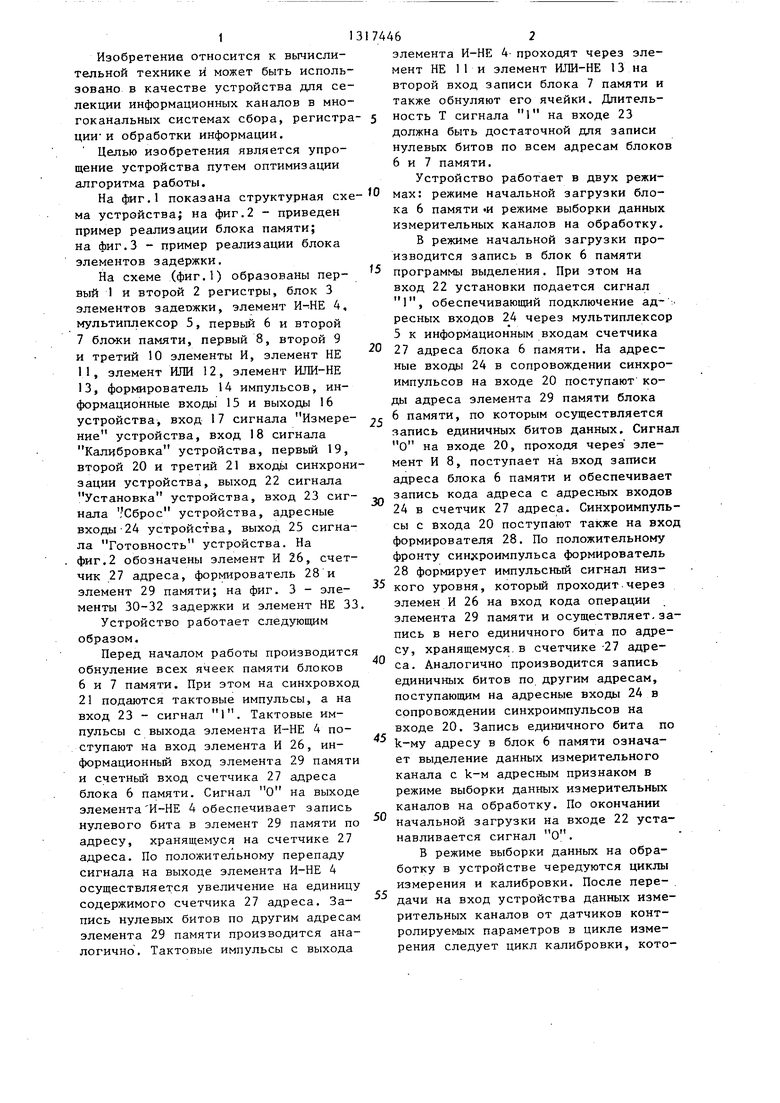

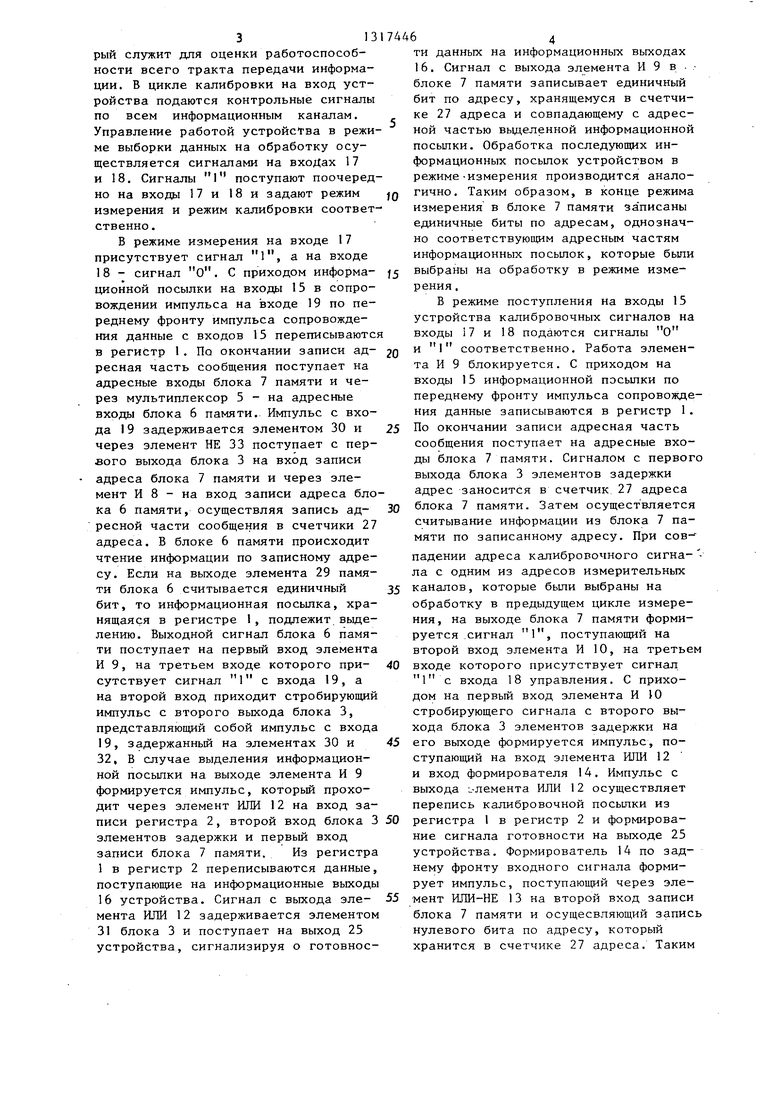

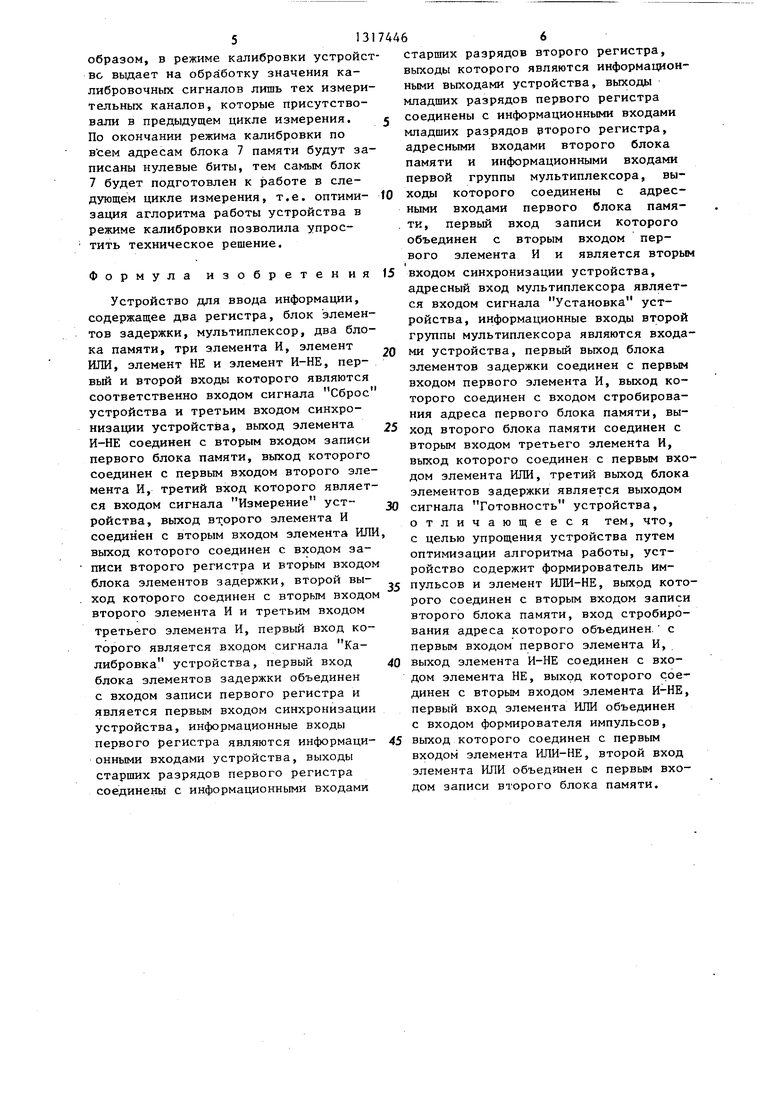

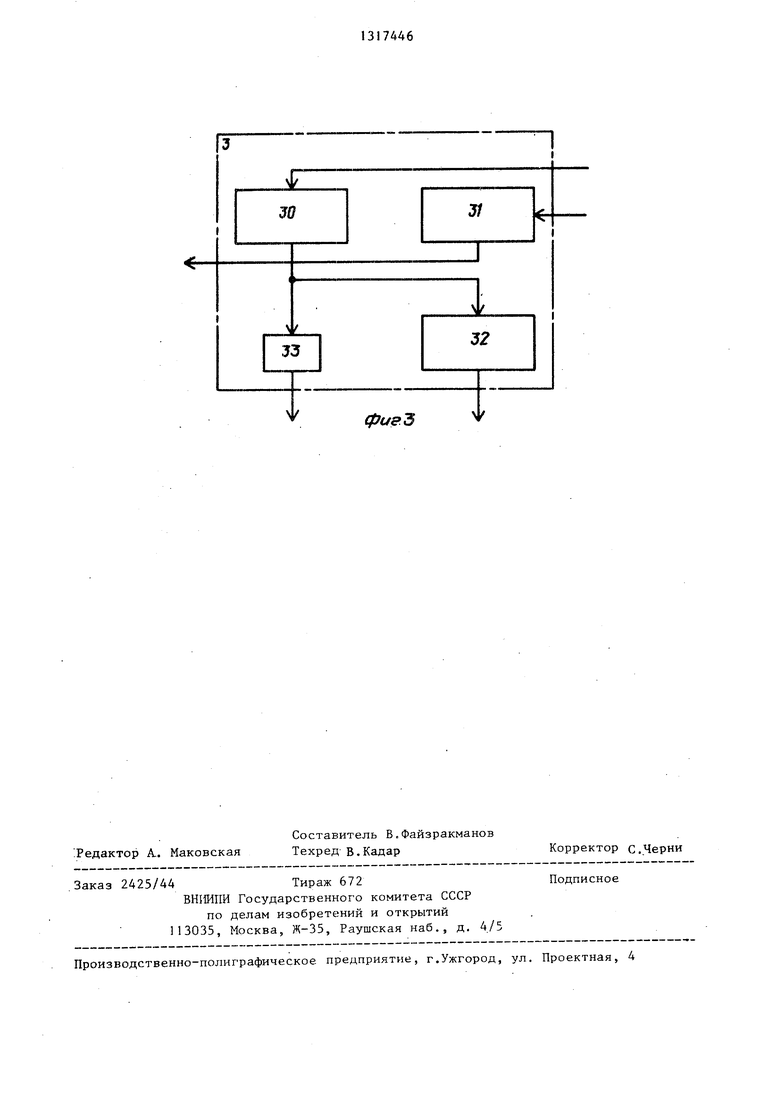

На фиг.1 показана структурная схе ма устройства; на фиг.2 - приведен пример реализации блока памяти; на фиг.З - пример реализации блока элементов задержки.

На схеме (фиг.1) образованы первый 1 и второй 2 регистры, блок 3 элементов задеожки, элемент И-НЕ 4, мультиплексор 5, первьй 6 и второй 7 блоки памяти, первый 8, второй 9 и третий 10 элементы И, элемент НЕ 11, элемент ИЛИ 12, элемент ИЛИ-НЕ 13, формирователь 14 импульсов, информационные входы 15 и выходы 16 устройства, вход 17 сигнала Измерение устройства, вход 18 сигнала Калибровка устройства, первый 19, второй 20 и третий 21 входь синхрони зации устройства, выход 22 сигнала Установка устройства, вход 23 сиг- Нала /Сброс устройства, адресные входы-24 устройства, выход 25 сигнала Готовность устройства. На фиг.2 обозначены элемент И 26, счетчик 27 адреса, формирователь 28 и элемент 29 памяти; на фиг. 3 - элементы 30-32 задержки и элемент НЕ 33

Устройство работает следующим образом.

Перед началом работы производится обнуление всех ячеек памяти блоков 6 и 7 памяти. При этом на синхровход 21 подаются тактовые импульсы, а на вход 23 - сигнал 1. Тактовые импульсы с выхода элемента И-НЕ 4 поступают На вход элемента И 26, информационный вход элемента 29 памяти и счетньш вход счетчика 27 адреса блока 6 памяти. Сигнал О на выходе элемента И-НЕ 4 обеспечивает запись нулевого бита в элемент 29 памяти по адресу, хранящемуся на счетчике 27 адреса. По положительному перепаду сигнала на выходе элемента И-НЕ 4 осуществляется увеличение на единицу содержимого счетчика 27 адреса. Запись нулевых битов по другим адресам элемента 29 памяти производится аналогично . Тактовые импульсы с выхода

174462

элемента И-НЕ 4- проходят через элемент НЕ 11 и элемент ИЛИ-НЕ 13 на второй вход записи блока 7 памяти и также обнуляют его ячейки. Длитель5 ность Т сигнала 1 на входе 23

должна быть достаточной для записи нулевых битов по всем адресам блоков 6 и 7 памяти.

Устройство работает в двух режи О мах: режиме начальной загрузки блока 6 памяти «и режиме выборки данных измерительных каналов на обработку. В режиме начальной загрузки производится запись в блок 6 памяти 5 программы выделения. При этом на вход 22 установки подается сигнал 1, обеспечивающий подключение ад- ресных входов 24 через мультиплексор

5к информационным входам счетчика 20 27 адреса блока 6 памяти. На адресные ВХОДЬ 24 в сопровождении синхроимпульсов на входе 20 поступают коды адреса элемента 29 памяти блока

6памяти, по которым осуществляется запись единичных битов данных. Сигнал о на входе 20, проходя через элемент И 8, поступает на вход записи адреса блока 6 памяти и обеспечивает запись кода адреса с адресных входов 24 в счетчик 27 адреса. Синхроимпульсы с входа 20 поступают также на вход формирователя 28. По положительному фронту сингсроимпульса формирователь 28 формирует импульсный сигнал кого уровня, которьй проходит через элемен И 26 на вход кода операции элемента 29 памяти и осуществляет, запись в него единичного бита по адресу, хранящемуся, в счетчике -27 адреса. Аналогично производится запись единичных битов по другим адресам, поступающим на адресные входы 24 в сопровождении синхроимпульсов на входе 20. Запись единичного бита по k-му адресу в блок 6 памяти означает выделение данных измерительного канала с k-м адресным признаком в режиме выборки данных измерительных каналов на обработку. По окончании

25

30

40

50

начальной загрузки на входе 22 устанавливается сигнал о.

В режиме выборки данных на обработку в устройстве чередуются циклы измерения и калибровки. После пере- . дачи на вход устройства данных измерительных каналов от датчиков контролируемых параметров в цикле измерения следует цикл калибровки, который служит для оценки работоспособности всего тракта передачи информации. В цикле калибровки на вход устройства подаются контрольные сигналы по всем информационным каналам, Управление работой устройства в режиме выборки данных на обработку осуществляется сигналами на входах 17 и 18. Сигналы 1 поступают поочередно на входы 17 и 18 и задают режим измерения и режим калибровки соответственно.

В режиме измерения на входе 17 присутствует сигнал 1, а на входе 18 - сигнал о. С приходом информа- ционной посылки на входы 15 в сопровождении импульса на входе 19 по переднему фронту импульса сопровождения данные с входов 15 переписываютс в регистр 1. По окончании записи ад- ресная часть сообщения поступает на адресные входы блока 7 памяти и через мультиплексор 5 - на адресные входы блока 6 памяти. Импульс с входа 19 задерживается элементом 30 и через элемент НЕ 33 поступает с первого выхода блока 3 на вход записи адреса блока 7 памяти и через элемент И 8 - на вход записи адреса блока 6 памяти, осуществляя запись ад- ресной части сообщения в счетчики 27 адреса. В блоке 6 памяти происходит чтение информации по записному адресу. Если на выходе элемента 29 памяти блока 6 считывается единичный бит, то информационная посылка, хранящаяся в регистре 1, подлежит выделению. Выходной сигнал блока 6 памяти поступает на первый вход элемента И 9, на третьем входе которого при- сутствует сигнал 1 с входа 19, а На второй вход приходит стробирующий импульс с второго выхода блока 3, представляющий собой импульс с входа 19, задержанный на элементах 30 и 32, В случае выделения информационной посылки на выходе элемента И 9 формируется импульс, которьй проходит через элемент ИЛИ 12 на вход записи регистра 2, второй вход блока 3 элементов задержки и первый вход записи блока 7 памяти. Из регистра 1 в регистр 2 переписываются данные, поступающие на информационные выходы 16 устройства. Сигнал с выхода эле- мента ИЛИ 12 задерживается элементом 31 блока 3 и поступает на выход 25 устройства, сигнализируя о готовности данных на информационных выходах 16. Сигнал с выхода элемента И 9 в блоке 7 памяти записывает единичный бит по адресу, хранящемуся в счетчике 27 адреса и совпадающему с адресной частью выделенной информационной посылки. Обработка последующих информационных посылок устройством в режиме-измерения производится аналогично. Таким образом, в конце режима измерения в блоке 7 памяти записаны единичные биты по адресам, однозначно соответствующим адресным частям информационных посыпок, которые бьши выбраны на обработку в режиме измерения .

В режиме поступления на входы 15 устройства калибровочных сигналов на входы 17 и 18 подаются сигналы О и 1 соответственно. Работа элемента И 9 блокируется. С приходом на входы 15 информационной посылки по переднему фронту импульса сопровождения данные записываются в регистр 1. По окончании записи адресная часть сообщения поступает на адресные входы блока 7 памяти. Сигналом с первог выхода блока 3 элементов задержки адрес заносится в счетчик 27 адреса блока 7 памяти. Затем осуществляется считывание информации из блока 7 памяти по записанному адресу. При совпадении адреса калибровочного сигна- ла с одним из адресов измерительных каналов, которые бьши выбраны на обработку в предыдущем цикле измерения, на выходе блока 7 памяти формируется сигнал 1, поступающий на второй вход элемента И 10, на третье входе которого присутствует сигнал 1 с входа 18 управления. С приходом На первый вход элемента И Ю стробирующего сигнала с второго выхода блока 3 элементов задержки на его выходе формируется импульс, поступающий на вход элемента ИЛИ 12 и вход формирователя 14. Импульс с выхода :--лемента ИЛИ 12 осуществляет перепись калибровочной посылки из регистра 1 в регистр 2 и формирование сигнала готовности на выходе 25 устройства. Формирователь 14 по заднему фронту входного сигнала формирует импульс, поступающий через элемент ИЛИ-НЕ 13 на второй вход записи блока 7 памяти и осущесвляющий запис нулевого бита по адресу, который хранится в счетчике 27 адреса. Таким

образом, в режиме калибровки устройство вьщает на обработку значения калибровочных сигналов лишь тех измерительных каналов, которые присутствовали в предыдущем цикла измерения. По окончании режима калибровки по в сем адресам блока 7 памяти будут записаны нулевые биты, тем самым блок 7 будет подготовлен к работе в следующем цикле измерения, т.е. оптимизация аглоритма работы устройства в режиме калибровки позволила упростить техническое решение.

Формула изобретения

Устройство для ввода информации, содержащее два регистра, блок элементов задержки, мультиплексор, два блока памяти, три элемента И, элемент ИЛИ, элемент НЕ и элемент И-НЕ, первый и второй входы которого являются соответственно входом сигнала Сброс устройства и третьим входом синхронизации устройства, выход элемента И-НЕ соединен с вторым входом записи первого блока памяти, выход которого соединен с первым входом второго элемента И, третий вход которого является входом сигнала Измерение устройства, выход вт.орого элемента И соединен с вторым входом элемента ИЛИ выход которого соединен с входом записи второго регистра и вторым входом блока элементов задержки, второй выход которого соединен с вторым входом второго элемента И и третьим входом третьего элемента И, первьй вход которого является входом сигнала Калибровка устройства, первый вход блока элементов задержки объединен с входом записи первого регистра и является первым входом синхронизации устройства, информационные входы первого регистра являются информационными входами устройства, выходы старших разрядов первого регистра соединены с информационными входами

старших разрядов второго регистра, вгэ1ходы которого являются информационными выходами устройства, выходы младших разрядов первого регистра соединены с информационными входами младших разрядов второго регистра, адресными входами второго блока памяти и информационными входами первой группы мультиплексора, выходы которого соединены с адресными входами первого блока памяти, первый вход записи которого объединен с вторым входом первого элемента И и является вторым входом синхронизации устройства, адресный вход мультиплексора является входом сигнала Установка устройства, информационные входы второй группы мультиплексора являются входами устройства, первый выход блока элементов задержки соединен с первым входом первого элемента И, выход которого соединен с входом стробирова- ния адреса первого блока памяти, выход второго блока памяти соединен с вторым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, третий выход блока элементов задержки является выходом сигнала Готовность устройства, отличающееся тем, что, с целью упрощения устройства путем оптимизации алгоритма работы, устройство содержит формирователь им- 5 пульсов и элемент ИГШ-НЕ, выход которого соединен с вторым входом записи второго блока памяти, вход стробиро- вания адреса которого объединен. с первым входом первого элемента И, выход элемента И-НЕ соединен с входом элемента НЕ, выход которого соединен с вторьм входом элемента И-НЕ, первый вход элемента ИЛИ объединен с входом формирователя импульсов, выход которого соединен с первым входом элемента ИЛИ-НЕ, второй вход элемента ИЛИ объединен с первым входом записи второго блока памяти.

0

5

0

0

5

.Редактор А.. Маковская

Составитель В.Файзракманов Техред- В.Кадар

.Заказ 2425/44Тираж 672Подписное

ВНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

фигЗ

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Устройство для ввода информации | 1985 |

|

SU1290337A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сортировки информации | 1987 |

|

SU1478210A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Устройство для адресации буферной памяти | 1988 |

|

SU1587517A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

Изобретение относится к вычислительной технике и может быть использовано дпя селекции информационных каналов в многоканальных системах сбора,.регистрации и обработки информации. Цель изобретения - упрощение устройства за счет оптимизации алгоритма работы. Устройство содержит два регистра, блок элементов задержки, элемент И-НЕ, мультиплексор. два блока памяти, три элемента И, элемент НЕ, элемент ИЛИ, элемент ИЛИ-НЕ, формирователь импульсов. Перед началом работы производится обнуление блоков памяти. Затем в первый блок памяти по сигналу Установка заносится информация о номерах входных каналов, подлежащих обработке. После этого чередуются циклы измерения и калибровки. В цикле измерения информация, поступающая на устройство, сортируется на основе признаков, записанных в первом блоке памяти. Во второй блок памяти заносится информация о нормах каналов, реально обработанных в цикле измерения. В режиме калибровки информация из второго блока памяти передается в ЭВМ, после чего второй блок памяти обнуляется.. После окончания калибровки устройство переходит в цикл измерения или при необходимости - в режим обнуления и установки. 3 ил. i (Л С со 4 О5

| Устройство для селекции информационных каналов | 1982 |

|

SU1070538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1985 |

|

SU1290337A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-06-15—Публикация

1985-12-05—Подача