Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства систем контроля функционирования средств вычислительной техники и автоматики.

Цель изобретения - расширение функциональных возможностей устройства за счет циклического воспроизведения информации.

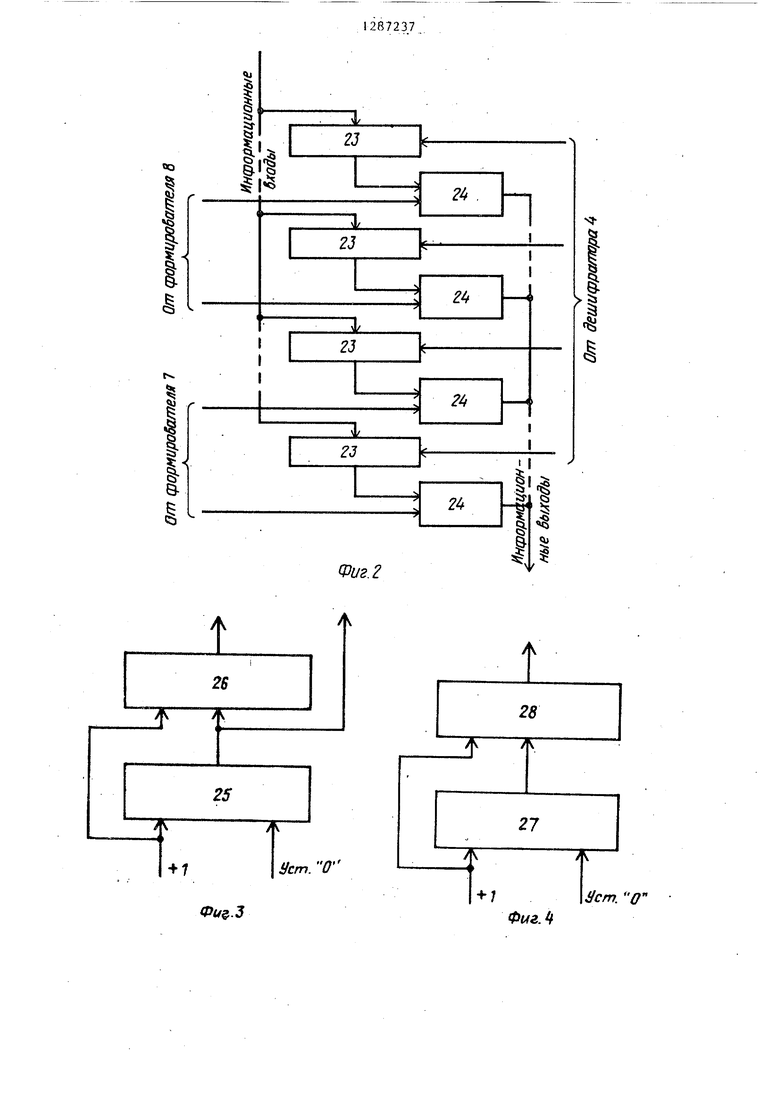

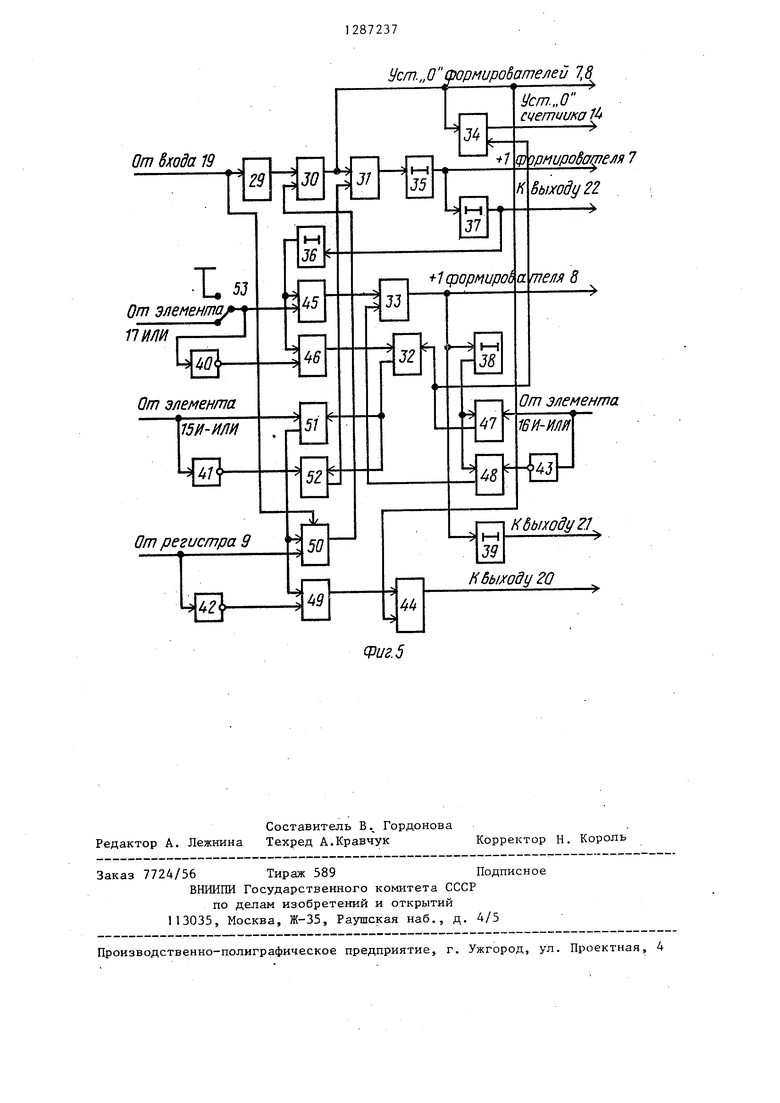

На фиг. 1 приведена структурная схема буферного запоминающего устройства; на фиг. 2 - структурная схема блока памяти; на фиг. 3 - структурная схема первого формирователя сигналов чтения; на фиг. 4 - структурная схема второго формирователя сигналов чтения; на фиг. 5 - структурная схема блока синхронизации.

Буферное запоминающее устройство содержит блок 1 памяти с информационными входами 2 и выходами 3, дешифратор 4 сигналов записи, адресные входы 5, первый вход 6 управления, первый формирователь 7 сигналов чтения, второй формирователь .8 сигналов чтения, первый регистр 9, второй регистр 10, первый дешифратор 11, второй дешифратор 12, третий дешифратор 13, счетчик 14, первый элемент И-ИЛИ 15,.. второй элемент И-ИЛИ 16, элемент ШШ 17, блок 18 синхронизации, второй вход 19 управления и выходы 20-22 управления.

Блок 1 памяти содержит регистры 23 и элементы И 24.

Формирователь 7 сигналов чтения содержит счетчик 25 и дешифратор 26, а формирователь 8 сигналов чтения - счетчик 27 и дешифратор 28.

Блок 1В синхронизации содержит формирователь 29, элементы ИЛИ 30-34, элементы 35-39 задержки, эЛементы НЕ 40-43, триггер 44, элементы И 45- 52 и переключатель 53. Блок 18 синхронизации может быть выполнен в виде микропрограммного автомата.

Устройство работает следующим образом.

Устройство может работать в режиме записи данных и в режиме чтения данных.

Б режиме записи данных на информационные входь: 2 поступают записываемые в .блок 1 памяти данные в сопровождении кода адреса на адресных входах 5 и сигнала на входе 6 управления . Сигнал на входе 6 управления

5

0

5

0

5

0

5

0

5

поступает на вход стробирования де- пшфратора 4, выходной сигнал которого осуществляет запись данных с шин 2 в регистр 23, код адреса которого присутствует на входах 5 устройства. Запись данных в другие регистры 23 блока 1 памяти производится аналогично .

Блок 1 памяти функционально разделен на два поля: поле для хранения командной информации и поле для хранения данных, которые сопровождают командную информацию. Каждое поле состоит из набора регистров, имеюш 1х последовательно возрастающие адреса. Так, при использовании предлагаемого устройства для тестирования устройств .управления накопителями на магнитн1ой ленте в поле командной информации могут записываться коды команд СЧИТАТЬ, ЗАШСАТЬ, ШАГ НА ЗОНУ ВПЕРЕД, ЗАПИСАТЬ МАРКЕР ГРУППЫ ЗОН и т.д., а в поле данных заносятся коды данных, сопровождающих некоторые из команд, например команду ЗАПИСАТЬ. Количество информационных слов в поле данных значительно меньше количества информационных слов в блоке данных, сопровождающих командную информацию. Так, в описанном примере с тестированием устройств управления накопителями на магнитной ленте в поле данных могут быть лишь два информационных слова, каждое соответственно с нулевыми и единичными битами, а длина L блока данных может быть различной (16, 32,...,1024 слова) и значительное превьш1ающей L 2.

Коды длины блока данных и коды количества командных слов, используемые в текущем цикле тестирования, наряду с признаком циклического их выполнения записываются в регистр 9. Запись данных в регистр 9, который имеет свой собственный адрес, производится аналогично записи в регистры 23 блока 1 памяти. По окончании записи данных в регистры 23 и 9 устройство готово к выполнению операции чтения.

Режим чтения начинается по высокому уровню сигнала на входе 19 управления устройства, который поступает на вход блока 18 синхронизации. Сигнал на входе 19 управления поступает на вход формирователя 29 блока 18 синхронизации, который по переднему фронту вырабатывает сигнал.

поступающий через элемент ИЛИ 30 на установочные входы формирователей 7 и.8 и триггер 44 блока 18 синхронизации и через элемент ИЛИ 34 на установочный вход счетчика 14, уста- навливая их в исходные нулевые состояния. Сигнал, на выходе элемента ИЛИ 30 через элемент ИЛИ S1 и элемент 35 задержки поступает на вход стробирования дешифратора 26 форми- рователя 7, выходной сигнал которого осуществляет чтение данных из первого регистра 23 командного поля блока 1 .памяти через соответствующие элементы И 24 на информационные.вы- ходы 3. Счетчик 25 модифицирует свое содержимое по заднему фронту сигнала на выходе элемента 35 задержки. Передним фронтом сигнала на выходе элемента 35 задержки, задержанным на элементе 37 задержки, осуществляется запись командного слова в регистр 10, указанный сигнал поступает на выход 22 устройства как идентификатор командного слова. Дешифратор 13 и элемент ИЛИ 17 определяют необходимость передачи набора данных за считанным ранее командным словом. Если имеется такая необходимость, то на выходе элемента ИЛИ I7 присутствует высокий уровень сигнала, который через элемент И 45 блока 18 синхронизации разрешает прохождение сигнала с выхода элемента 36 задержки через элемент ИЛИ 33 на вход стробирования дешифратора 28 формирователя 8, выходной сигнал которого производит чтение на информационные выходы 3 устройст- ва слова данных из первого регистра 2 поля данных блока 1 памяти через соот ветствующие элементы И 24. Сигнал на выходе элемента 39 задержки является идентификатором слова данных и поступает на выход 21 управления устройства. Сигнал, задержанный на элемен- те 38 задержки, поступает на входа элементов И 47 и 48, на которых проверяется выполнение условия окончания передачи блока данных. Счет переданнь х данных в блоке осуществляется счетчиком 14, который изменяет свое состояние по заднему фронту сигнала на выходе элемента ИЛИ 33. Дешифратор 1I вьщеляет соответствующие состояния счетчика 14, которые срав- ниваются с заданными на второй группе выходов регистра 9. Сравнение про- ийводится на элементе И-ИЛИ 16. В

случае передачи требуемого объема в блоке данных на выходе элемента И-ШШ 16 присутствует высокий уровень сигнала. В противном случае высокий уровень сигнала на выходе элемента НЕ 43 разрешит прохождение сигнала с элемента 38 задержки через элемент И 48 на вход элемента ИЛИ 33 и цикл выдачи данных на информационные выходы 3 устройства повторится. При этом данные будут считываться из следующего по порядку регистра 23 блока 1 памя ги. По окончании передачи блока данных высокий уровень сигнала появится на входе элемента И 47 и сигнал с выхода элемента 38 за- держки через элемент И 47 и элемент ИЛИ 34 сбросит в нулевое состояние счетчик 14. Одновременно с этим сигнал с выхода элемента И 47 через элемент ИЛИ 32, на второй вход которого поступает сигнал с выхода элемента 36 задержки через элемент И 46 в случае если предыдущее считанное командное слово не требовало передачи данных, поступает на входы элементов И 51 и 52, где проверяется условие окончания выдачи командных слов. Счет пе- реданны с командных слов производится на счетчике 25 формирователя 7,который изменяет свое состояние по заднему фронту сигнала на выходе элемента 35 задержки. Сигналы с выходов счетчика 25 поступают на дешифратор 12, который выделяет соответствующие состояния счетчика 25, которые затем сравниваются с заданными на первой группе выходов регистра 9. Сравнение производится на элементе И-ШШ 15. В случае передачи требуемого количества командных Слов на выходе элемента И-ИЛИ 15 присутствует высокий уровень сигнала. В противном случае высокий уровень сигнала на выходе элемента НЕ 41 разрешит прохождение сигнала с выхода элемента ИЛИ 3 через элемент И 52 на вход элемента ИЛИ 31 и будет выполнен цикл выдачи следующего командного .слова. При этом командное слово будет считываться из следующего по порядку регистра 23 .командного поля блока 1 памяти. По окончании передачи требуемого количества командных слов высокий уровень сигнала на входе элемента И 51 разрешит прохождение сигнала с выхода элемента ИЛИ 32 на входы элементов И 49 и 50, где проверяется

выполнение условия циклического выполнения ранее переданного набора командных слов. Циклическое выполнение набора командных слов задается высоким уровнем сигнала на выходе одного из разрядов регистра 9. При этом высокие уровни сигналов на входах элемента И 50 (продолжительность циклического выполнения набора командных слов задается временем подцержа- fO сигналов чтения, первый и второй рения высокого уровня на входе 19 управления устройства) разрешает прохождение -сигнала с выхода элемента И 51 через элемент И 50 на вход элемента ИЛИ 30, что приведет к повторению выдачи набора командных слов. В противном случае при отсутствии условия циклического выполнения командных слов высокий.уровень сигнала на Выходе элемента НЕ 42 разрешит прохождение через элемент И 49 сигнала с выхода элемента И 51, который установит триггер 44 в единичное состояние, и на выходе 20 управления устройства появится высокий уровень сигнала, свидетельствующий об окой- чании режима чтения информации. В режиме циклического чтения набора командных слов триггер 44 не устанавли

гистры, первьй, второй и третий де шифраторы, первый и второй элемент И-ИЛИ, счетчик, элемент ИЖ и блок синхронизации, причем выходы второ t5 формирователя сигналов чтения соед нены с другими входами управления чтения блока памяти, установочные входы первого и второго формироват лей сигналов чтения подключены к п вому выходу блока синхронизации,уп равляющие входы.второго формироват ля сигналов чтения и счетчика соед нены с вторым выходом блока синхро низации, третий выход которого под ключен К управляющему входу первог формирователя сигналов чтения, пят и шестой йыходы блока синхронизаци являются соответственно первым и в рым выходами управл ения устройства

вается в единичное состояние, а окон- 30 седьмой выход блока синхронизации

чание режима чтения задается снятием высокого уровня сигнала на входе 19 управления устройства.

Переключатель 53 устанавливается в положение, при котором блокируется передача сигналов через элемент И 45 в том случае, если в процессе работы не требуется сопровождение командных слов данными.

Изобретение позволяет эффективнее использовать аппаратные средства в процессе проведения контроля функционирования средств вычислительной техники.

Формула изобретения

Буферное запоминазощее устройство, содержащее блок памяти, информацион- ные входы и выходы которого являются

соответственно информационными входа- 50 соответственно к информационным вхоми и выходами устройства, дешифратор сигналов..записи, стробирующий вход которого является первым входом управления устройства, один из входов дешифратора сигналов записи является адресным входом устройства, входы управления записью блока памяти подключены к выходам дешифратора

сигналов записи, одни входы управления чтением блока памяти соединены с соответствующими выходами первого формирователя сигналов чтения, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет циклического воспроизведения информации, оно содержит второй формирователь

гистры, первьй, второй и третий дешифраторы, первый и второй элементы И-ИЛИ, счетчик, элемент ИЖ и блок синхронизации, причем выходы второго формирователя сигналов чтения соединены с другими входами управления чтения блока памяти, установочные входы первого и второго формирователей сигналов чтения подключены к первому выходу блока синхронизации,управляющие входы.второго формирователя сигналов чтения и счетчика соединены с вторым выходом блока синхронизации, третий выход которого подключен К управляющему входу первого формирователя сигналов чтения, пятый и шестой йыходы блока синхронизации являются соответственно первым и вто- рым выходами управл ения устройства.

седьмой выход блока синхронизации

подключен к входу записи второго регистра и является третьим выходом управления устройства, а первый вход блока синхронизации является вторым

входом управления устройства, второй, третий, четвертый и пятый входы блока синхронизации соединены соответственно с выходом первого элемента И-ИЛИ, выходом второго элем ента И-ИЛИ, выходом элемента ИЛИ и, выходом первого регистра, одни входы второго элемента И-ИЛИ подключены к соответствующим выходам первого де- шифратора, входы которого подключены

к соответствующим выходам счетчика, другие входы второго элемента И-ИЛИ соединены с соответствующими выходами первого регистра, информационные входы и выходы которого подключены

дам устройства и одним входам первого элемента И-ИЛИ, другие входы кото-, рого подключены к соответствующим выходам второго дешифратора, входы которого соединены с соответствующими выходами первого формирователя сигналов чтения, вход записи первого регистра подключен к выходу дешифратоpa сигналов записи, информационные входы второго регистра соединены с информационными выходами блока памяти, выходы второго регистра соединены с соответств тощими входами тре-

тьего дешифратора, выходы которого соединены с соответствующими входами элемента ИЛИ, а четвертый выход блока синхронизации подключен к адресному входу счетчика.

Фи.З

Уст.„0 дк}рмиро8ателец 7,8

От ёхода 19

трмиробошеля

От элемента

сриг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сортировки информации | 1987 |

|

SU1478210A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

| Устройство для сортировки информации | 1986 |

|

SU1606972A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

Изобретение может быть использовано в качестве буферного запоминающего устройств систем контроля функционирования средств автоматики и вычислительной техники. Цель изобретения состоит в расширении функциональных возможностей за счет введения в устройство, содержащее блок памяти, дешифгатор сигналов записи, формирователь сигналов чтения, второго форьшрователя сигналов чтения, счетчика, двух регистров, элемента ШШ, блока синхронизации и двух: элементов И-ИЛИ. Это-позволит организовывать раз:шчные режимы чтения информации из блока памяти за -счет циклического воспроизведения информации. 5 ил. (Л с 1C 00 ч to 00

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1084896A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-11—Подача