Изобретение относится к импульсной технике и может быть использовано в радиосвязи.

Цель изобретения - расширение функциональных возможностей генератора псевдослучайной последовательности импульсов за счет обеспечения возможности регулирования фазоврсменных параметров формируемой последов тель- ности.

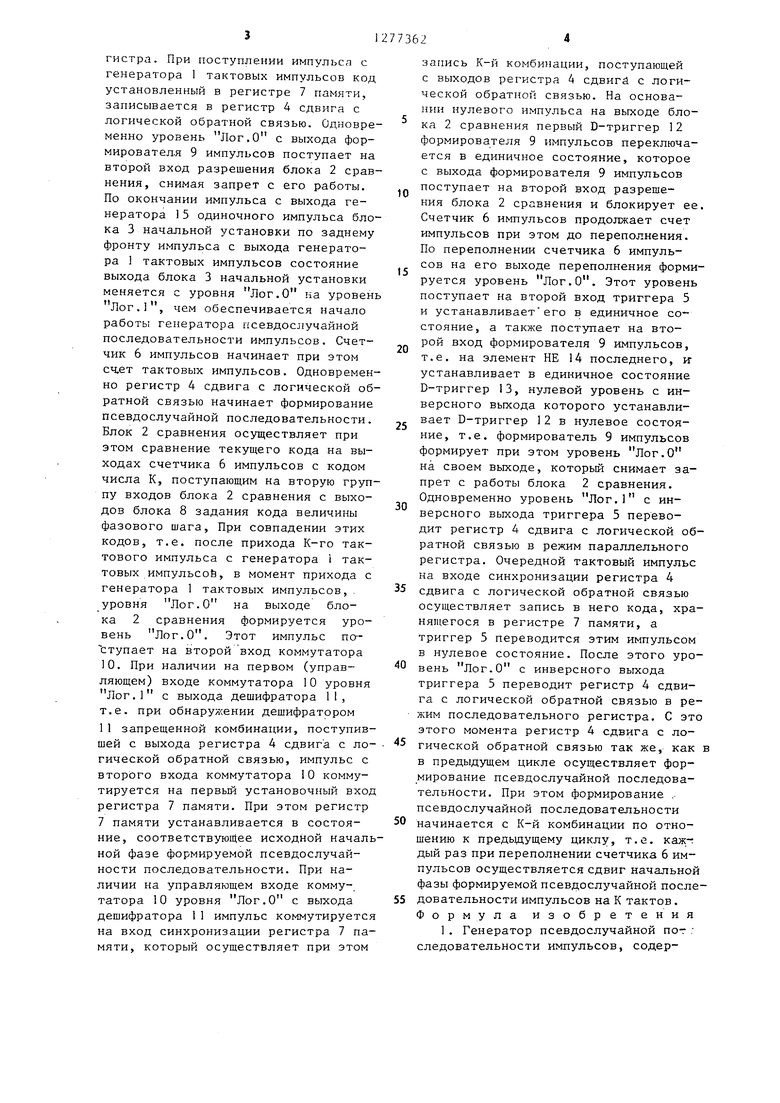

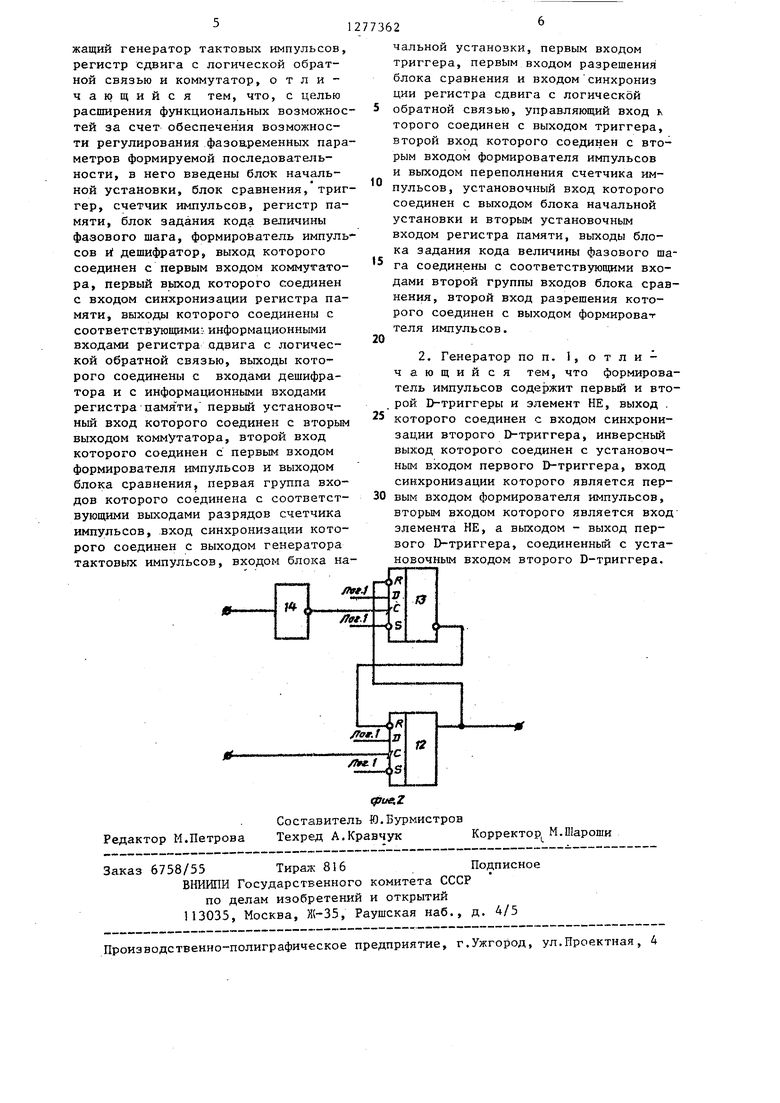

На фиг.1 представлена структурная схема генератора псевдослучайной последовательности импульоов; на фиг.2 - схема формирователя импульсов, пример выполнения.

Генера тор псевдослучайной последовательности импульсов (фиг.1) содержит генератор I тактовых импульсов, блок 2 сравнения, блок 3 начальной установки, регистр 4 сдвига с логической обратной связью, триггер 5, счетчик 6 импульсов, регистр 7 памяти, блок 8 задания кода величины фазового шага, формирователь 9 импульсов, KOMNryTaTOp 10, дешифратор 11, выход которого соединен с первым входом коммутатора 10, первый выход которого соединен с входом синхронизации регистра 7 памяти, выходы кото-т рого соединены с соответствующими информационными входами регистра 4 сдвига с логической обратной связью, выходы которого соединены с входами дешифратора 11 и с информационными входами регистра 7 памяти, первый, установочный вход которого соединен с вторым выходом коммутатора 10, . второй вход которого соединен с первым входом формирователя 9 импульсов и выходом блока 2 сравнения, первая группа входов которого соединена с соответству1ош,ими выходами разрядов счетчика 6 импульсов, вход синхронизации которого соединен с выходом . генератора 1 тактовых импульсов, входом блока 3 начальной установки, первым входом триггера 5, первым входом разрешения блока 2 сравнения и входом синхронизации регистра 4 сдвига с ло- гуческой обратной связью, управляющий вход которого соединен с выходом триггера 5, второй вход которо- го соединен с вторым входом формирователя 9 импульсов и выходом переполнения счетчика 6 импульсов, установочный вход которого соединен с выходом блока 3 начальной установки и вторым установочным входом

регистра 7 памяти. Выходы блока 8 задания кода величины фазового шага соединены с соответствующими входами второй группы входов блока 2 сравнения, второй вход разрешения которого соединен с выходом формирователя 9 импульсов.

Формирователь 9 импульсов (фиг.2) содержит первый 12 и второй 13 D- .

триггеры, элемент НЕ 14, выход которого соединен с входом синхронизации второго D-триггера 13, инверсный .выход которого соединен с установочным входом первого D-триггера

12, вход синхронизации которого является первым входом формирователя 9 импульсов, вторым входом которого является вход элемента НЕ 14, а выходом - выход первого D-триггера 12, соединенный с установочным входом второго D-триггера 13.

Блок 3 начальной установки выполнен в виде последовательно соединенных генератора 15 одиночного импульса и D-триггера 16, вход и выход которого являются соответственно входом и выходом блока 3 начальной установки.

Генератор псевдослучайной последовательности импульсов работает следующим образом.

При включении питания генератор 15 одиночного импульса блока 3 начальной установки формирует импульс,

который обнуляет D-триггер 16 и на выходе блока 3 начгшьной установки формируется уровень Лог.О. Этот уровень, поступая на установочный вход счетчика 6 импульсов, педеводит его в состояние переполнения, а поступая на второй установочный вход регистра 7 памяти, устанавливает его в заданное состояние, которое определяет исходную начальную

фазу формируемой псевдослучайной последовательности. По окончании тактового импульса на тактовом входе счетчика 6 импульсов на его выходе переполнения формируется уровень Лог.О, который поступает на. вторые входы (установки в О) триггера 5 и формирователя 9 импульсов, которые устанавливаются в нулевое состояние. С инверсного выхода триггера 5 уровень Лог.1 поступает на управляющий вход регистра 4 сдвига с логической обратной связью и пере- водит его в режим параллельного регистра. При поступлении импульса с генератора 1 тактовых импульсов код установленный в регистре 7 памяти, записывается в регистр 4 сдвига с логической обратной связью. Одновременно уровень Лог,О с выхода фор- мировател.я 9 импульсов поступает на второй вход разрешения блока 2 сравнения, снимая запрет с его работы. По окончании импульса с выхода генератора 5 одиночного импульса блока 3 начальной установки по заднему фронту импульса с выхода генератора 1 тактовых импульсов состояние выхода блока 3 начальной установки меняется с уровня Лог.О на уровень Лог.1, чем обеспечивается начало работы генератора псевдослучайной последовательности импульсов. Счетчик 6 импульсов начинает при этом счет тактовых импульсов. Одновременно регистр 4 сдвига с логической обратной связью начинает формирование псевдослучайной последовательности. Блок 2 сравнения осуществляет при этом сравнение текущего кода на выходах счетчика 6 импульсов с кодом числа К, поступающим на вторую группу входов блока 2 сравнения с выходов блока 8 задания кода величины фазового шага, При совпадении этих кодов, т.е. после прихода К-го тактового импульса с генератора 1 тактовых импульсоЬ, в момент прихода с генератора 1 тактовых импульсов,. уровня Лог.О на выходе блока 2 сравнения формируется уровень Лог.О. Этот импульс по- ступает на второй вход коммутатора 0. При наличии на первом (управляющем) входе коммутатора 10 уровня Лог.1 с выхода дешифратора 11, т.е. при обнаружении дешифратором 11 запрещенной комбинации, поступившей с выхода регистра 4 сдвига с ло- гической обратной связью, импульс с второго входа коммутатора 10 коммутируется на первый установочный вход регистра 7 памяти. При этом регистр 7 памяти устанавливается в состояние, соответствующее исходной начальной фазе формируемой псевдослучайности последовательности. При наличии на управляющем входе комму-, татора 10 уровня Лог.О с выхода дешифратора 11 импульс коммутируется на вход синхронизации регистра 7 памяти, который осуществляет при этом

0

5

0

5

0

5

0

5

запись К-й комбинации, поступающей с выходов регистра 4 сдвига с логической обратной связью. На основании нулевого импульса на выходе блока 2 сравнения первый D-триггер 12 формирователя 9 импульсов переключается в единичное состояние, которое с выхода формирователя 9 импульсов поступает на второй вход разрешения блока 2 сравнения и блокирует ее. Счетчик 6 импульсов продолжает счет импульсов при этом до переполнения. По переполнении счетчика 6 импульсов на его выходе переполнения формируется уровень Лог.О. Этот уровень поступает на второй вход триггера 5 и устанавливает его в единичное состояние, а также поступает на второй вход формирователя 9 импульсов, т.е. на элемент НЕ 14 последнего, и- устанавливает в единичное состояние D-триггер 13, нулевой уровень с инверсного выхода которого устанавливает D-триггер 12 в нулевое состояние, т.е. формирователь 9 импульсов формирует при этом уровень Лог.О на своем выходе, который снимает запрет с работы блока 2 сравнения. Одновременно уровень Лог.1 с инверсного выхода триггера 5 переводит регистр 4 сдвига с логической обратной связью в режим параллельного регистра. Очередной тактовый импульс на входе синхронизации регистра 4 сдвига с логической обратной связью осуществляет запись в него кода, хранящегося в регистре 7 памяти, а триггер 5 переводится этим импульсом в нулевое состояние. После этого уровень Лог.О с инверсного выхода триггера 5 переводит регистр 4 сдвига с логической обратной связью в режим последовательного регистра. С это этого момента регистр 4 сдвига с логической обратной связью так же, как в в предыдущем цикле осуществляет формирование псевдослучайной последовательности. При этом формирование . псевдослучайной последовательности начинается с К-й комбинации по отношению к предьздущему циклу, т.е. каж-г дый раз при переполнении счетчика 6 импульсов осуществляется сдвиг начальной фазы формируемой псевдослучайной последовательности импульсов на К тактов. Формула изобретения 1. Генератор псевдослучайной пот : следовательности импульсов, содержащий генератор тактовых импульсов, регистр сдвига с логической обратной связью и коммутатор, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности регулирования фазоаременных параметров формируемой последовательности, в него введены блок начальной установки, блок сравнения, триггер, счетчик импульсов, регистр памяти, блок задания кода величины фазового шага, формирователь импульсов Hf дешифратор, выход которого соединен с первым входом коммутатора, первый выход которого соединен с входом синхронизации регистра памяти, выходы которого соединены с соответствующими; информационными входами регистра сдвига с логической обратной связью, выходы которого соединены с входами дешифратора и с информационными входами регистра памя ти, первый установочный вход которого соединен с вторым выходом коммутатора, второй вход которого соединен с первым входом формирователя импульсов и выходом блока сравнения, первая группа входов которого соединена с соответствующими выходами разрядов счетчика импульсов, вход синхронизации которого соединен с выходом генератора тактовых импульсов, входом блока на77362°

чальной установки, первым входом триггера, первым входом разрешения блока сравнения и входом синхрониз ции регистра сдвига с логической обратной связью, управляющий вход к торого соединен с выходом триггера, второй вход которого соединен с вторым входом формирователя импульсов и выходом переполнения счетчика импульсов, установочный вход которого соединен с выходом блока начальной установки и вторым установочным входом регистра памяти, выходы блока задания кода величины фазового шага соединены с соответствующими входами второй группы входов блока сравнения, второй вход разрешения которого соединен с выходом формироват теля импульсов.

10

15

20

2. Генератор по п. 1, отличающийся тем, что формирователь импульсов содержит первьй и вто- . рой D-триггеры и злемент НЕ, выход .

25 которого соединен с входом синхронизации второго D-триггера, инверсный выход которого соединен с установочным входом первого D-триггера, вход синхронизации которого является пер30 вым входом формирователя импульсов, вторым входом которого является вход- элемента НЕ, а выходом - выход первого D-триггера, соединенный с установочным входом второго D-триггера,

Редактор М.Петрова

фие.г

Составитель Ю.Бурмистров

Техред А.Кравчук KoppeKTopj М.Шароши

Заказ 6758/55 Тираж 816 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайной последовательности импульсов | 1986 |

|

SU1368959A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

| Устройство для имитации сбоев | 1990 |

|

SU1836684A3 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор псевдослучайных чисел | 1983 |

|

SU1185582A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

Изобретение может быть использовано в радиосвязи. Целью изобретения является расширение функциональных возможностей. Для достижения цели в генератор псевдослучайной последовательности импульсов введены блок 3 начальной установки блок 2 сравнения, триггер 5, счетчик 6 импульсов, регистр 7 памяти, блок 8 задания кода величины фазового шага, формирователь 9 им- пульсон и дешифратор 11. Генератор псевдослучайной последовательности импульсов также содержит генератор 1 тактовых импульсов, регистр 4 сдвига с логической обратной связью, коммутатор 10. Данный генератор обеспечивает возможность регулирования фазовременных параметров формируе - мой последовательности.1з.п.ф-лы.2ил. f (Л с

| Генератор псевдослучайных последовательностей импульсов | 1978 |

|

SU769715A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор псевдослучайных последовательностей | 1978 |

|

SU725211A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-15—Публикация

1985-05-13—Подача