to сд

4

09 Ю

I i

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств работающих, например, в позиционноостаточной системе сч:исления (ПОС).

Цель изобретения - повьшение быстродействия.

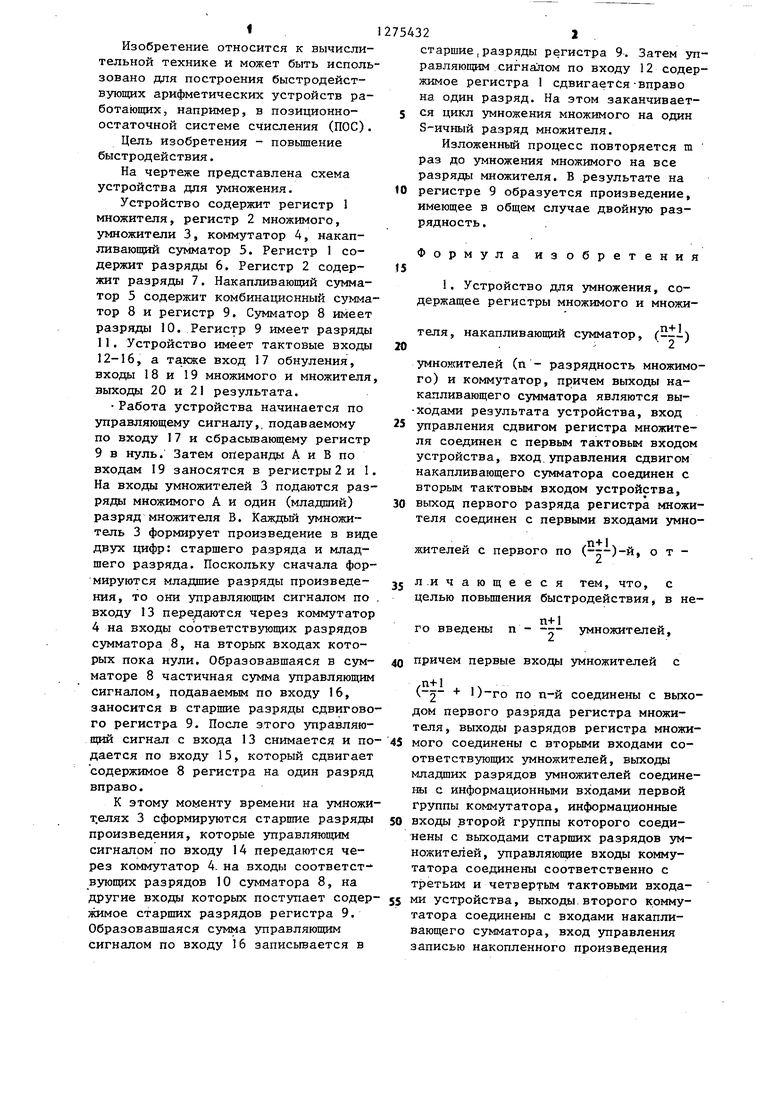

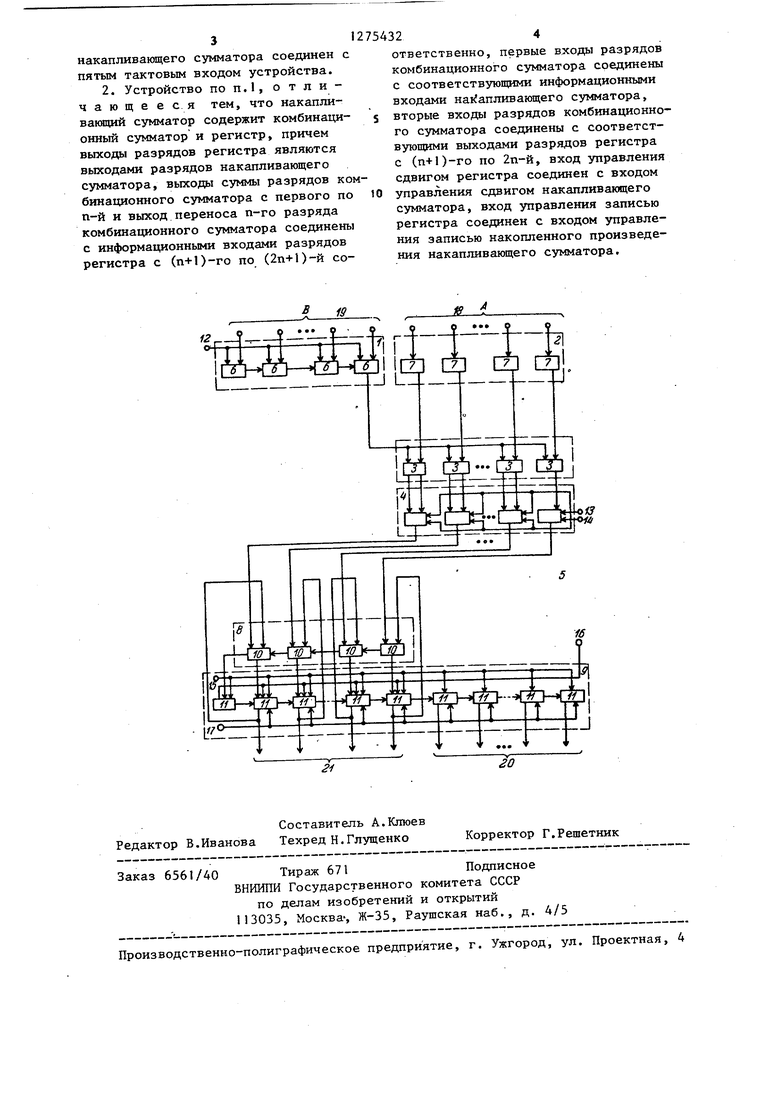

На чертеже представлена схема устройства для умножения.

Устройство содержит регистр 1 множителя, регистр 2 множимого, умножители 3, коммутатор 4, накапливающий сумматор 5. Регистр 1 содержит разряды 6, Регистр 2 содержит разряды 7. Накапливающий сумматор 5 содержит комбинационный сумматор 8 и регистр 9. Сумматор 8 имеет разряды 10, Регистр 9 имеет разряды 11. Устройство имеет тактовые входы 12-16, а также вход 17 обнуления, входы 18 и 19 множимого и множителя, выходы 20 и 21 результата.

Работа устройства начинается по управляющему сигналу,, подаваемому по входу 17 и сбрасьшающему регистр 9 в нуль. Затем операнды А и В по входам 19 заносятся в регистры 2 и 1. На входы умножителей 3 подаются разряды множимого А и один (младший) разряд множителя В. Каждый умножитель 3 формирует произведение в виде двух цифр: старшего разряда и младшего разряда. Поскольку сначала формируются младшие разряды произведения, то они управляющим сигналом по входу 13 передаются через коммутатор 4 на входы соответствующих разрядов сумматора 8, на вторых входах которых пока нули. Образовавшаяся в сум маторе 8 частичная сумма управляющим сигналом, подаваемым по входу 16, заносится в старшие разряды сдвигового регистра 9, После этого управляющий сигнал с входа 13 снимается и подается по входу 15, который сдвигает содержимое 8 регистра на один разряд вправо,

К этому моменту времени на умножит.елях 3 сформируются старшие разряды произведения, которые управляющим сигналом по входу 14 передаются через коммутатор 4- на входы соответст взпощих разрядов 10 сумматора 8, на другие входы которых поступает содержимое старших разрядов регистра 9. Образовавшаяся сумма управляющим сигналом по входу 16 записывается в

754322

старшие,разряды регистра 9. Затем управляющим сигналом по входу 12 содержимое регистра 1 сдвигается-вправо на один разряд. На этом заканчивает5 ся цикл умножения множимого на один S-ичный разряд множителя.

Изложенный процесс повторяется m раз до умножения множимого на все разряды множителя, В результате на to регистре 9 образуется произведение, имеющее в общем случае двойную разрядность ,

Формула изобретения

1, Устройство для умножения, содержащее регистры множимого и множителя, накапливаюшзнй сумматор, (---) 2

умножителей (п - разрядность множимого) и коммутатор, причем выходы накапливающего сумматора являются выходами результата устройства, вход

управления сдвигом регистра множителя соединен с первым тактовым входом устройства, вход.управления сдвигом накапливающего сумматора соединен с вторым тактовым входом устройства,

выход первого разряда регистра множителя соединен с первыми входами умно/п+К жителей с первого по (---)-и, о т л.и чающееся тем, что, с целью повьш1ения быстродействия« в неп+1го введены п - --- умножителей,

причем первые входы умножителей с

,,пн-1 ,.

.2 )гo по п-й соединены с выходом первого разряда регистра множителя , выходы разрядов регистра множимого соединены с вторыми входами соответствующих умножителей, выходы младших разрядов умножителей соединеш 1 с информационными входами первой ГРЗШПЫ коммутатора, информационные

входы второй группы которого соединены с выходами старших разрядов умножителей, управляющие входы коммутатора соединены соответственно с третьим и четвертым тактовыми входами устройства, выходы.второго коммутатора соединены с входами накапливающего сумматора, вход управления записью накопленного произведения

накапливающего сумматора соединен с пятым тактовым входом устройства.

2. Устройство по П.1, отличающееся тем, что накапливающий сумматор содержит комбинационный сумматор и регистр, причем выходы разрядов регистра являются выходами разрядов накапливающего сумматора, выходы суммы разрядов кобинационного сумматора с первого по п-й и выход переноса п-го разряда комбинационного сумматора соединены с информационными входами разрядов регистра с (п+1)-го по (2п+1)-й соответственно, первые входы разрядов комбинационного сумматора соединены с соответствующими информационными входами на11 апливающего сумматора, вторые входа разрядов комбинационного сумматора соединены с соответствующими выходами разрядов регистра с (п+1)-го по 2п-й, вход управления сдвигом регистра соединен с входом управления сдвигом накапливающего сумматора, вход управления записью регистра соединен с входом управления записью накопленного произведения накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения | 1975 |

|

SU1206773A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих арифметических устройств, работакицих, например, в позиционно-остаточной системе счисления. Цель изобретения - повышение быстродействия. Устройство содержит регистр множителя, регистр множимого, группу умиожителей, коммутатор и накапливакяций сумматор и соответствующие связи. 1 з.п. ф-лы, 1 ил.

| Авторское свидетельство СССР 754412, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ ПОСЛЕДОВАТЕЛЬНОГО | 0 |

|

SU383044A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1984-12-30—Подача