1

Изобретение относится к области вычислительной техники и может быть использовано при проектировании ариф метических устройств ЦВМ.

Целью изобретения является повышение быстродействия.

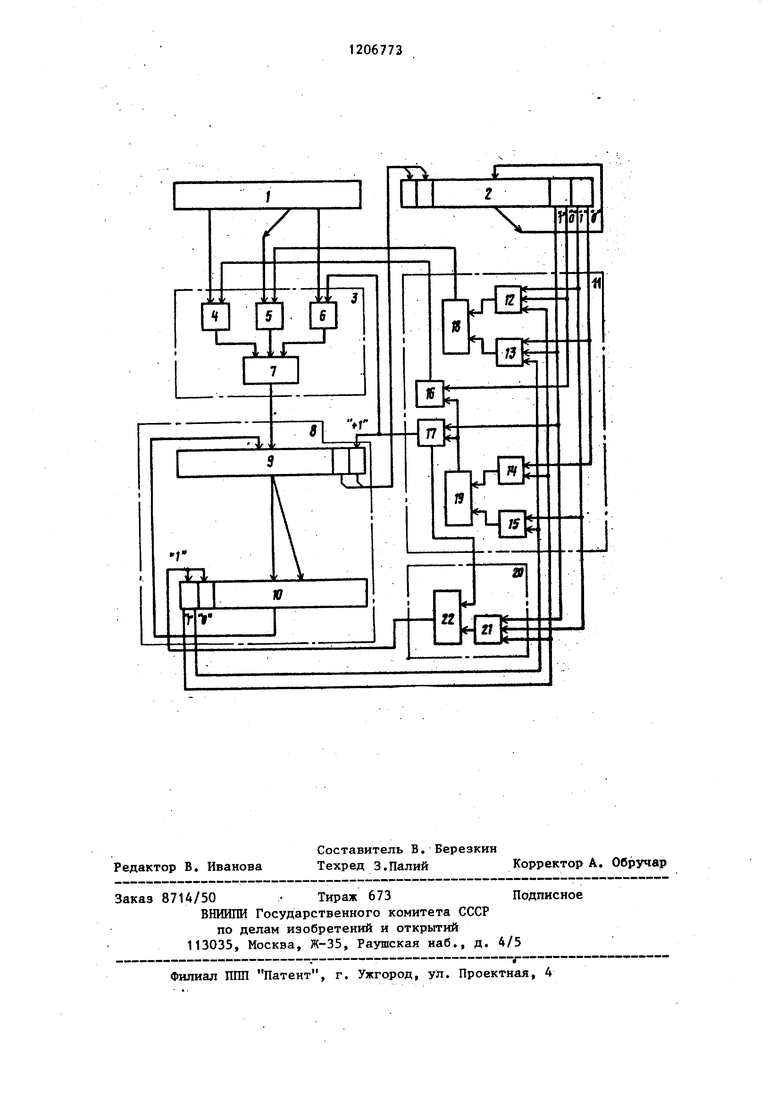

На чертеже представлена функциональная схема устройства для умножения.

Устройство содержит регистр 1 множимого, регистр 2 множителя, коммутатор 3, содержащий группу элементов И 4-6 и группу элементов ИЛИ 7, накапливающий сумматор 8, содержащий комбинационный сумматор 9 и регистр 10, узел 11 управления коммутатором, содержащий элементы И 12-17 и элементы ИЛИ 18 и 19, узел 20 определения знака операции, содержащий элемент И 21 и элемент ИЛИ 22.

Регистры 2 и 10 функционально полные состоят из вспомогательного и основного регистров. Сдвиг содержимого регистров 10 и 2 производится двумя тактирующими импульсами внутри такта или двумя фронтами одного тактирующего импульса..

При умножении двух чисел, заданных в модифицированном дополнительном коде, код множимого заносится в регистр 1, а код множителя - в , регистр 2. В устройстве используется метод умножения на два разряда множителя, начиная с младших его разрядов, при неподвижном множимом. В зависимости от результата исследования пары разрядов множителя предусматриваются следующие действия.

В случае пары 00 производится про- стой сдвиг на два разряда вправо частичного произведения на регистре 10 через 1 мбинационный сумматор 9. В случае пары 01 к сумме частичных произведений прибавляется одинарное множимое и сумма частичных произведем НИИ сдвигается на два разряда вправо В случае пары 10 прибавляется удвоенное множимое и сумма частичных произведений сдвигается на два разряда вправо. В случае пары 11 из суммы частичных произведений вычитается одинарное множимое и сумма частичных произведений сдвигаетсЙ на два разряда вправо. В результате вьиита- ния очередная сумма частичных производных будет, иметь отрицательный знак. На следующем такте умножения

45

- 40 м. 55

206773

должно быть прибавлено одинарное множимое.

Отрицательный знак предыдущей суммы частичных производных учитьта5 ется при обработке следующей пары разрядов. Если следующая пара 00, то она обрабатывается как 01. Если следующая пара 01, то она обраба- тьгоается как ЛЮ. Если следующая

10 пара 10, то она обрабатьгеается как 11-. Если следующая пара 11, то она обрабатывается как 00 и присваивается отрицательный знак очередной сумме частичных произведений

15 (подается 1 на входы знаковых разрядов регистра 10).

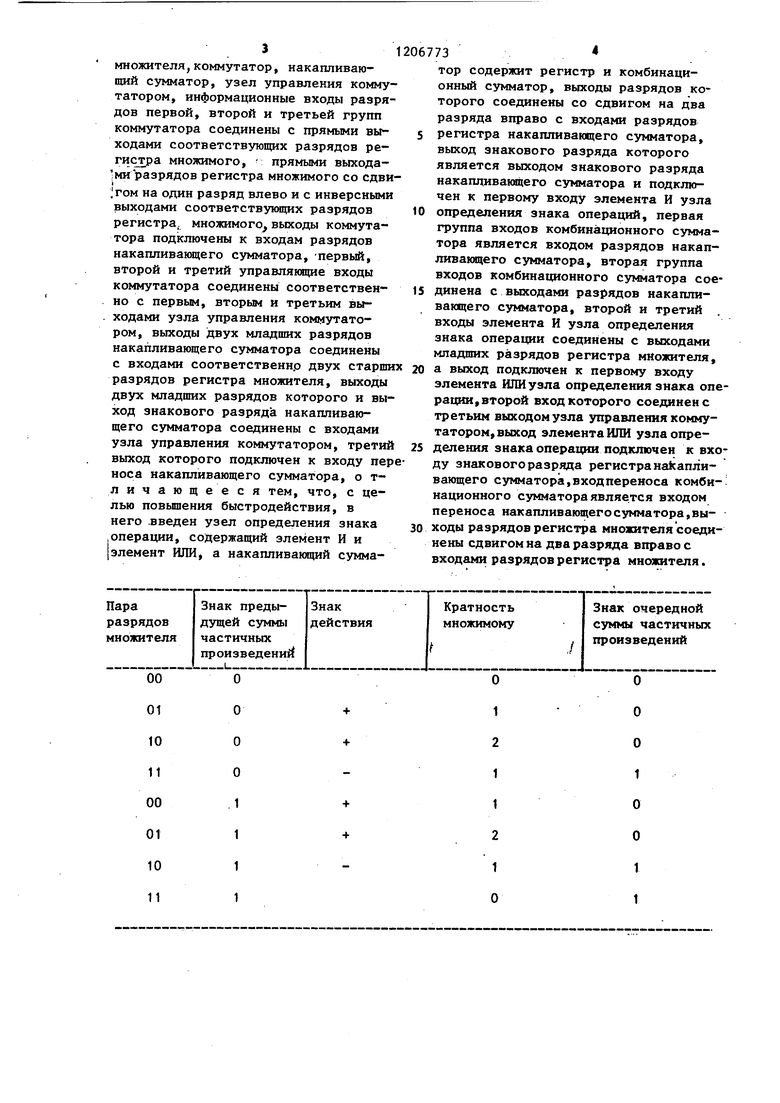

Узлы 11 и 20 функционируют в соответствии с правилами для обработки пар разрядов множителя с учетом зна20 ка предьздущей суммы частичных произведений. Правила сведены в таблицу.

При выполнении вычитания множимое в обратном коде из регистра 1 через коммутатор 3 поступает на входы ком25 бинационного сумматора 9. При этом на вход переноса младщего разряда сумматора 9 подается +1, т.е. на входах сумматора. 9 образуется дополнительный код множимого.

30 При выполнении умножения очередная сумма частичных произведений с сумматора 9 со сдвигом на два разряда вправо записывается в регистр 10, при этом младшие разряды очередной

35 суммы записываются на входы двух старших разрядов регистра множителя 2, поскольку по мере сдвига множителя на два разряда вправо старшие разряды регистра 2 освобождаются.

При выполнении последнего такта умножения очередная сумма частичных произведений с сумматора 9 по параллельным цепям записьшается в регистр 10, при этом на входы двух старших разрядов регистра множителя 2 запи- сьшаются нули (результат операции после выполнения последнего сложения не обязательно должен переписываться в регистр 10, а может быть выбран непосредственно из сумматора 9).

В результате умножения в регистре 10 получаются старшие разряды суммы частичных произведений, а в регистре- 2 - его младшие разряды.

50

Формула изобретения

Устройство для умножения, содержащее регистр множимого, регистр

множителя,коммутатор, накапливающий сумматор, узел управления коммутатором, информационные входы разрядов первой, второй и третьей групп коммутатора соединены с прямыми выходами соответствующих разрядов ре- множимого, прямыми выхода- ми разрядов регистра множимого со сдвиi

. гом на один разряд влево и с инверсными выходами соответствующих разрядов регистра, множимого, выходы коммутатора подключены к входам разрядов накапливающего сумматора, -первый, второй и третий управляющие входы коммутатора соединены соответственно с первым, вторым и третьим выходами узла управления коммутатором, выходы двух младших разрядов накапливающего сумматора соединены с входами соответственнр двух старши разрядов регистра множителя, выходы двух младших разрядов которого и выход знакового разряда накапливающего сумматора соединены с входами узла управления коммутатором, третий выход которого подключен к входу перноса накапливающего сумматора, о т- личающееся тем, что, с целью повышения быстродействия, в него .введен узел определения знака .операции, содержащий злемент И и (злемент ИЛИ, а накапливающий сумма206773

тор содержит регистр и комбинационный сумматор, выходы разрядов которого соединены со сдвигом на два разряда вправо с входами разрядов

5 регистра накапливающего сумматора, выход знакового разряда которого является выходом знакового разряда накапливающего сумматора и подключен к первому входу элемента И узла

10 определения знака операций, первая группа входов комбинационного сумматора является входом разрядов накапливающего сумматора, вторая группа входов комбинационного сумматора соеIS динена с выходами разрядов накашга- вамцего сумматора, второй и третий входы элемента И узла определения знака операции соединены с выходами младших разрядов регистра множителя,

20 а выход подключен к первому входу

элемента ШШузла определения знака операции, второй вход которого соединен с третьим выходом узла управления коммутатором, выход элемента ИЛИ узла опре25 деления знака операции подключен к входу знаковогоразряда регистранатапливающего сумматора,входпереноса комбинационного сумматора является входом переноса накапливакнцегосумматора,вы30 ходы разрядов регистра множителя соединены сдвигом на два разряда вправо с входами разрядов регистра множителя.

Редактор В. Иванова

Составитель В. Березкин

Техред 3.Палий Корректор А. Обручар

Заказ 8714/50 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ПШ1 Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Устройство для умножения | 1974 |

|

SU608156A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

Изобретение относится к области вычислительной техники и может быть использовано при проектировании арифметических устройств ЦВМ. Целью изобретения является повышение быстродействия устройства. Устройство содержит регистр множимого, регистр множителя, коммутатор, группу злементов И, группу элементов ИЛИ, 1 накаш1иваю- 1ЦИЙ сумматор, комбинационный сумма-- тор, регистр, узел управления коммутатором, содержащий шесть элементов И и два элемента ИЛИ. Повышение быстродействия достигается введением узла определения знака операции, содержащего элемент И, элемент ИЛИ. 1 табл. 1 ип. ё INS С о: 00

| Каган Б.М., Каневский М.М | |||

| Цифровые вычислительные машины и системы, м: | |||

| Энергия, 1973, с | |||

| Чемодан с сигнальным замком | 1922 |

|

SU338A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Майоров С.А | |||

| и др | |||

| Принципы организации цифровых машин | |||

| ЛГ Машиностроение, 1974, с | |||

| Приспособление для подачи воды в паровой котел | 1920 |

|

SU229A1 |

Авторы

Даты

1986-01-23—Публикация

1975-07-09—Подача