1 I3

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении ре- конфигурируемых управляющих и вычислительных систем с использованием множества однотипных микропрограммных устройств управления.

Цель изобретения - повышение надежности за счет устранения влияния сбоев на работу и блокировки выдачи искаженной микрокоманды в операционное устройство Г

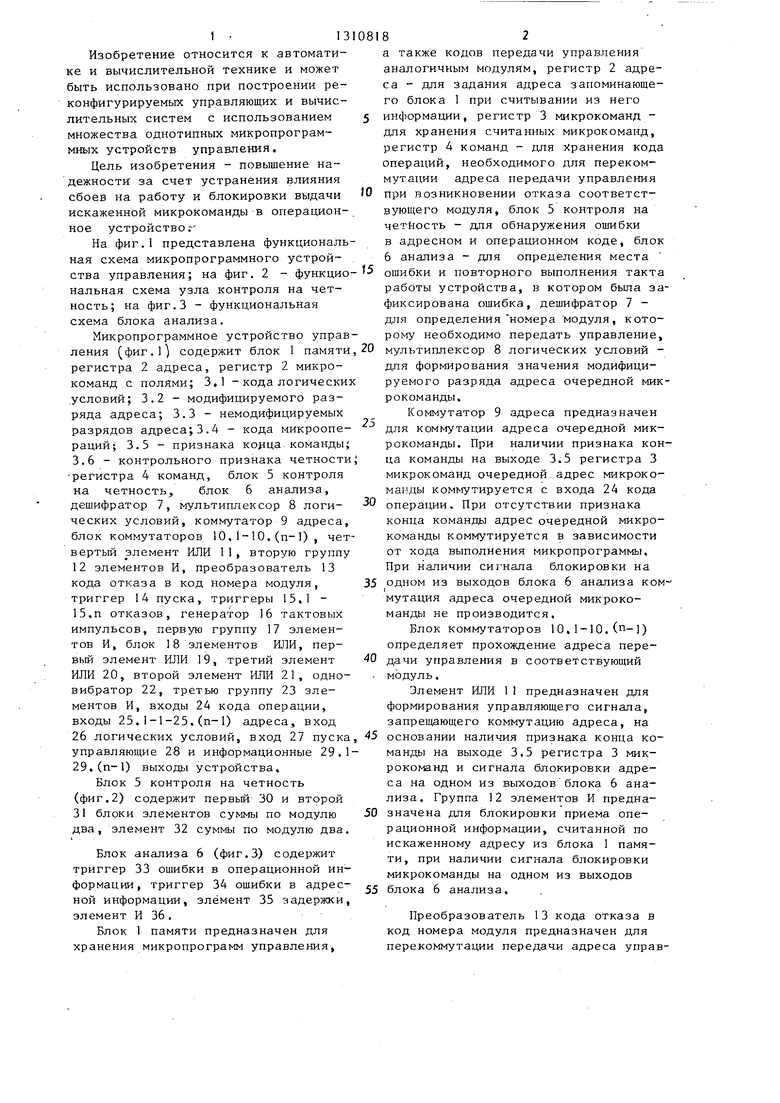

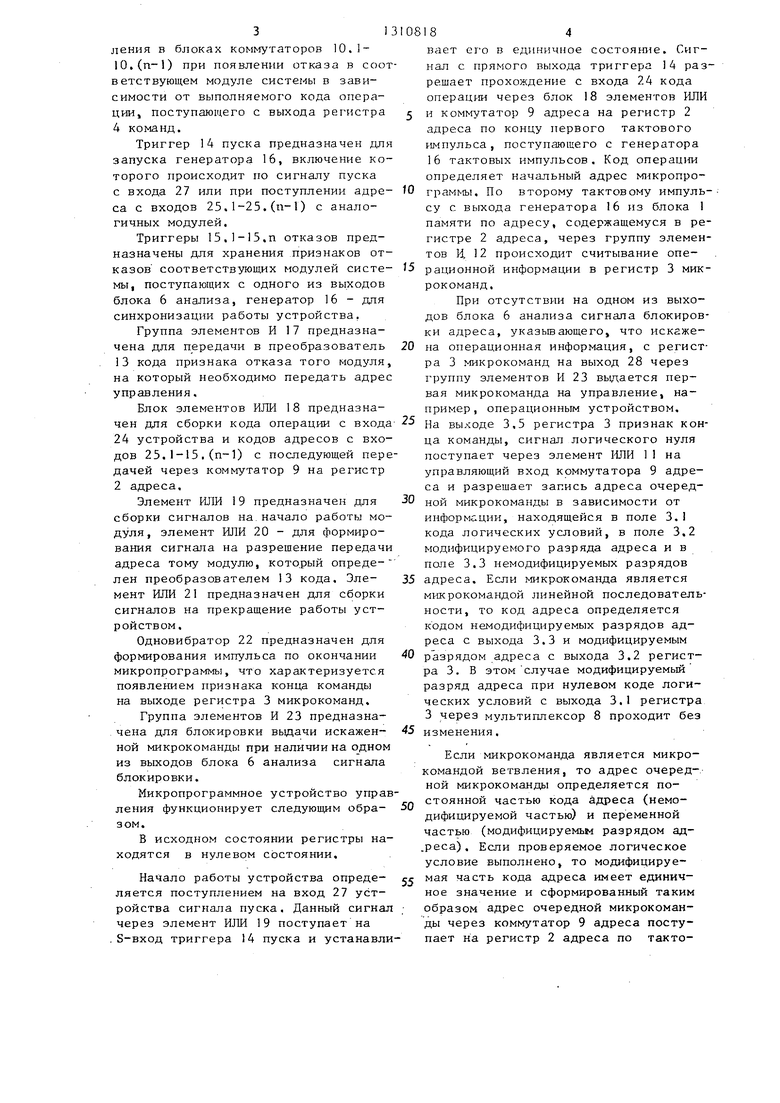

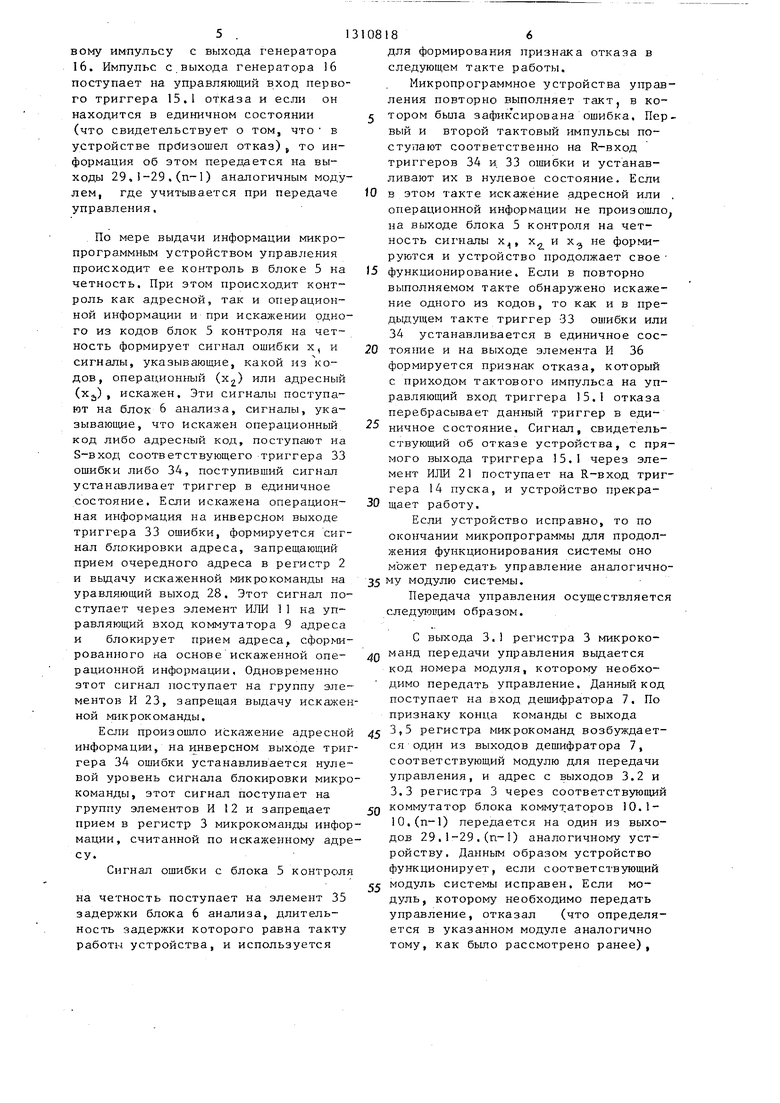

На фиг.1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 - функцио нальная схема узла контроля на четность; на фиг.З - функциональная схема блока анализа.

Микропрограммное устройство управления (фиг.)) содержит блок 1 памяти регистра 2 адреса, регистр 2 микрокоманд с полями; 3.1 - кода логических условий; 3.2 - модифицируемого разряда адреса; 3.3 - немодифицируемых разрядов адреса;3.4 - кода микроопераций; 3.5 - признака команды; 3.6 - контрольного признака четности регистра 4 команд, блок 5 контроля на четностьJ блок 6 анализа, дешифратор 7, мультиплексор 8 логи- ческих условий, коммутатор 9 адреса, блок коммутаторов 10,1 - 10.(п-1) , четвертый элемент ИЛИ 11, вторую группу 12 элементов И, преобразователь 13 кода отказа в код номера модуля, триггер 14 пуска, триггеры 15,1 - 15,п отказов, генератор 16 тактовых импульсов, первую группу 17 элементов И, блок 18 элементов ИЛИ, первый элемент ИЛИ 19, третий элемент ИЛИ 20, второй элемент ИЛИ 21, одно- вибратор 22, третью группу 23 элементов И, входы 24 кода операции, входы 25,1-1-25,(п-1) адреса, вход 26 логических условий, вход 27 пуска управляющие 28 и информационные 29,1 29,(п-1) выходы устройства.

Блок 5 контроля на четность (фиг,2) содержит первый 30 и второй 31 блоки элементов суммы по модулю два, элемент 32 суммы по модулю два.

Блок анализа 6 (фиг,3) содержит триггер 33 ошибки в операционной информации , триггер 34 ошибки в адрес- ной информации, элемент 35 задержки, элемент И 36,

Блок 1 памяти предназначен для хранения микропрограмм управления,

а также кодов передачи управления аналогичным модулям, регистр 2 адреса - для задания адреса запоминаюше- го блока 1 при считывании из него информации, регистр 3 микрокоманд - для хранения считанных микрокоманд, регистр 4 команд - дпя Хранения кода операций, необходимого для перекоммутации адреса передачи управления при возникновении отказа соответствующего модуля, блок 5 контроля на четкость - для обнаружения ошибки в адресном и операционном коде, блок 6 анализа - дпя определения места ошибки и повторного выполнения такта работы устройства, в котором была зафиксирована ошибка, дешифратор 7 - для определения номера модуля, которому необходимо передать управление, мультиплексор 8 логических условий - для формирования значения модифицируемого разряда адреса очередной микрокоманды.

Коммутатор 9 адреса предназначен для коммутации адреса очередной микрокоманды. При наличии признака конца команды на выходе 3,5 регистра 3 микрокоманд очередной, адрес микрокоманды коммутируется с входа 24 кода операции. При отсутствии признака конца команды адрес очередной микрокоманды коммутируется в зависимости от хода выполнения микропрограммы. При наличии сигнала блокировки на одном из выходов блока 6 анализа коммутация адреса очередной микрокоманды не производится.

Блок коммутаторов 10,1-10,(п-) определяет прохождение адреса передачи управления в соответствующий модуль,

Элемент ИЛИ 11 предназначен для формирования управляющего сигнала, запрещающего коммутацию адреса, на основании наличия признака конца команды на выходе 3,5 регистра 3 микрокоманд и сигнала блокировки адреса на одном из выходов блока 6 анализа. Группа 12 элементов И предназначена для блокировки приема операционной информации, считанной по искаженному адресу из блока 1 памяти, при наличии сигнала блокировки микрокоманды на одном из выходов блока 6 анализа.

Преобразователь 13 кода отказа в код номера модуля предназначен для перекоммутации передачи адреса управ31

ления в блоках коммутаторов 10.1- lO.(n-l) при появлении отказа в соответствующем модуле системы в зависимости от выполняемого кода операции, поступающего с выхода регистра 4 команд.

Триггер 14 пуска предназначен для запуска генератора 16, включение которого происходит по сигналу пуска с входа 27 или при поступлении адреса с входов 25.1-25.(п-1) с аналогичных модулей.

Триггеры 15.1-15.П отказов предназначены для хранения признаков отказов соответствующих модулей системы, поступающих с одного из выходов блока 6 анализа, генератор 16 - для синхронизации работы устройства.

Группа элементов И 17 предназначена для передачи в преобразователь 13 кода признака отказа того модуля, на который необходимо передать адрес управления.

Блок элементов ИЛИ 18 предназначен для сборки кода операции с входа 24 устройства и кодов адресов с входов 25.1-15.(п-1) с последующей передачей через коммутатор 9 на регистр 2 адреса.

Элемент ИЛИ 19 предназначен для сборки сигналов на начало работы модуля , элемент ИЛИ 20 - для формирования сигнала на разрешение передачи адреса тому модулю, который опреде- лен преобразователем 13 кода. Элемент ИЛИ 21 предназначен для сборки сигналов на прекращение работы устройством.

Одновибратор 22 предназначен для формирования импульса по окончании микропрограммы, что характеризуется появлением признака конца команды на выходе регистра 3 микрокоманд.

Группа элементов И 23 предназначена для блокировки выдачи искаженной микрокоманды при наличии на одном из выходов блока 6 анализа сигнала блокировки.

Микропрограммное устройство управления функционирует следующим образом,

В исходном состоянии регистры находятся в нулевом состоянии.

Начало работы устройства определяется поступлением на вход 27 устройства сигнала пуска. Данный сигнал через элемент ИЛИ 19 поступает на . S-вход триггера 14 пуска и устанавли184

вает его в единичное состояние. Сигнал с прямого выхода триггера 14 разрешает прохождение с входа 24 кода операции через блок 18 элементов ИЛИ и коммутатор 9 адреса на регистр 2 адреса по концу первого тактового импульса, поступающего с генератора 16 тактовых импульсов. Код операции определяет начальный адрес микропрограммы. По второму тактовому импульсу с выхода генератора 16 из блока 1 памяти по адресу, содержащемуся в регистре 2 адреса, через группу элементов И, 12 происходит считывание операционной информации в регистр 3 микрокоманд.

При отсутствии на одном из выходов блока 6 анализа сигнала блокировки адреса, указьшающего, что искажена операционная информация, с регистра 3 микрокоманд на выход 28 через группу элементов И 23 выдается первая микрокоманда на управление, например , операционным устройством.

На выходе 3.5 регистра 3 признак конца команды, сигнал логического нуля поступает через элемент ИЛИ 11 на управляющий вход коммутатора 9 адреса и разрешает запись адреса очеред

ной микрокоманды в зависимости от

информации, находящейся в поле 3.1 кода логических условий, в поле 3.2 модифицируемого разряда адреса и в поле 3.3 немодифицируемых разрядов

адреса. Если микрокоманда является микрокомандой линейной последовательности, то код адреса определяется кодом немодифицируемых разрядов адреса с выхода 3.3 и модифицируемым

разрядом адреса с выхода 3.2 регистра 3. В этом случае модифицируемый разряд адреса при нулевом коде логических условий с выхода 3.1 регистра 3 через мультиплексор 8 проходит без

изменения.

Если микрокоманда является микроомандой ветвления, то адрес очередной микрокоманды определяется по

стоянной частью кода адреса (немодифицируемой частью) и переменной частью (модифицируемьм разрядом ад- реса). Если проверяемое логическое условие выполнено, то модифицируе- мая часть кода адреса имеет единичное значение и сформированный таким образом адрес очередной микрокоманды через коммутатор 9 адреса поступает на регистр 2 адреса по такте5 .1

вому импульсу с выхода генератора 16. Импульс с выхода генератора 16 поступает на управляющий вход первого триггера 15,1 отказа и если он находится в единичном состоянии (что свидетельствует о том, что в устройстве произошел отказ), то информация об этом передается на выходы 29,-29,(п-1) аналогичным модулем, где учитывается при передаче управления.

По мере выдачи информации микропрограммным устройством управления происходит ее контроль в блоке 5 на четность. При этом происходит контроль как адресной, так и операционной информации и при искажении одного из кодов блок 5 контроля на четность формирует сигнал ошибки х, и сигналы, указывающие, какой из кодов, операционный (х) или адресный (Xj,) , искажен. Эти сигналы поступают на блок 6 анализа, сигналы, ука- зываюиие, что искажен операционньй код либо адресный код, поступают на S-вход соответствующего триггера 33 ошибки либо 34, поступивший сигнал устан шливает триггер в единичное состояние. Если искажена оператдион- ная информация на инверсном выходе триггера 33 ошибки, формируется сигнал блокировки адреса, запрещающий прием очередного адреса в регистр 2 и вьщачу искаженной микрокоманды на уравляющий выход 28. Этот сигнал поступает через элемент ИЛИ 11 на управляющий вход коммутатора 9 адреса и блокирует прием адреса, сформированного на основе искаженной операционной информации, Одновременно этот сигнал поступает на группу элементов И 23, запрещая выдачу искаженной микрокоманды.

Если произошло искажение адресной информации, на инверсном выходе триггера 34 ошибки устанавливается нулевой уровень сигнала блокировки микрокоманды, этот сигнал поступает на группу элементов И 12 и запрещает прием в регистр 3 микрокоманды информации, считанной по искаженному адресу.

Сигнал ошибки с блока 5 контроля

на четность поступает на элемент 35 задержки блока 6 анализа, длительность задержки которого равна такту работы устройства, и используется

8186

для формирования признака отказа в следующем такте работы.

Микропрограммное устройства управления повторно выполняет такт, в ко5 тором была зафик сирована ошибка. Первый и второй тактовый импульсы поступают соответственно на R-вход триггеров 34 и. 33 О1иибки и устанавливают их в нулевое состояние. Если

0 в этом такте искажение адресной или . операционной информации не произошло на выходе блока 5 контроля на четность сигналы х, х и х не формируются и устройство продолжает свое

15 функционирование. Если в повторно выполняемом такте обнаружено искажение одного из кодов, то как и в предыдущем такте триггер 33 ошибки или 34 устанавливается в единичное сос0 тояние и на выходе элемента И 36 формируется признак отказа, который с приходом тактового импульса на управляющий вход триггера 15,1 отказа перебрасывает данный триггер в еди ничное состояние. Сигнал, свидетельствующий об отказе устройства, с прямого выхода триггера 15,1 через элемент ИЛИ 21 поступает на R-вход триггера 14 пуска, и устройство прекра30 щает работу.

Если устройство исправно, то по окончании микропрограммы для продолжения функционирования системы оно может передать управление аналогично;)5 му модулю системы.

Передача управления осуществляется следующим образом.

С выхода 3,1 регистра 3 микроко- 0 манд передачи управления выдается

код номера модуля, которому необхо- димо передать управление. Данный код поступает на вход дешифратора 7. По признаку конца команды с выхода

лс 3,5 регистра микрокоманд возбуждается один из выходов дешифратора 7, соответствующий модулю для передачи управления, и адрес с выходов 3,2 и 3.3 регистра 3 через соответствующий

д коммутатор блока коммутаторов 10,1- 10,(п-1) передается на один из выходов 29,1-29,(п-I) аналогичному устройству. Данным образом устройство функционирует, если соответствующий

ij модуль системы исправен. Если модуль, которому необходимо передать управление, отказал (что определяется в указанном модуле аналогично тому, как было рассмотрено ранее),

713

то передача управления осуществляется в зависимости от выполняемой команды (кода операции, .хранимого в регистре 4 команд) и номера отказавшего модуля системы. Признак отказа i-ro модуля системы с входов 25.1- 25.(п-I) поступает на S-вход триггеров 15.2-15.п соответствующих определенному модулю, Дпя каждого кода операции вместо отказавшего модуля может быть передано управление на другой определенный модуль системы, в котором хранится дубль нужной микропрограммы или укороченная микропрограмма,

I

Функцию управления заменой отказавшего модуля выполняет преобразователь 13 кода, на входы которого поступает признак того, что модуль, которому необходимо передать управление, отказал, и код операции. По этой информации преобразователь 13 кода определяет модуль, которому необходимо передать управление вместо ,отказавшего. На одном из выходов преобразователя 13 кода появляется сигнал, определяющий тот номер модуля, которому необходимо передать управление вместо отказавшего. Этот сигнал поступает на соответствующий коммутатор 10,1-10,(п-1) и по признаку конца команды адрес передается на один из выходов устройства.

После прихода от другого модуля системы по одному из входов 25.1- 15,(п-1) адреса, с которого необходимо начать работу (выдачу микрокоманд) , он через блок 18 элементов ИЛИ поступает на информационный вход коммутатора 9 адреса и на элемент ИЛИ 19, На выходе элемента ИЛИ 19 появляется сигнал, который перебрасывает триггер 14 пуска в единичное состояние и тем самым запускает генератор 16 тактовых импульсов. Первым тактовым импульсом с входа генер ато- ра 16 информация через коммутатор 9 адреса заносится в регистр 2, По этому адресу происходит считывание информации из запоминающего блока 1, Далее устройство работает аналогично рассмотренному ранее.

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти, регистр адреса, регистр микрокоманд.

с 10 t5

0

25

30

«

5

5

0

5

регистр команд, блок контроля на четность, дешифратор, мультиплексор логических условий, коммутатор адреса, блок коммутаторов, преобразователь кода отказа в код номера модуля, триггер пуска, группу триггеров отказов, генератор тактовых импульсов, первую группу элементов И, блок элементов ШШ, . первый элемент ИЛИ, второй элемент ИЛИ, третий элемент ИЛИ, одновибратор, причем выход коммутатора адреса соединен с информационным входом регистра адреса,выход по- ля адреса которого соединен с адресным входом блока памяти, выход поля кода логических условий регистра микрокоманд соединен с управляюошм входо г мультиплексора логических условий и входом дешифратора, выход поля модифицируемого разряда адреса регистра микрокоманд соединен с вым информационным входом мультиплексора логических условий, выходы поля немодифицируемь1х разрядов адреса регистра микрокоманд соединены с первым информационным входом коммутатора адреса и группой информационных входов блока коммутаторов, выходы дешифратора соединены с первой группой управляющих входов блока коммутаторов и с первыми входами элементов И первой группы, выходы блока коммутаторов являются информационными выходами устройства, выход мультиплексора логических условий соединен - с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса и входом немодифИ цируемого разряда адреса группы информационных входов блока коммутаторов, выход поля кода логических условий, выходы поля немодифицируемых разрядов адреса и выход поля микроопераций регистра микрокоманд соединены с первым входом блока контроля на четность, выход поля контрольного признака четности регистра микрокоманд соединен с вторым входом блока контроля на четность, выход поля адреса регистра адреса соединен с третьим входом блока контроля на четность, выход поля контрольного признака четности регистра адреса соединен с четвертым входом блока на четность, вход кода операции устройства соединен с информационным входом регистра команд и входом блока элементов ИЛИ, входы адреса уст9 .13

ройства соединены с группой входов / блока элементов ИЛИ, выход которого соединен с вторым информационным входом коммутатора адреса, вход пуска устройства соединен с входом первого элемента ИГГИ, выход блока элементов ИЛИ соединен с группой входов первого элемента ИЛИ, выход которого соединен с S-входом триггера пуска, прямой и инверсный выходы триггера пуска соединены соответственно с первым и вторым входами генератора тактовых импульсов, выход которого соединен с входами синхронизации регистра адреса, регистра команд, регистра микрокоманд, первого триггера отказа группы прямой выход триггера пуска соединен с первым управляющим входом коммутатора адреса, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, прямой выход первого триггера отказа группы соединен с выходом отказа устройства и пер- вым входом второго элемента ИЛИ, выход которого соединен с R-входом триггера пуска, входы отказа устройства соединены с S-входами соответствующих триггеров отказа группы, начиная с второго, прямые выходы которых соединены с вторыми входами соответствующих элементов И первой группы, выходы элементов И первой группы соединены с первой группой входов преобразователя кода отказа в код номера модуля, выходы регистра команд соединены с второй группой входов.преобразователя кода отказа в код номера модуля, выходы которого соединены с второй группой управляющих входов блока коммутаторов и входами третьего элемента ИЛИ, выход которого соединен с третьей группой управляющих входов блока коммутато- ров, выход поля признака конца команды регистра микрокоманд соединен с четвертой группой управляющих входов блока коммутаторов, разрешающим входом дешифратора и входом одновиб- ратора, выход которого соединен с вторым входом второго элемента ИЛИ, отличающееся тем, что, с целью повышения надежности за счет устранения влияния сбоев на работу и блокировки выдачи искаженной микрокоманды в операционное устройство, в устройство введены блок анализа,

1810

вторая группа элементов И, третья группа элементов И, четвертый элемент ИЛИ, причем выход ошибки блока контроля на четность соединен с первым входом блока анализа, выход ошибки в операционном коде блока контроля на четность соединен с вторым входом блока анализа, выход ошибки в адресном коде блока контроля на четность соединен с третьим входом блока анализа, четвертый вход блока анализа соединен с выходом генерато ра тактовых импульсов, выход признака отказа блока анализа соединен с D-ВХОДОМ первого триггера отказа . группы, выход блокировки микрокоманды блока анализа соединен с первыми входами элементов И второй группы, выходы блока памяти соединены с вторыми входами элементов И второй группы, выходы элементов И которой соединены с информационными входами регистра микрокоманд, выход блокировки адреса блока анализа соединен с первыми входами элементов И третьей группы, выходы поля микроопераций регистра микрокоманд соединены с вторыми входами элементов И третьей группы, выходы элементов И которой образуют управляющий выход устройства, выход блокировки адреса блока анализа соединен с прямым входом четвертого элемента ИЛИ, выход поля конца команды регистра микрокоманд соединен с входом последнего элемента. И третьей группы с инверсным входом четвертого элемента ИЛИ, выход которого соединен с вторым управляющим входом коммутатора адреса, причем блок анализа содержит триггер ошибки в операционной информации, триггер ошибки в адресной информации элемент задержки и элемент И блока, анализа, выход которого является выходом признака отказа блока анализа, первый вход блока анализа подключен к первому входу элемента И блока анализа и через элемент задержки к второму входу элемента И блока анализа, второй вход блока анализа подключен к S-входу триггера ошибки в операционной информации инверсный выход которого является выходом блокировки адреса блока анализа, третий вход блока анализа подключен к S-ВХОДУ триггера ошибки в адресной информадии, инверсный выход которого является выходом блокировки микрокоманды анализа, четвертый вход блока анализа подключен к R-входам.

13I08I8

триггеров ошибок в операционной информации ив адресной информации.

Л/г

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения реконфигурируемых управляющих и вычислительных систем с использованием ffloжecтвa однотипных микропрограммных устройств управления. Целью изобретения является повышение на дежностй функционирования устройства за счет устранения влияния сбоев на его работу и блокировки выдачи искаженной микрокоманды в операцион;Ное устройство. Устройство позволяет: вьшолнить такт, в котором зафиксиро-; вана ошибка. Если это был сбой, устройство продолжает работу, если же произошел отказ - устройство прекращает функционирование, При искажении операционного кода блок анализа формирует сигнал, запрещающий выдачу микрокоманды в операционное устрой- ство. (Л эо 30

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1986-02-11—Подача