1

Изобретение относится к импульсной технике и может быть испольгювано в цифровых логических схемах.

Цель изобретения - увеличение быстродействия и уменьшение потребляемой мощности.

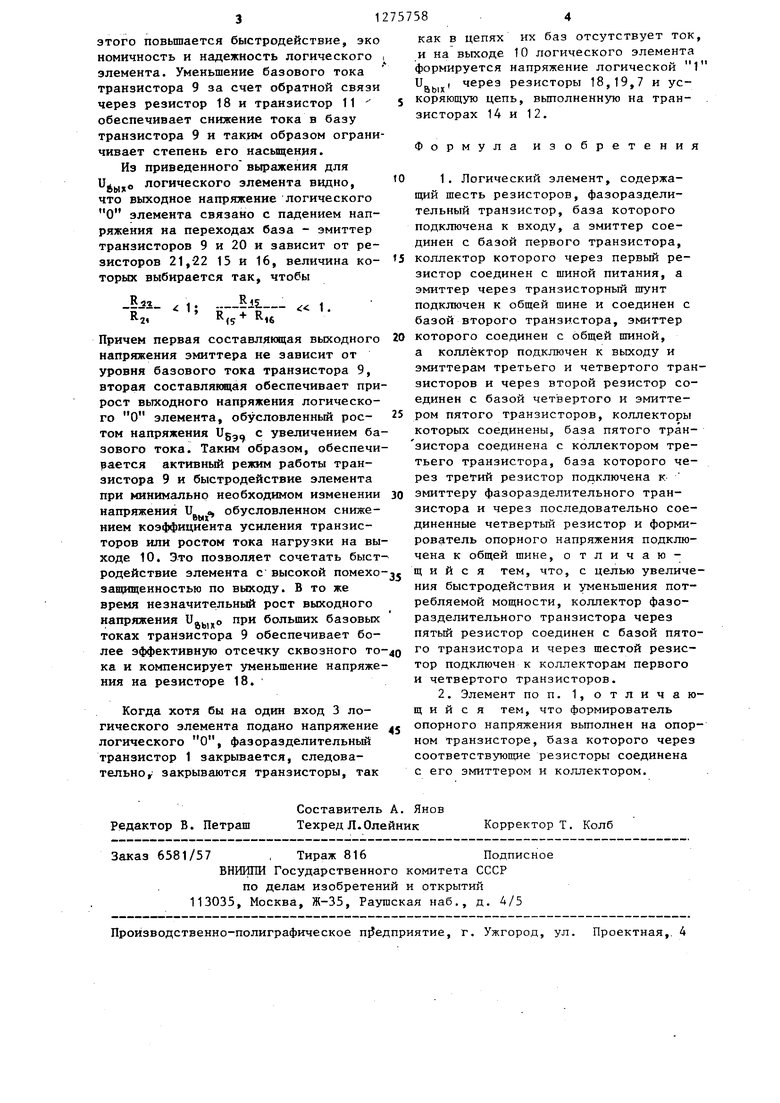

На чертеже представлена принципиальная электрическая схема логического элемента.

Логический элемент содержит фазоразделительный транзистор 1 база которого через входной многоэмиттерньй транзистор 2 подключена к входам 3, при этом эмиттеры транзистора 2 подключены к входам 3, база через резистор 4 соединена с шиной 5 питания и подключена к его коллектору и базе транзистора 1, эмиттер которого соединен с базой первого транзистора 6, коллектор которого через первый резистор 7 соединен с шиной 5 питания, а эмиттер через транзисторный шунт 8 соединен с общей шиной и подключен к базе второго транзистора 9. Эмиттер транзистора 9 соединен с общей шиной, а коллектор подключен к выходу 10 иэмиттерам третьего 11 и четвертого 12 транзисторов 11 и 12 и через второй резистор 13 соединен с базой четвертого 12 и эмиттером пятого 14 транзисторов, коллекторы которых соединены. База пятого транзистора 14 соединена с коллектором третьего транзистора 11, база которого подключена через третий резистор 15 к эмиттеру транзистора 1 и через последовательно соединенные четвертый резистор 16 и формирователь 17 опорного напряжения к общей шине. Коллектор транзистора 1 через пятый резистор 18 соединен с базой пятого транзистора 14 и через шестой резистор 19 подключен к коллекторам первого 6 и четвертого 12 транзисторов

Формирователь 17 опорного напряжения вьшолнен на опорном транзисторе 20, база которого через соответствуюшде резисторы 21 и 22 соединена с его эмиттером и коллектором. Транзисторный шунт 8 выполнен на шунтирующем транзисторе 23, змиттер которого подключен к общей шине, а коллектор и база через соответству1 ш1;ие резисторы 24 и 25 соединена с эмиттером транзистора 1.

Логический элемент работает следующим образом.

75758-«

При подале высокого уровня напряжения логической 1 на все входы логического элемента эмиттерные переходы транзистора 2 закрыты. Ток чеS рез резистор 4, закоротку между переходом база - коллектор транзистора 2 поступает в базу фазораспределительного транзистора 1 и открывает его. Эмиттерньй ток транзистора 1

10 течет в цепь из резисторов 15 и 16 ; и формирователь 17 опорного напряжения, а также в базу транзистора 6,

Быстрое включение транзистора 6, а следовательно, транзистора 9 обес5 печивается высоким уровнем базовых токов транзисторов 9 и 6, уровень которых определяется резисторами 19 и 7. Увеличению быстродействия логического элемента способствует тран20 зисторный шунт 8, включающийся и выключающийся с замедлением, определяемым соотношением резисторов 24 и 25, по сравнению с включением и выключением выходного тразистора 9.

При достижении на выходе 10 напряжения

Rie

Rji.u

9 Rjs R,c

R

71

где IL , падение напряжения на

переходах база - эмиттер транзисторов 20 и 9

R ,R| ,R2,, сопротивления резисторов 15,16,21 и 22,

открывается транзистор 11 и избыточная часть базового тока транзистора 6, задаваемого резисторами 19 и 7, отводится через резистор 1В в коллектор транзистора 1, При этом внутренняя помехозащищенность логического элемента улучшается за счет падения )напряжения на резисторах 18 и 7, так как более эффективно блокируется переход база. - эмиттер транзистора

14 и уменьшается уровень сквозного тока через транзистор 12.

Так как резистор 7 является общим резистором в коллекторных цепях (элементом обратной связи) транзисторов 1,,1Ги 12, наличие тока через один из транзисторов способствует уменьшению тока через другой. При этом исключается возможность насыщения и потери быстродействия транзистора 6, а .также возможность протекания значительных сквозных токов через транзисторы 14 и 12 при открытых транзисторах 6 и 11. В результате

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Трехкаскадный ТТЛШ-вентиль | 1988 |

|

SU1598158A1 |

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Формирователь импульсов (его варианты) | 1980 |

|

SU974562A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых логических схемах. Цель изобретения - повышение быстродействия и уменьшение потребляемой мощности. Устройство содержит фазоразделительный транзистор 1, много змиттерный транзистор 2, формирователь 17 опорного напряжения, -транзисторы 6, 9, 11, 14, резисторы 4, 15, 16, 19. Для достижения поставленной цели в устройство введены транзистор 12, транзисторный шунт 8, резисторы 7, 13, 18. 1 з. п.ф-лы,1 ил. (Л 01 сл оо

| Логический элемент | 1982 |

|

SU1058061A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-07—Публикация

1985-08-30—Подача