1

Изобретение относится к импульсно технике и может быть использовано для построения интегральных логических схем.

Цель изобретения - увеличение надежности работы интегральной логической схемы путем уменьшения сквоз- ных токов,, а также увеличение быстродействия.

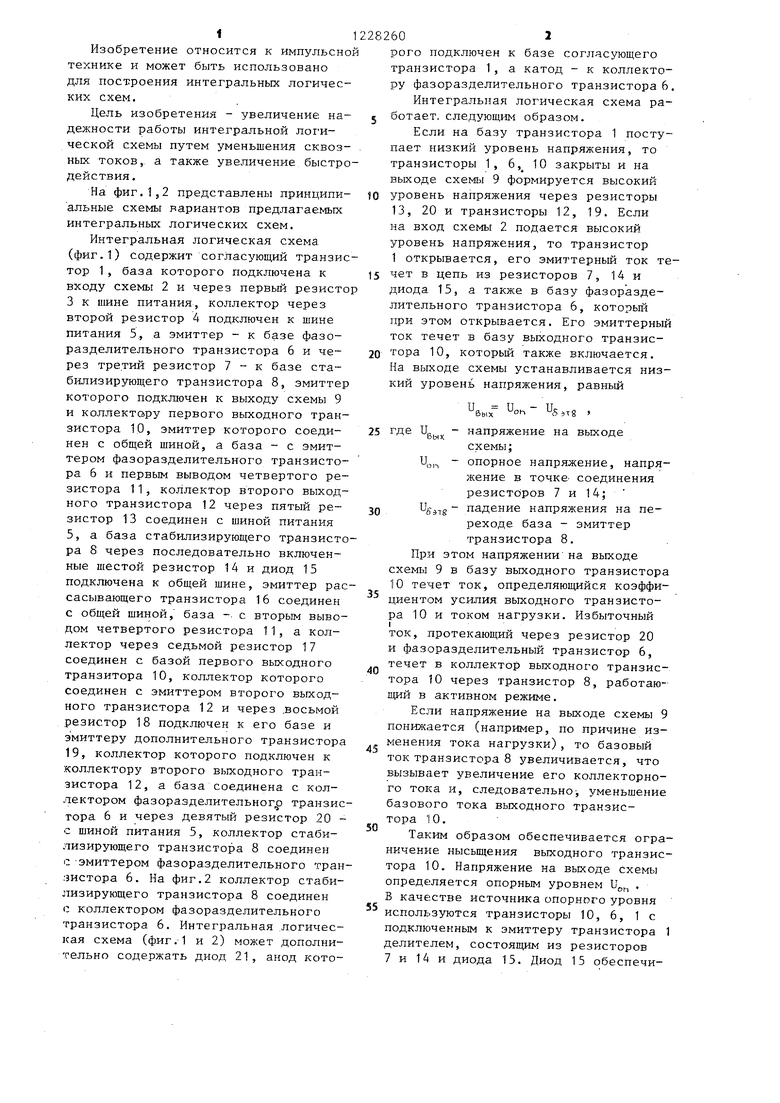

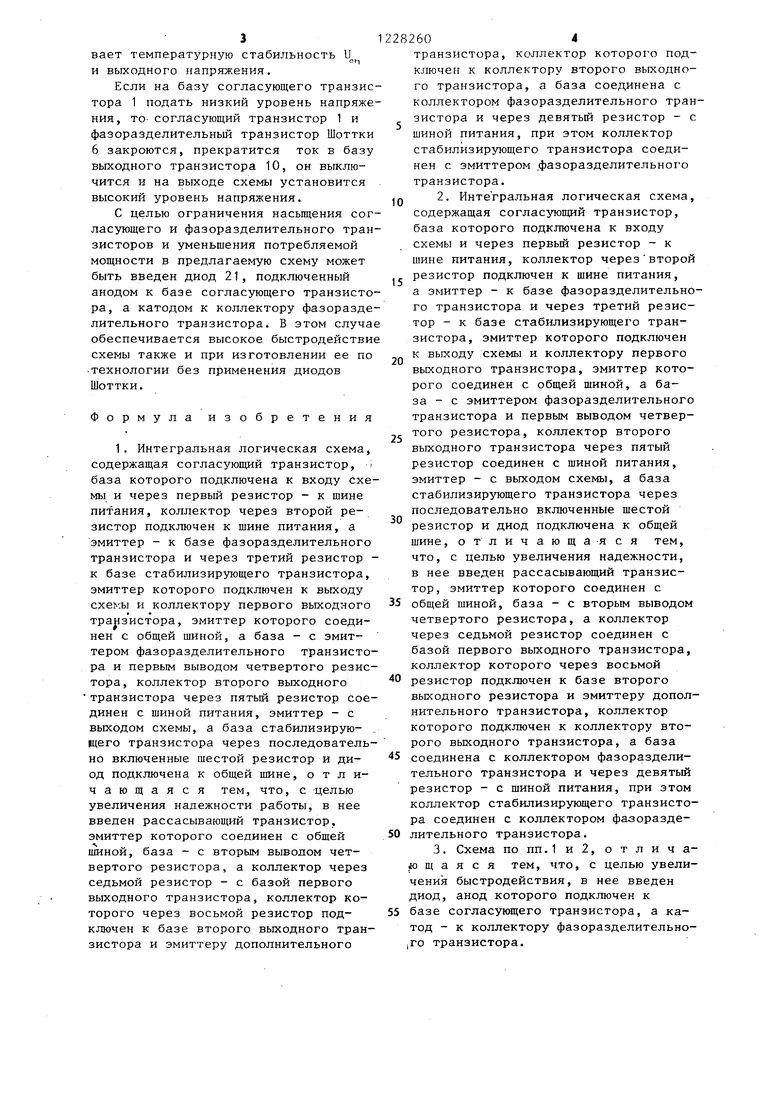

На фиг.1,2 представлены принципиальные схемы вариантов предлагаемых интегральных логических схем.

Интегральная логическая схема. (фиг.1) содержит согласующий транзистор 1, база которого подключена к входу схемы 2 и через первый резисто 3 к шине питания, коллектор через второй резистор 4 подключен к шине питания 5., а эмиттер - к базе фазо- разделительного транзистора 6 и через третий резистор 7 - к базе стабилизирующего транзистора 8, эмиттер которого подключен к выходу схемы 9 и коллектору первого выходного транзистора 10, эмиттер которого соединен с общей шиной, а база - с эмиттером фазоразделительного транзистора 6 и первым выводом четвертого резистора 11, коллектор второго выходного транзистора 12 через пятый резистор 13 соединен с шиной питания 5, а база стабилизирующего транзистора 8 через последовательно включенные шестой резистор 14 и диод 15 подключена к общей шине, эмиттер рассасывающего транзистора 16 соединен с общей шиной, база - с вторым выводом четвертого резистора 11, а коллектор через седьмой резистор 17 соединен с базой первого выходного транзитора 10, коллектор которого соединен с эмиттером второго выходного транзистора 12 и через .восьмой резистор 18 подключен к его базе и эмиттеру дополнительного транзистора 19, коллектор которого подключен к коллектору второго выходного транзистора 12, а база соединена с коллектором фазоразделительног транзистора 6 и через девятый резистор 20 - с шиной питания 5, коллектор стабилизирующего транзистора 8 соединен с-эмиттером фазоразделительного транзистора 6. На фиг.2 коллектор стабилизирующего транзистора 8 соединен с коллектором фазоразделительного транзистора 6. Интегральная логическая схема (фиг.-1 и 2) может дополнительно содержать диод 21, анод кото82602

рого подключен к базе согласующего транзистора 1, а катод - к коллектору фазоразделительного транзистора 6. Интегральная логическая схема ра

ботает, следующим образом.

Если на базу транзистора 1 поступает низкий уровень напряжения, то транзисторы 1, 6, 10 закрыты и на выходе схемы 9 формируется высокий

0 уровень напряжения через резисторы 13, 20 и транзисторы 12, 19. Если на вход схемы 2 подается высокий уровень напряжения, то транзистор 1 открывается, его эмиттерный ток те5 чет в цепь из резисторов 7, 14 и диода 15, а также в базу фазоразделительного транзистора 6, которьш при этом открывается. Его эмиттерный ток течет в базу выходного транзис0 тора 10, который также включается. На выходе схемы устанавливается низкий уровень напряжения, равный

Ue,, и..- Us,,8 ,

5 где Ug - напряжение на выходе

схемы;

Ц,, - опорное напряжение, напря- л ;ение в точке соединения резисторов 7 и 14;

30 падение напряжения на переходе база - эмиттер транзистора 8.

При этом напряжении на выходе схемы 9 в базу выходного транзистора 10 течет ток, определяющийся коэффициентом усилия выходного транзистора 10 и током нагрузки. Избыточный г ток, протекающий через резистор 20

и фазоразделительный транзистор 6, течет в коллектор выходного транзистора 10 через транзистор 8, работающий в активном режиме.

Если напряжение на выходе схемы 9 понижается (например, по причине изменения тока нагрузки), то базовый ток транзистора 8 увеличивается, что вызывает увеличение его коллекторного тока и, следовательноj уменьшение базового тока выходного транзистора 10,

Таким образом обеспечивается ограничение ныcьш eния выходного транзистора 10, Напряжение на выходе схемы определяется опорным уровнем U, , В качестве источника опорного уровня используются транзисторы 10, 6, 1 с подключенным к эмиттеру транзистора 1 делителем, состоящим из резисторов 7 и 14 и диода 15, Диод 15 обеспечи35

40

43

50

3

вает температурную стабильность IJ, и выходного напряжения.

Если на базу согласующего транзистора 1 подать низкий уровень напряжения, то- согласующий транзистор 1 и фазоразделительный транзистор Шоттки 6 закроются, прекратится ток в базу выходного транзистора 10, он выключится и на выходе схемы установится высокий уровень напряжения.

С целью ограничения насыщения согласующего и фазоразделительного транзисторов и уменьшения потребляемой мощности в предлагаемую схему может быть введен диод 21, подключенный анодом к базе согласующего транзистора, а катодом к коллектору фазоразделительного транзистора. В этом случа обеспечивается высокое быстродействи схемы также и при изготовлении ее по технологии без применения диодов Шоттки.

Формула изобретения

1. Интегральная логическая схема, содержащая согласующий транзистор, база которого подключена к входу схемы и через первый резистор - к шине питания, коллектор через второй резистор подключен к шине питания, а эмиттер - к базе фазоразделительного транзистора и через третий резистор - к базе стабилизирующего транзистора, эмиттер которого подключен к выходу схемы и коллектору первого выходного транзистора, эмиттер которого соединен с общей шиной, а база - с эмиттером фазоразделительного транзистора и первым выводом четвертого резистора, коллектор второго выходного транзистора через пятый резистор соединен с щиной питания, эмиттер - с выходом схемы, а база стабилизирующего транзистора через последовательно включенные шестой резистор и диод подключена к общей шине, отличающаяся тем, что, с -целью увеличения надежности работы, в нее введен рассасывающий транзистор, эмиттер которого соединен с общей ишной, база - с вторым выводом четвертого резистора, а коллектор через седьмой резистор - с базой первого выходного транзистора, коллектор которого через восьмой резистор подключен к базе второго выходного транзистора и эмиттеру дополнительного

0

282604

транзистора, коллектор которого подключен к коллектору второго выходного транзистора, а база соединена с коллектором фазоразделительного транзистора и через девятый резистор - с шиной питания, при этом коллектор стабилизирующего транзистора соединен с эмиттером .фазоразделительного транзистора.

JQ 2. Интегральная логическая схема, содержащая согласующий транзистор, база которого подключена к входу схемы и через первый резистор - к шине питания, коллектор через второй резистор подключен к щине питания, а эмиттер - к базе фазоразделительного транзистора и через третий резистор - к базе стабилизирующего транзистора, эмиттер которого подключен к выходу схемы и коллектору первого выходного транзистора, эмиттер которого соединен с общей шиной, а база - с эмиттером фазоразделительного транзистора и первым выводом четвертого резистора, коллектор второго выходного транзистора через пятый резистор соединен с шиной питания, эмиттер - с выходом схемы, а база стабилизирующего транзистора через последовательно включенные шестой резистор и диод подключена к общей шине, отличающая ся тем, что, с целью увеличения надежности, в нее введен рассасывающий транзистор, эмиттер которого соединен с

5 общей шиной, база - с вторым выводом четвертого резистора, а коллектор через седьмой резистор соединен с базой первого выходного транзистора, коллектор которого через восьмой

0 резистор подключен к базе второго

выходного резистора и эмиттеру дополнительного транзистора, коллектор которого подключен к коллектору второго выходного транзистора, а база

5 соединена с коллектором фазоразделительного транзистора и через девятый резистор - с шиной питания, при этом коллектор стабилизирующего транзистора соединен с коллектором фазоразде0 лительного транзистора.

3. Схема по пп.1 и 2, отличающаяся тем, что, с целью увеличения быстродействия, в нее введен диод, анод которого подключен к

5 базе согласукнцего транзистора, а катод - к коллектору фазоразделительно- ,го транзистора.

0

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| ТТЛ-элемент | 1985 |

|

SU1274150A1 |

| Логический элемент | 1985 |

|

SU1275758A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

Изобретение относится к импульсной технике. Цель изобретения - увеличение надежности работы интегральной логической схемы. Устройство содержит согласующий транзистор 1, резисторы 3,4,7,11,14,17,18 и 20, шину питания 5, фазоразделительный транзистор 6, стабилизирующий транзистор 8, вход 2 и выход 9 схемы, выходные транзисторы 10 и 12, диод 15, рассасывающий транзистор 16, дополнительный транзистор 19 и диод 21. Введение диода 21 ограничивает насыщение согласующего 1 и фазораздели- тельного 6 транзисторов и уменьшает потребляемую мощность. Введение рассасывающего транзистора 16 и образование новых связей между элементами устройства позволяет уменьшить сквозные токи и увеличить быстродействие устройства. 2 с.и 1 з.п. ф-лы, 2 ил. § (Л

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-30—Публикация

1984-01-05—Подача