Изобретение относится к импульсной технике, а именно к микросхемотехнике транзисторно-транзисторных логических элементов.

, Целью изобретения является уменьшение средней потребляемой мощности путем устранения сквозных токов при переключении схемы.

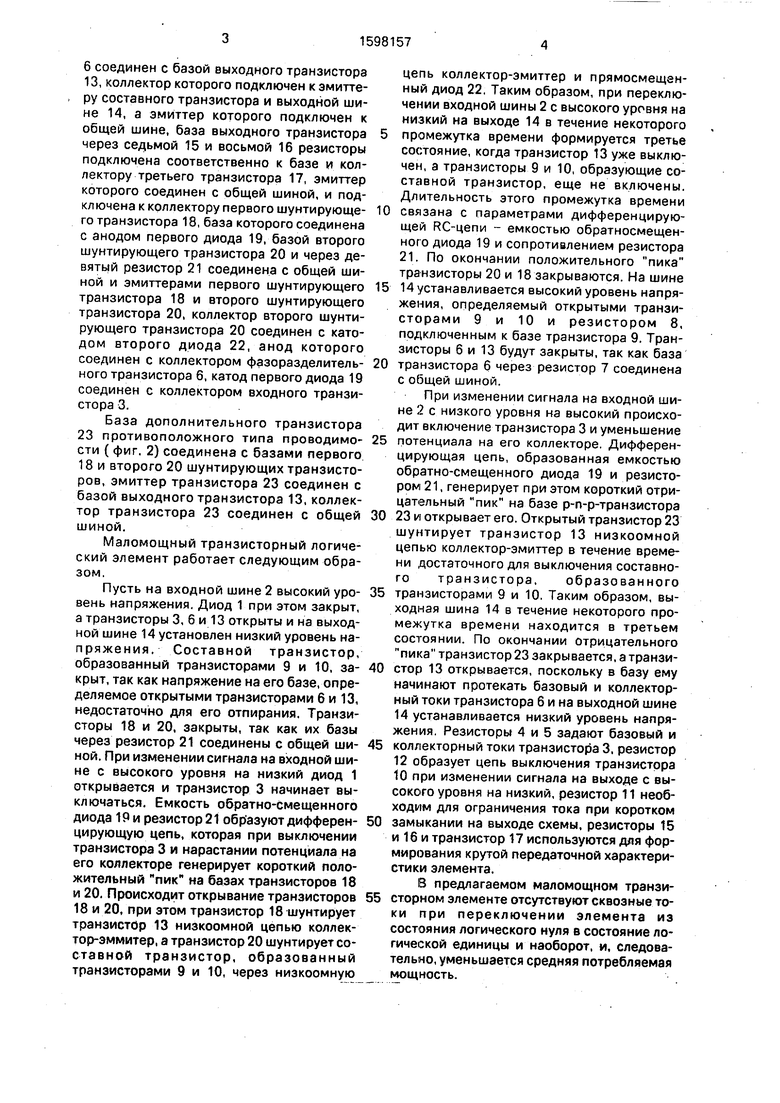

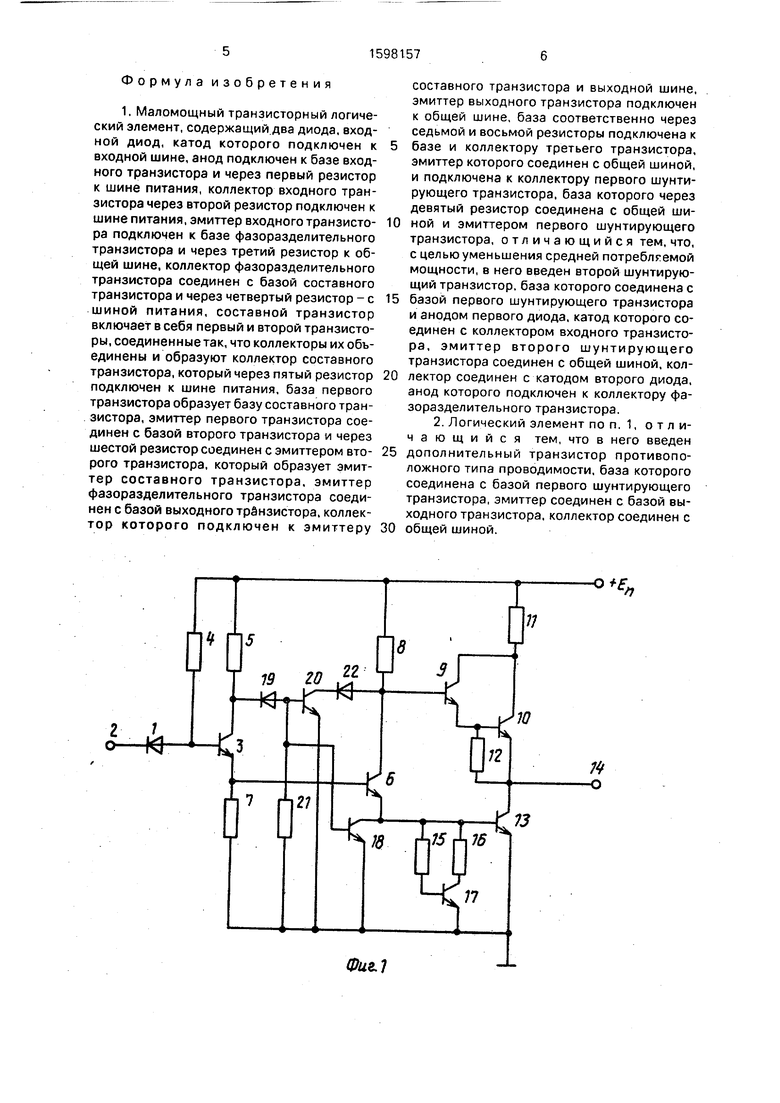

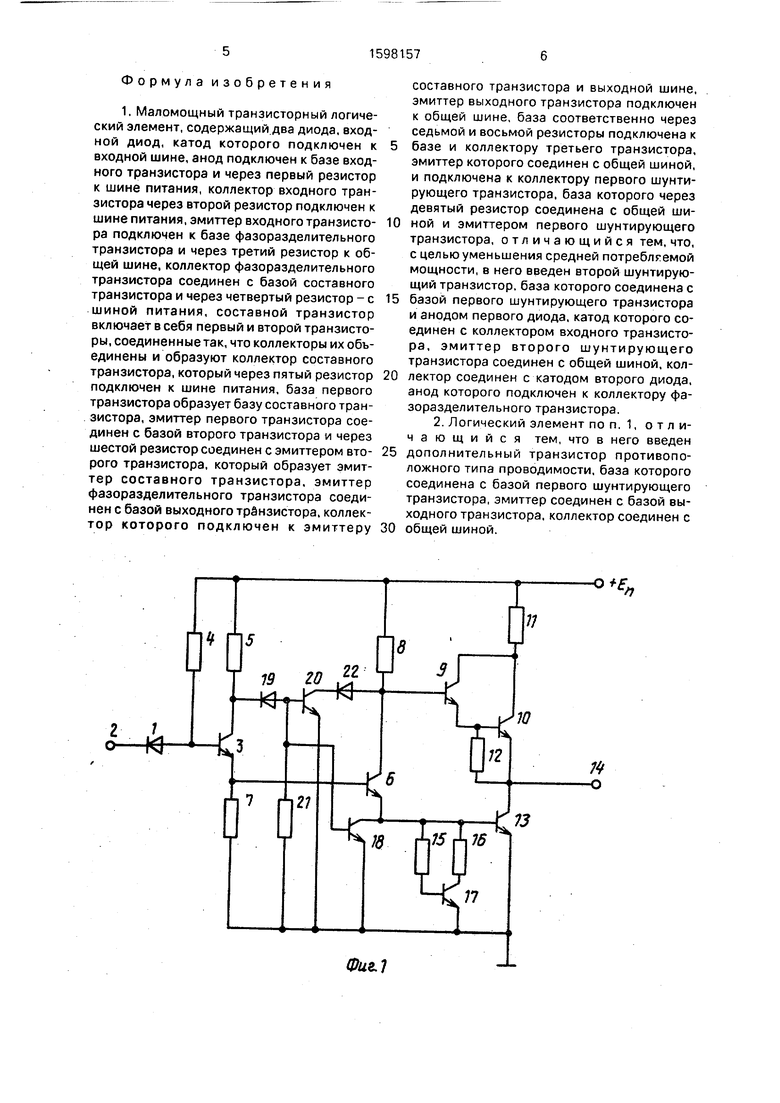

На фиг, 1 и 2 представлены электрические принципиальные схемы маломощного транзисторногс логического элемента.

Маломощный транзисторный логический элемент (фиг. 1) содержит входной диод 1, катод которого подключен к входной шине 2, анод подключен к базе входного транзистора 3 и через первый резистор 4 к шине питания +Еп, коллектор входного транзистора 3 через второй резистор 5 соединен с шиной питания +Еп, эмиттер входного транзистора 3 подключен к базе фазо- разделительного транзистора 6 и через третий резистор 7 к общей шине, коллектор фазоразделительного транзистора 6 соединен с базой составного транзистора и через четвертый резистор 8 - с шиной питания +ЕП. Составной транзистор включает в себя первый 9 и второй 10 транзисторы, соединенные так, что коллекторы их объединены и образуют коллектор составного транзистора, который через пятый резистор 11 соединен с шиной питания +Еп. база первого транзистора 9 образует базу составного транзистора, эмиттер первого транзистора 9 соединен с базой второго транзистора 10 и через шестой резистор 12 соединен с эмиттером второго транзистора 10, который образует эмиттер составного транзистора, эмиттер фазоразделительного транзистора

сл ю сх

сл VI

6 соединен с базой выходного транзистора 13, коллектор которого подключен к эмиттеру составного транзистора и выходной шине 14, а эмиттер которого подключен к общей шине, база выходного транзистора через седьмой 15 и восьмой 16 резисторы подключена соответственно к базе и коллектору третьего транзистора 17, эмиттер которого соединен с общей шиной, и подключена к коллектору первого шунтирующего транзистора 18, база которого соединена с анодом первого диода 19, базой второго шунтирующего транзистора 20 и через де- вять1й резистор 21 соединена с общей шиной и эмиттерами первого шунтирующего транзистора 18 и второго шунтирующего транзистора 20, коллектор второго шунтирующего транзистора 20 соединен с катодом второго диода 22, анод которого соединен с коллектором фазоразделитель- ного транзистора 6, катод первого диода 19 соединен с коллектором входного транзистора 3.

База дополнительного транзистора 23 противоположного типа проводимости ( фиг. 2) соединена с базами первого 18 и второго 20 шунтирующих транзисторов, эмиттер транзистора 23 соединен с базой выходного транзистора 13. коллектор транзистора 23 соединен с общей шиной.

Маломощный транзисторный логический элемент работает следующим образом.

Пусть на входной шине 2 высокий уровень напряжения. Диод 1 при этом закрыт, а транзисторы 3. 6 и 13 открыты и на выходной шине 14 установлен низкий уровень напряжения. Составной транзистор, образованный транзисторами 9 и 10, закрыт, так как напряжение на его базе, определяемое открытыми транзисторами 6 и 13, недостаточно для его отпирания. Транзисторы 18 и 20. закрыты, так как их базы через резистор 21 соединены с общей шиной. При изменении сигнала на входной шине с высокого уровня на низкий диод 1 открывается и транзистор 3 начинает выключаться. Емкость обратно-смещенного диода 19 и резистор 21 обр азуют дифференцирующую цепь, которая при выключении транзистора 3 и нарастании потенциала на его коллекторе генерирует короткий положительный пик на базах транзисторов 18 и 20. Происходит открывание транзисторов 18 и 20, при этом транзистор 18 шунтирует транзистор 13 низкоомной цепью коллек- тор-эммитер, а транзистор 20 шунтирует со- ставной транзистор, образованный транзисторами 9 и 10, через низкоомную

цепь коллектор-эмиттер и прямосмещен- ный диод 22. Таким образом, при переключении входной шины 2 с высокого уровня на низкий на выходе 14 в течение некоторого 5 промежутка времени формируется третье состояние, когда транзистор 13 уже выключен, а транзисторы 9 и 10, образующие составной транзистор, еще не включены. Длительность этого промежутка времени 10 связана с параметрами дифференцирующей RC-цепи - емкостью обратносмещен- ного диода 19 и сопротивлением резистора 21. По окончании положительного пика транзисторы 20 и 18 закрываются. На шине 15 14 устанавливается высокий уровень напряжения, определяемый открытыми транзисторами 9 и 10 и резистором 8, подключенным к базе транзистора 9. Транзисторы 6 и 13 будут закрыты, так как база 20 транзистора 6 через резистор 7 соединена с общей шиной.

При изменении сигнала на входной шине 2 с низкого уровня на высокий происходит включение транзистора 3 и уменьшение 25 потенциала на его коллекторе. Дифференцирующая цепь, образованная емкостью обратно-смещенного диода 19 и резистором 21, генерирует при этом короткий отрицательный пик на базе р-п-р-транзистора 0 23 и открывает его. Открытый транзистор 23 шунтирует транзистор 13 низкоомной цепью коллектор-эмиттер в течение времени достаточного для выключения составного транзистора. образованного 5 транзисторами 9 и 10. Таким образом, выходная шина 14 в течение некоторого промежутка времени находится в третьем состоянии. По окончании Отрицательного пика транзистор 23 закрывается, а транзи- 0 стор 13 открывается, поскольку в базу ему начинают протекать базовый и коллекторный токи транзистора 6 и на выходной шине 14 устанавливается низкий уровень напряжения. Резисторы 4 и 5 задают базовый и 5 коллекторный токи транзистора 3. резистор 12 образует цепь выключения транзистора 10 при изменении сигнала на выходе с высокого уровня на низкий, резистор 11 необходим для ограничения тока при коротком 0 замыкании на выходе схемы, резисторы 15 и 16 и транзистор 17 используются для формирования крутой передаточной характеристики элемента.

В предлагаемом маломощном транзи- 5 сторном элементе отсутствуют сквозные то- ки при переключении элемента из состояния логического нуля в состояние логической единицы и наоборот, и, следовательно, уменьшается средняя потребляемая мощность.

Формула изобретения

1. Маломощный транзисторный логический элемент, содержащий два диода, входной диод, катод которого подключен к входной шине, анод подключен к базе входного транзистора и через первый резистор к щине питания, коллектор входного транзистора через второй резистор подключен к шине питания, эмиттер входного транзисто- ра подключен к базе фазоразделительного транзистора и через третий резистор к общей шине,коллектор фазоразделительного транзистора соединен с базой составного транзистора и через четвертый резистор - с шиной питания, составной транзистор включает в себя первый и второй транзисторы, соединенные та к, что коллекторы их объединены и образуют коллектор составного транзистора, который через пятый резистор подключен к шине питания, база первого транзистора образует базу составного транзистора, эмиттер первого транзистора соединен с базой второго транзистора и через шестой резистор соединен с эмиттером вто- рого транзистора, который образует эмиттер составного транзистора, эмиттер фазоразделительного транзистора соединен с базой выходного транзистора, коллектор которого подключен к эмиттеру

составного транзистора и выходной шине, эмиттер выходного транзистора подключен к общей шине, база соответственно через седьмой и восьмой резисторы подключена к базе и коллектору третьего транзистора, эмиттер которого соединен с общей шиной, и подключена к коллектору первого шунтирующего транзистора, база которого через девятый резистор соединена с общей шиной и эмиттером первого шунтирующего транзистора, отличающийся тем, что, с целью уменьшения средней потребляемой мощности, в него введен второй шунтирующий транзистор, база которого соединена с базой первого шунтирующего транзистора и анодом первого диода, катод которого соединен с коллектором входного транзистора, эмиттер второго шунтирующего транзистора соединен с общей шиной, коллектор соединен с катодом второго диода, анод которого подключен к коллектору фазоразделительного транзистора.

2. Логический элемент по п. 1, отличающийся тем, что в него введен дополнительный транзистор противоположного типа проводимости, база которого соединена с базой первого шунтирующего транзистора, эмиттер соединен с базой выходного транзистора, коллектор соединен с общей шиной.

Фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| ТТЛШ-вентиль | 1988 |

|

SU1599984A1 |

| Быстродействующий ТТЛШ-вентиль | 1987 |

|

SU1531207A1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| Логический элемент | 1985 |

|

SU1275758A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

Изобретение относится к импульсной технике, а именно к микросхемотехнике транзисторно-транзисторных логический элементов. Цель изобретения - уменьшение средней потребляемой мощности. Маломощный транзисторно-транзисторный логический элемент содержит девять резисторов, два диода, входной диод, входной транзистор, фазоразделительный транзистор, составной транзистор на первом и втором транзисторах, выходной транзистор, третий транзистор и первый и второй шунтирующие транзисторы, а также дополнительный транзистор противоположного типа проводимости. Введение второго шунтирующего транзистора, а также дополнительного транзистора противоположного типа проводимости позволяет уменьшить среднюю потребляемую мощность за счет исключения сквозных токов при переключении элемента из состояния логического "0" в состояние логической "1" и наоборот. 1 з.п.ф-лы, 2 ил.

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника.-М.: Радио и связь, 1982, с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Патент США № 4330723, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-07—Публикация

1988-10-27—Подача