е

1 3

СЛ

ND

ш

ND

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

Изобретение относится к вычислительной технике и может использоваться для контроля и диагностирования дискретных объектов. Цель изобретения - расширение функциональных возможностей. Устройство содержит два мультиплексора 2 и 8, блок 3 синхронизации, блок 4 оперативной памяти, формирователь 5 сигнатур, блок 6 индикации, блок 7 управления. Устройство позволяет контролировать разнотипные цифровые блоки с произвольным числом входов и выходов. 1 з.п. ф-лы, 3 ил.

Фиг.1

3

Изобретение относится к цифровой вьтислительной технике и может быть использовано .для проверки работоспособности и поиска дефектов в цифров аппаратуре.

Цель изобретения - расширение функциональных возможностей устройсва за счет контроля логических схем с произвольным числом входов и выходов о

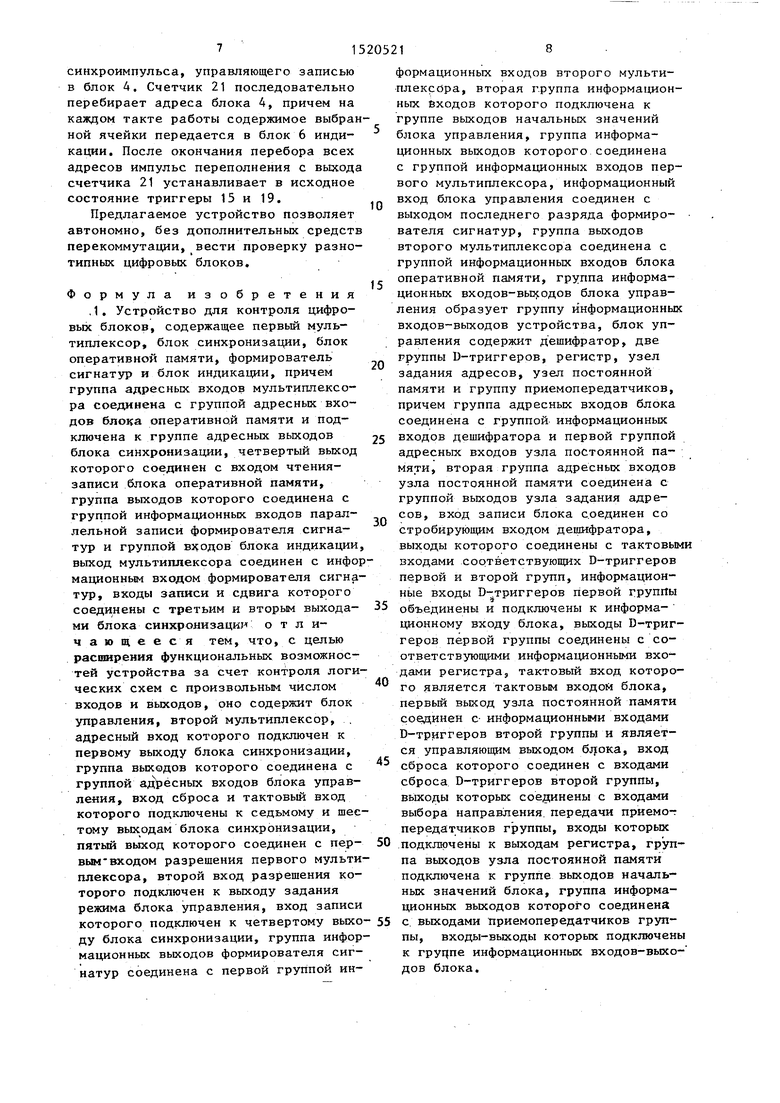

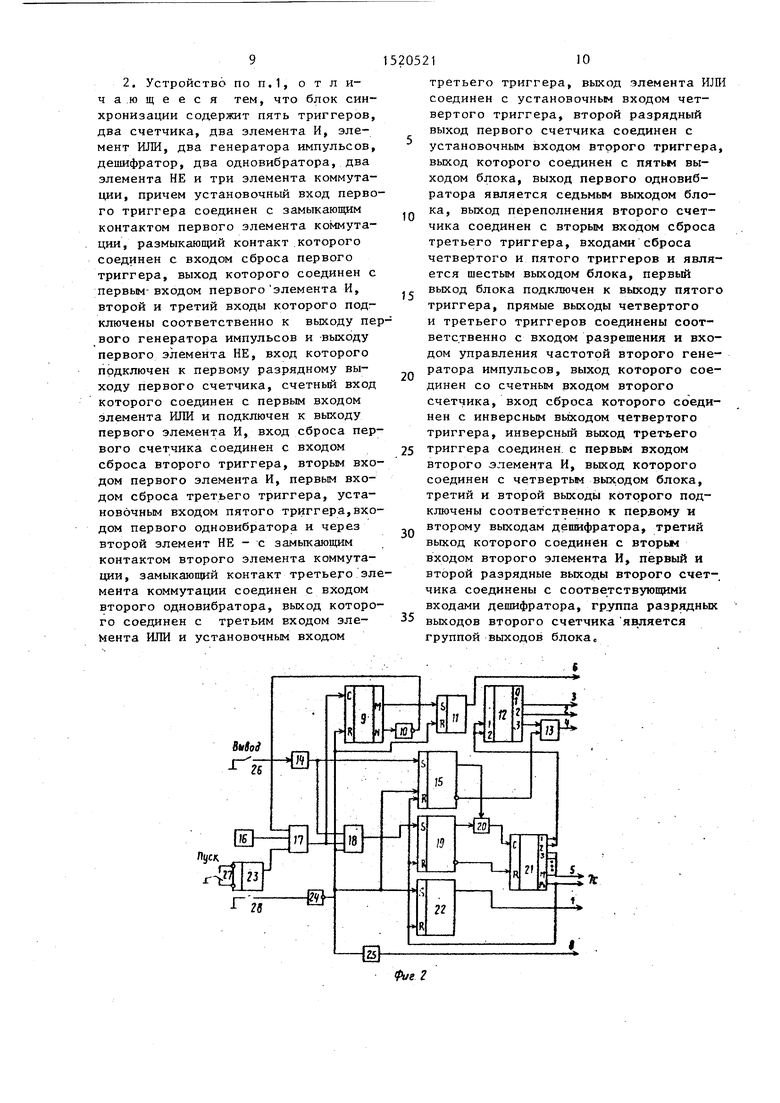

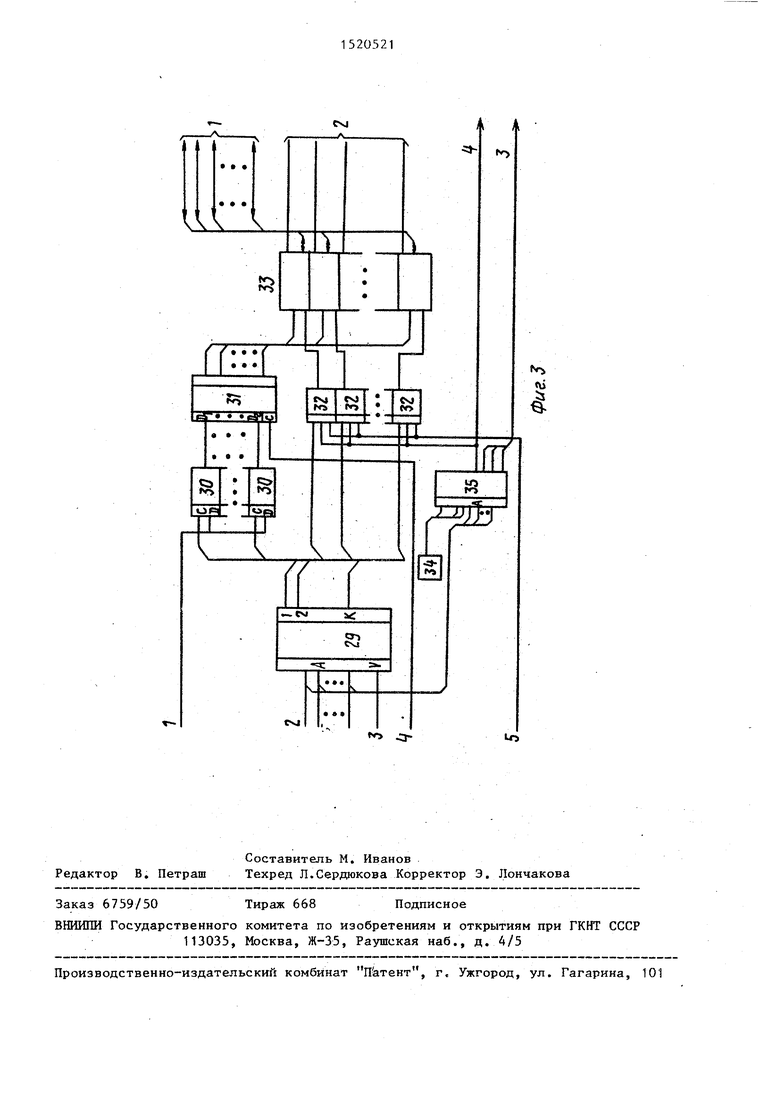

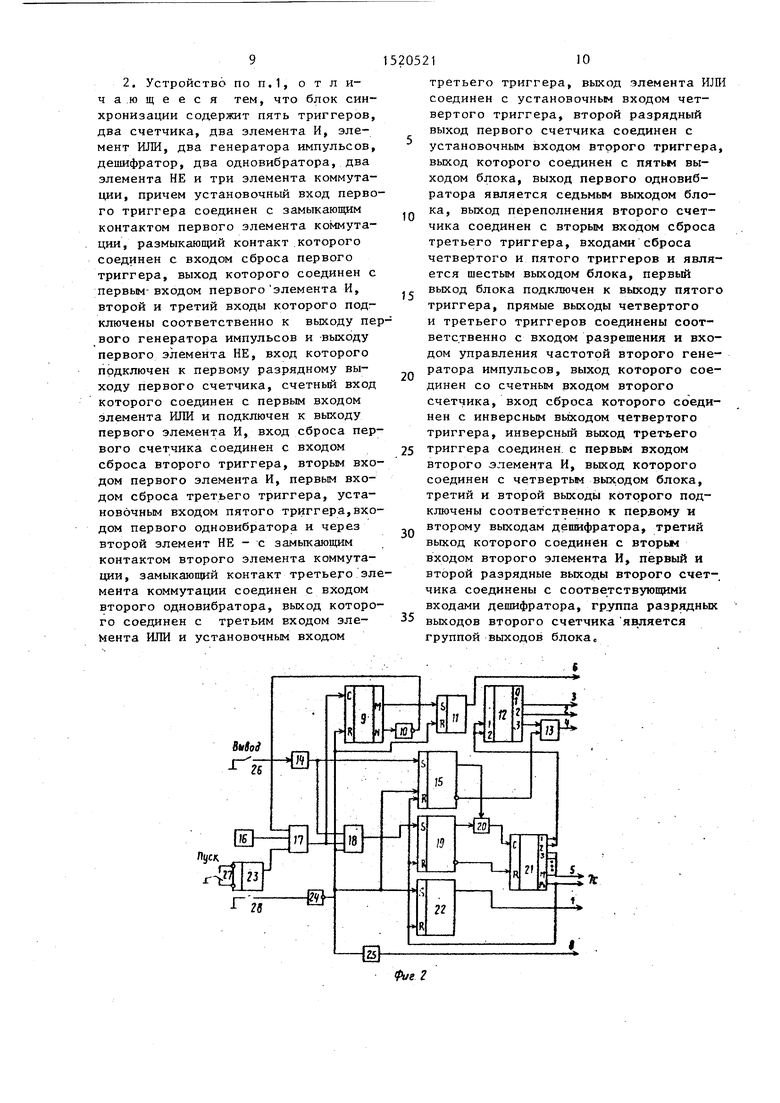

На фиг.1 приведена структурная схема устройства для контроля цифровых блоков; на фиг.2 - функциональная схема блока синхронизации; на фиг.3 - функциональная схема блока управления.

Устройство для контроля цифровых блоков 1 содержит первый мультиплексор 2, блок 3 синхронизации, блок 4 оперативной памяти, формирователь 5 сигнатур, блок 6 индикации,, блок 7 управления, второй мультиплексор 8.

Блок 3 синхронизации содержит счетчик 9, элемент НЕ 10, первьш триггер 11, дешифратор 12, элемент И 13, одновибратор 14, триггер 15, генератор 16 импульсов, элемент И 1 элемент ИЛИ 18, триггер 19, генератор 20 импульсов, счетчик 21,триггеры 22 и 23, элемент НЕ 24, одно- вибратор 25, элементы-26-28 коммутации.

Блок 4 предназначен для временно хранения текущих значений сигнатур или псевдослучайных кодов. Емкость блока 4 равна числу информационных контактов объекта контроля, а разряность слова - разрядности формирователя 5 сигнатур. Последний представ

ляет собой регистр сдвига с обратнь

связями, осуществляющий деление входной последовательности на образующий полином и имеющий дополнительные информационные и управляющие входы параллельной записи. Разрядность регистра и структура обратных связей определяются видом образующего полинома и выбираются исходя из.требований к достоверности обнаружения ошибок в контролируемых последователь- нoctяx.

В качестве блока 6 индикации может быть использовано печатающее устройство, алфавитно-цифровой дисплей или панель индикации.

Блок 7 управления предназначен для выбора направления передачи информации по каждому из контактов прове0

5

0

5

0

5

ряемого блока 1, хранения информации о начальных состояниях блока 4 и выдачи управляющих воздействий на первый мультиплексор 2.

Блок 7 (фиг.3) содержит дешифратор 29 выбора контактов,, триггеры 30 по числу контактов проверяемого блока 1, регистр 31, триггеры 32 по числу контактов проверяемого блока, двунаправленные элементы 33 по числу контактов проверяемого блока, узел 34 задания адресов и узел 35 постоянной памяти.

Мультиплексор 8 предназначен для выбора источника записываемой информации в блок 4 - либо формирователя сигнатур 5, либо узла 35 блока 7 коммутации.

Устройство работает следующим образом.

При нажатии кнопки элемента 28 коммутации Нач.УСТ. производится присвоение начальных значений блока 4 и устанавливаются в требуемое состояние триггеры 32 управления двунаправленными элементами 33. При этом высокий .потенциал с выхода элемента НЕ 24 поступает на вход установки триггера 22, одновибратор 25, первый вход сброса триггера 15 и через элемент ИЛИ 18 на вход установки триггера 19. С выхода одновибратора 25 одиночный импульс поступает на восьмой выход блока синхронизации,а с него на пятый вход блока управления и входы сброса триггеров 32. Низкий потенциал с выходов триггеров 32 переводит двунаправленные элементы 33 в состояние приема информации.

Триггер 22 устанавливается в единичное состояние, и с его выхода вы- сокий потенциал через первый выход блока 3 синхронизации поступает на

вход управления мультиплексора 8,разрешая прохождение данных на информационные входы блока 4 с третьего выхода блока 7 управления.

Высокий потенциал с выхода триггера 19 поступает на вход управления генератора 20, разрешая его работу. Последовательность импульсов с выхода генератора 20 поступает на счетный вход счетчика 21, первые два выхода

которого управляют работой депшфрато- ра 12, формирующего импульсы синхронизации устройства. Остальные выходы счетчика 21 образуют адресную шину

10

устройства, которая управляет работой мультиплексора 2, блока 4, дешифратора 29 и узла 35. Адрес, выставленный счетчиком 21, выбирает необходимую ячейку ПЗУ, где в первом раз- ряде записано функдиональное назначение каждого контакта: О - выход, 1 - вход, а в остальных - начальное состояние, в которое необходимо установить блок 4. Импульсом синхронизации, поступающим с четвертого выхода блока управления, эта информация записывается в соответствующие триггер 32 и ячейку блока 4.

После того, как закончится перебор всех контактов проверяемого блока, импульс переполнения с выхода счетчика 21 устанавливает в нулевое состояние триггеры 15, 19 и 22. В данном состоянии устройство готово к проверке цифрового блока.

Рассмотрим работу устройства в режиме проверки цифрового блока.

После перевода кнопкой Пуск 27 триггера 23 в единичное состояние разрешается прохождение импульсов синхронизации генератора 16 через элемент И 17 на счетный вход счетчика 9 и через элемент ИЛИ 18 на вход установка триггера 19. При этом начинает работу генератор 20, управляющий опросом контактов проверяемого блока 1„ Если контакт, адрес которого определяется счетчиком 21,

записанное в регистся состояние, ре 31.

Мультиплексор 2 в этом случае закрыт сигналом, поступающим с третьего выхода блока 7 управления и на выходе мультиплексора устанавливается высокий потенциал, который также подается на вход формирователя 5 сигнатур. Считывание, сдвиг и запись нового состояния производятся аналогично рассмотренному выше случаю. Поскольку при формировании данной сигнатуры на вход формирователя 5

|с всегда подан высоюий потенциал, то данный регистр работает в режиме генератора. С последнего разряда формирователя 5 очередной бит подается на вход триггеров 30 и записывается в

2Q соответствующий триггер третьим импульсом синхронизации. После завершения опроса контактов цифрового блока импульс переполнения счетчика 21 сбрасывает триггер 19 и записывает

25 в регистр 31 очередной входной набор, сформированный на линейке триггеров 30. С приходом очередного импульса с генератора 16 цикл работы устройства повторяется.

До того, как на первом входе счетчика 9 появится высокий уровень и переключит триггер 11 в единичное состояние, мультиплексор 2 будет закрыт сигналом, поступающим с шестого выхода блока 3 синхронизации на вто30

40

45

является выходным, то соответствуюпщй 35 рой вход разрешения мультиплексора 2. триггер 32 находится в нулевом состоянии и двунаправленный элемент 33 работает в режиме приема информации. Логическое состояние передается че- рез двунаправленный элемент 33, мультиплексор 2 на вход формирователя 5 сигнатур. По первому импульсу синхронизации текущее состояние регистра, соответствующее данному контакту, переписывается из блока 4 в формирователь 5 сигнатур, по второму импульсу происходит сдвиг логического состояния контакта в формирователь 5 и формирование нь- 1ВОЙ сигнатуры. По третьему импульсу синхронизации производится запись новой сигнатуры на место старой в блок 4.

Если контакт, адрес которого выбран счетчиком 21, является выходным, то триггер 32 находится в единичном состоянии, элемент 33 - в режиме передачи сигнала и на контакт передаетЭтим обеспечивается задержка приема информации с проверяемого блока 1 до . того момента, как все его элементы памяти установятся в определенное состояние.После того, как будет подано необходимое число входных воздействий, высокий потенциал .с второго выхода счетчика 9 через элемент НЕ 10 закрывает элемейт И 18, проверка заканчивается.

При нажатии оператором кнопки Вывод 26 запускается одновибратор 14, который своим выходным импульсом устанавливает в единицу триггер 15 и через элемент ИЛИ 18 триггер 19, Высокий потенциал с прямого выхода триггера 15 поступает на вход управления частотой г енератора 20 тактовых импульсов, вызывая, снижение 55 его рабочей частоты. Низкий потенциал с инверсного выхода триггера 15 поступает на второй вход элемента И 13, запрещая выдачу третьего

50

0

записанное в регистся состояние, ре 31.

Мультиплексор 2 в этом случае закрыт сигналом, поступающим с третьего выхода блока 7 управления и на выходе мультиплексора устанавливается высокий потенциал, который также подается на вход формирователя 5 сигнатур. Считывание, сдвиг и запись нового состояния производятся аналогично рассмотренному выше случаю. Поскольку при формировании данной сигнатуры на вход формирователя 5

с всегда подан высоюий потенциал, то данный регистр работает в режиме генератора. С последнего разряда формирователя 5 очередной бит подается на вход триггеров 30 и записывается в

Q соответствующий триггер третьим импульсом синхронизации. После завершения опроса контактов цифрового блока импульс переполнения счетчика 21 сбрасывает триггер 19 и записывает

5 в регистр 31 очередной входной набор, сформированный на линейке триггеров 30. С приходом очередного импульса с генератора 16 цикл работы устройства повторяется.

До того, как на первом входе счетчика 9 появится высокий уровень и переключит триггер 11 в единичное состояние, мультиплексор 2 будет закрыт сигналом, поступающим с шестого выхода блока 3 синхронизации на вто0

рой вход разрешения мультиплексора 2.

Этим обеспечивается задержка приема информации с проверяемого блока 1 до . того момента, как все его элементы памяти установятся в определенное состояние.После того, как будет подано необходимое число входных воздействий, высокий потенциал .с второго выхода счетчика 9 через элемент НЕ 10 закрывает элемейт И 18, проверка заканчивается.

При нажатии оператором кнопки Вывод 26 запускается одновибратор 14, который своим выходным импульсом устанавливает в единицу триггер 15 и через элемент ИЛИ 18 триггер 19, Высокий потенциал с прямого выхода триггера 15 поступает на вход упавления частотой г енератора 20 тактовых импульсов, вызывая, снижение его рабочей частоты. Низкий потенциал с инверсного выхода триггера 15 поступает на второй вход элемена И 13, запрещая выдачу третьего

синхроимпульса, управляющего записью в блок 4. Счетчик 21 последовательно перебирает адреса блока 4, причем на каждом такте работы содержимое выбранной ячейки передается в блок 6 индикации. После окончания перебора всех адресов импульс переполнения с выхода счетчика 21 устанавливает в исходное состояние триггеры 15 и 19.

Предлагаемое устройство позволяет автономно, без дополнительных средств перекоммутации, вести проверку разнотипных цифровых блоков.

Формула изобретения .1, Устройство для контроля цифровых блоков, содержащее первый мультиплексор, блок синхронизации, блок оперативной памяти, формирователь сигнатур и блок индикации, причем группа адресньЕк входов мультиплексора соединена с группой адресных входов блока оперативной памяти и подключена к группе адресных выходов блока синхронизации, четвертый выход которого соединен с входом чтения- записи блока оперативной памяти, группа выходов которого соединена с группой информационных входов парал лельной записи формирователя сигнатур и группой входов блока индикации выход мультиплексора соединен с инфомационным входом формирователя сигнатур, входы записи и сдвига KOTopioro соединены с третьим и вторым выходами блока сиихронизации отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет контроля логических схем с произвольным числом входов и выходов, оно содержит блок управления, второй мультиплексор, , адресный вход которого подключен к первому выходу блока синхронизации, группа выходов которого соединена с группой адресных входов блока управления, вход сброса и тактовый вход которого подключены к седьмому и шестому выходам блока синхронизации, пятый выход которого соединен с пер- Bbw входом разрешения первого мультиплексора, второй вход разрешения которого подключен к выходу задания режима блока управления, вход записи которого подключен к четвертому выходу блока синхронизации, группа информационных выходов формирователя сигнатур соединена с первой группой ин

формационных входов второго мультиплексора, вторая г.руппа информационных входов которого подключена к группе выходов начальньк значений блока управления, группа информационных выходов которого соединена с группой информационных входов первого мультиплексора, информационный вход блока управления соединен с выходом последнего разряда формирователя сигнатур, группа выходов второго мультиплексора соединена с группой информационных входов блока оперативной памяти, группа информационных входов-выходов блока управления образует группу информационных входов-выходов устройства, блок управления содержит дешифратор, две группы 1)-триггеров, регистр, узел задания адресов, узел постоянной памяти и группу приемопередатчиков, причем группа адресных входов блока соединена с группой информационных входов дешифратора и первой группой адресных входов узла постоянной памяти, вторая группа адресных входов узла постоянной памяти соединена с группой выходов узла задания адресов, вход записи блока соединен со стробирующим входом дешифратора, выходы которого соединены с тактовыми входами соответствующих D-триггеров первой и второй групп, информационные входы D-триггеров первой группы объединены и подключены к йнформа- Щ1ОННОМУ входу блока, выходы D-триггеров первой группы соединены с соответствующими информационными входами регистра, тактовый вход которого является тактовым входом блока, первый выход узла постоянной памяти соединен с- информационньми входами D-триггеров второй группы и является управляющим выходом 6jjoKa, вход сброса которого соединен с входами сброса D-триггеров второй группы, выходы которых соединены с входами выбора направления, передачи приемопередатчиков группы, входы которых подключены к выходам регистра, группа выходов узла постоянной памяти подключена к группе выходов начальных значений блока, группа информационных выходов которого соединена с. выходами приемопередатчиков группы, входы-выходы которьк подключены к rpyqne информационных входов-Bbtxo- дов блока.

fo .3lo

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1987-09-08—Подача